JAJSIM5A November 2020 – June 2022 DLP670S

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 Storage Conditions

- 6.3 ESD Ratings

- 6.4 Recommended Operating Conditions

- 6.5 Thermal Information

- 6.6 Electrical Characteristics

- 6.7 Capacitance at Recommended Operating Conditions

- 6.8 Timing Requirements

- 6.9 Typical Characteristics

- 6.10 System Mounting Interface Loads

- 6.11 Micromirror Array Physical Characteristics

- 6.12 Micromirror Array Optical Characteristics

- 6.13 Window Characteristics

- 6.14 Chipset Component Usage Specification

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

3 概要

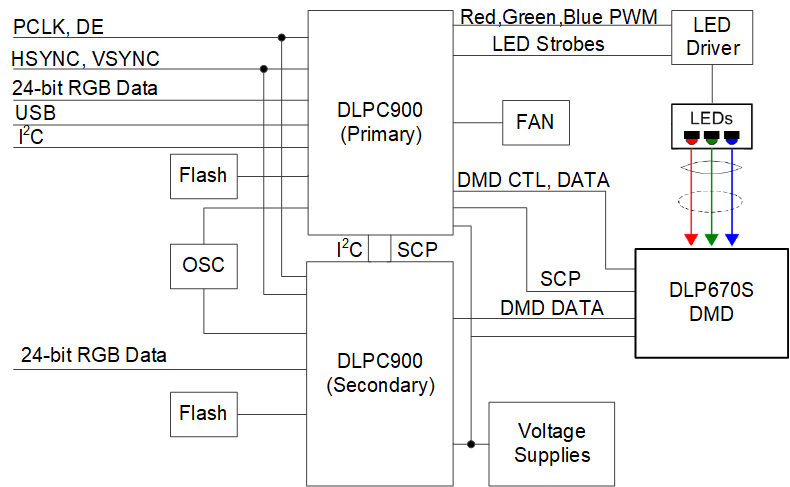

430 万個を超えるマイクロミラーを搭載した DLP670S デジタル・マイクロミラー・デバイス (DMD) は、入射光の振幅、方向、位相を変調する空間光変調器 (SLM) です。この DMD は、4 つの 2xLVDS 入力データ・バスとの組み合わせにより、非常に高速なパターン・レートで高分解能パターンを表示できます。DLP670S は高分解能で高速なパターン・レートを実現しており、産業用、医療用、および高度な画像処理アプリケーションを幅広くサポートするのに最適です。DLP670S の機能と動作の高い信頼性 は、デュアル DLPC900 デジタル・コントローラと組み合わせることで実現されます。この専用チップセットは、さまざまな最終製品ソリューションの要件を満たすのに必要な高いパターン・レートで、柔軟でプログラムしやすいパターンを提供します。

高分解能は、3Dマシン・ビジョン・アプリケーションで大型の物体をスキャンする際に直接的な利点があります。

DLP670S を使用して設計を開始する方法については、TI の DLP® 高度光制御テクノロジーのページをご覧ください。TI.com で利用できる DLP 高度光制御のリソースには、評価基板、リファレンス・デザイン、光学モジュール・メーカー、DLP デザイン・ネットワーク・パートナーなどが含まれており、製品開発期間の短縮に役立ちます。

表 3-1 製品情報

| 部品番号 | パッケージ | 本体サイズ (公称) |

|---|---|---|

| DLP670S(1) | FYR (350) | 35mm × 32mm |

(1) 利用可能なパッケージについては、このデータシートの末尾にある注文情報を参照してください。

DLP670S の概略回路図

DLP670S の概略回路図