JAJST20A March 2024 – September 2024 DLPC964

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Pin Configuration and Functions

- 5 Specifications

-

6 Detailed Description

- 6.1 Overview

- 6.2 Functional Block Diagram

- 6.3 Feature Description

- 6.4

Device Functional

Modes

- 6.4.1 DLPC964 Aurora 64B/66B Input Data and Command Write Cycle

- 6.4.2 DMD Row Operation

- 6.4.3 Block Load Address Select

- 6.4.4 Block Mode Select

- 6.4.5 Mirror Clocking Pulse (MCP)

- 6.5

Register Map

- 6.5.1

Register Table Overview

- 6.5.1.1 FPGA_INTERRUPT_STATUS Register

- 6.5.1.2 FPGA_INTERRUPT_ENABLE_CONTROL Register

- 6.5.1.3 FPGA_MAIN_STATUS Register

- 6.5.1.4 FPGA_VERSION Register

- 6.5.1.5 FPGA_MAIN_CTRL Register

- 6.5.1.6 SELF_TEST_REG Register

- 6.5.1.7 DMDIF_ERROR_STATUS_CLR Register

- 6.5.1.8 DMDIF_ERROR_STATUS Register

- 6.5.1.9 PRBS7_MACRO0_TEST_RESULT Register

- 6.5.1.10 PRBS7_MACRO1_TEST_RESULT Register

- 6.5.1.11 PRBS7_MACRO2_TEST_RESULT Register

- 6.5.1.12 PRBS7_MACRO3_TEST_RESULT Register

- 6.5.1.13 PRBS7_TEST_CONTROL Register

- 6.5.1.14 PRBS7_TEST_RUNSTATUS Register

- 6.5.1.15 LS_BUS_TEST_RESULT Register

- 6.5.1.16 DMD_TYPE Register

- 6.5.1.17 HSS_RESET Register

- 6.5.1.18 HSS_CHANNEL_STATUS Register

- 6.5.1.19 HSS_LANE_STATUS Register

- 6.5.1.20 HSS_CH0_SOFTERROR_COUNT Register

- 6.5.1.21 HSS_CH1_SOFTERROR_COUNT Register

- 6.5.1.22 HSS_CH2_SOFTERROR_COUNT Register

- 6.5.1.23 HSS_CH3_SOFTERROR_COUNT Register

- 6.5.1.24 HSS_SOFTERROR_COUNT_RESET Register

- 6.5.1.25 HSSI_Channel_0_DMD_Data_GT_Cell_Control Register

- 6.5.1.26 HSSI_Channel_0_DMD_Clock_GT_Cell_Control Register

- 6.5.1.27 HSSI_Channel_1_DMD_Data_GT_Cell_Control Register

- 6.5.1.28 HSSI_Channel_1_DMD_Clock_GT_Cell_Control Register

- 6.5.1.29 HSSI_Channel_2_DMD_Data_GT_Cell_Control Register

- 6.5.1.30 HSSI_Channel_2_DMD_Clock_GT_Cell_Control Register

- 6.5.1.31 HSSI_Channel_3_DMD_Data_GT_Cell_Control Register

- 6.5.1.32 HSSI_Channel_3_DMD_Clock_GT_Cell_Control Register

- 6.5.1.33 HSSI_DMD_Vcm_Value Register

- 6.5.1.34 TEST_DMD_ID Register

- 6.5.1.35 TEST_DMD_FUSE1 Register

- 6.5.1.36 TEST_DMD_FUSE2 Register

- 6.5.1.37 TEST_DMD_FUSE3 Register

- 6.5.1.38 TEST_DMD_FUSE4 Register

- 6.5.1

Register Table Overview

-

7 Application and Implementation

- 7.1 Application Information

- 7.2 Typical Application

- 7.3 Interfacing to DLPC964 Controller High Speed Serial (HSS) Aurora 64B/66B Inputs

- 7.4 Power Supply Recommendations

- 7.5 Layout

- 7.6 Layout Example

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- ZUM|1156

サーマルパッド・メカニカル・データ

発注情報

7.6 Layout Example

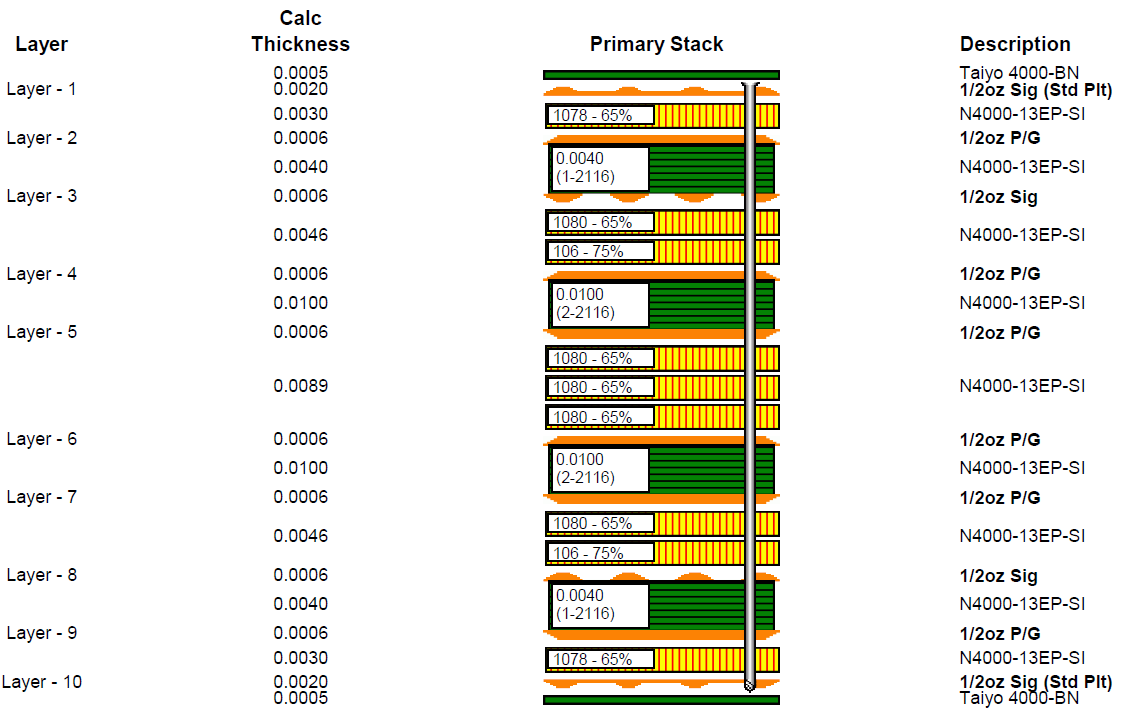

The PCB layer design may vary depending on the system design. However, careful attention is required to meet design considerations. Table 7-13 shows a layer definition table and Figure 7-14 shows a PCB stack-up. The PCB stack-up uses Nelco N4000-13-SI as the dielectric material to improve the signal slew rate for better performance of the Aurora 64B/66B input interface and the HSSI DMD output interface.

Table 7-13 Layer Definition

| LAYER | DESCRIPTION |

|---|---|

| Top | Top components. Low frequency signals routing, ground, voltage mini-planes |

| 2 | Ground |

| 3 | High speed signal layer |

| 4 | Ground |

| 5 | Split power plane |

| 6 | Split power plane |

| 7 | Ground |

| 8 | High speed signal layer |

| 9 | Ground |

| Bottom | Discrete components. Low frequency signals routing, ground, voltage mini-planes |

Figure 7-14 PCB Stack-Up.

Figure 7-14 PCB Stack-Up.