JAJSJR7B August 2022 – October 2023 DRV8462

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 ピン構成および機能

- 6 仕様

-

7 詳細説明

- 7.1 概要

- 7.2 機能ブロック図

- 7.3

機能説明

- 7.3.1 動作インターフェイス

- 7.3.2 ステッパ・モーター・ドライバの電流定格

- 7.3.3 PWM モーター・ドライバ

- 7.3.4 マイクロステッピング・インデクサ

- 7.3.5 インデクサ出力

- 7.3.6 自動マイクロステッピング・モード

- 7.3.7 カスタム・マイクロステッピング表

- 7.3.8 電流レギュレーション

- 7.3.9 内部リファレンス電圧

- 7.3.10 静止電力節約モード

- 7.3.11 電流レギュレーション減衰モード

- 7.3.12 外付け抵抗による電流検出

- 7.3.13 サイレント・ステップ減衰モード

- 7.3.14 自動トルクの動的電流調整

- 7.3.15 チャージ・ポンプ

- 7.3.16 リニア電圧レギュレータ

- 7.3.17 VCC 電圧電源

- 7.3.18 ロジック・レベル、トライレベル、クワッドレベルのピン構造図

- 7.3.19 スペクトラム拡散

- 7.3.20 保護回路

- 7.3.21 デバイスの機能モード

- 7.4 プログラミング

- 7.5

レジスタ・マップ

- 7.5.1 ステータス・レジスタ

- 7.5.2

制御レジスタ

- 7.5.2.1 CTRL1 (アドレス = 0x04) [デフォルト = 0Fh]

- 7.5.2.2 CTRL2 (アドレス=0x05) [デフォルト=06h]

- 7.5.2.3 CTRL3 (アドレス=0x06) [デフォルト=38h]

- 7.5.2.4 CTRL4 (アドレス=0x07) [デフォルト=49h]

- 7.5.2.5 CTRL5 (アドレス=0x08) [デフォルト=03h]

- 7.5.2.6 CTRL6 (アドレス=0x09) [デフォルト=20h]

- 7.5.2.7 CTRL7 (アドレス=0x0A) [デフォルト=FFh]

- 7.5.2.8 CTRL8 (アドレス=0x0B) [デフォルト=0Fh]

- 7.5.2.9 CTRL9 (アドレス=0x0C) [デフォルト=10h]

- 7.5.2.10 CTRL10 (アドレス=0x0D) [デフォルト=80h]

- 7.5.2.11 CTRL11 (アドレス=0x0E) [デフォルト=FFh]

- 7.5.2.12 CTRL12 (アドレス=0x0F) [デフォルト=20h]

- 7.5.2.13 CTRL13 (アドレス=0x10) [デフォルト=10h]

- 7.5.2.14 CTRL14 (アドレス = 0x3C) [デフォルト = 58h]

- 7.5.3 インデクサ・レジスタ

- 7.5.4

カスタム・マイクロステッピング・レジスタ

- 7.5.4.1 CUSTOM_CTRL1 (アドレス=0x16) [デフォルト=00h]

- 7.5.4.2 CUSTOM_CTRL2 (アドレス=0x17) [デフォルト=00h]

- 7.5.4.3 CUSTOM_CTRL3 (アドレス=0x18) [デフォルト=00h]

- 7.5.4.4 CUSTOM_CTRL4 (アドレス=0x19) [デフォルト=00h]

- 7.5.4.5 CUSTOM_CTRL5 (アドレス=0x1A) [デフォルト=00h]

- 7.5.4.6 CUSTOM_CTRL6 (アドレス=0x1B) [デフォルト=00h]

- 7.5.4.7 CUSTOM_CTRL7 (アドレス=0x1C) [デフォルト=00h]

- 7.5.4.8 CUSTOM_CTRL8 (アドレス=0x1D) [デフォルト=00h]

- 7.5.4.9 CUSTOM_CTRL9 (アドレス=0x1E) [デフォルト=00h]

- 7.5.5

自動トルク・レジスタ

- 7.5.5.1 ATQ_CTRL1 (アドレス=0x1F) [デフォルト=00h]

- 7.5.5.2 ATQ_CTRL2 (アドレス=0x20) [デフォルト=00h]

- 7.5.5.3 ATQ_CTRL3 (アドレス=0x21) [デフォルト=00h]

- 7.5.5.4 ATQ_CTRL4 (アドレス=0x22) [デフォルト=20h]

- 7.5.5.5 ATQ_CTRL5 (アドレス=0x23) [デフォルト=00h]

- 7.5.5.6 ATQ_CTRL6 (アドレス=0x24) [デフォルト=00h]

- 7.5.5.7 ATQ_CTRL7 (アドレス=0x25) [デフォルト=00h]

- 7.5.5.8 ATQ_CTRL8 (アドレス=0x26) [デフォルト=00h]

- 7.5.5.9 ATQ_CTRL9 (アドレス=0x27) [デフォルト=00h]

- 7.5.5.10 ATQ_CTRL10 (アドレス=0x28) [デフォルト=08h]

- 7.5.5.11 ATQ_CTRL11 (アドレス=0x29) [デフォルト=0Ah]

- 7.5.5.12 ATQ_CTRL12 (アドレス=0x2A) [デフォルト=FFh]

- 7.5.5.13 ATQ_CTRL13 (アドレス=0x2B) [デフォルト=05h]

- 7.5.5.14 ATQ_CTRL14 (アドレス=0x2C) [デフォルト=0Fh]

- 7.5.5.15 ATQ_CTRL15 (アドレス=0x2D) [デフォルト=00h]

- 7.5.5.16 ATQ_CTRL16 (アドレス=0x2E) [デフォルト=FFh]

- 7.5.5.17 ATQ_CTRL17 (アドレス=0x2F) [デフォルト=00h]

- 7.5.5.18 ATQ_CTRL18 (アドレス=0x30) [デフォルト=00h]

- 7.5.6 サイレント・ステップ・レジスタ

- 8 アプリケーションと実装

- 9 熱に関する注意事項

- 10電源に関する推奨事項

- 11レイアウト

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

- DDW|44

発注情報

7.3.20.6 開放負荷検出 (OL)

開放負荷フォルトは、次の場合に検出されます。

モーターが動作している場合:

コイル電流が開放負荷電流スレッショルド (IOL) を下回った場合

モーターがホールド状態の場合:

コイル電流がインデクサで設定された ITRIP レベルを下回った場合

上記のいずれかの条件が、開放負荷検出時間 (tOL) を超えて持続する場合

デバイスが SPI インターフェイスで動作している場合、開放負荷検出をイネーブルにするには EN_OL ビットを 1b にする必要があります。

開放負荷検出時間 (tOL) は、表 7-28 のように設定されます。

|

インターフェイス |

OL_T |

tOL (ms) の最大値 |

|---|---|---|

ハードウェア・インターフェイス | 該当なし | 60 |

SPI インターフェイス | 00b | 30 |

01b (デフォルト) | 60 | |

10b | 120 |

開放負荷フォルトが検出されると、次の動作が行われます。

nFAULT が Low にプルされます。

デバイスが SPI インターフェイスで動作している場合、次の動作が行われます。

OL ビットと FAULT ビットは 1b にラッチされます

OL_A ビットが 1b の場合、AOUT1 と AOUT2 の間の巻線 A の開放負荷フォルトを示します。

BOUT1 と BOUT2 の間の開放負荷フォルトによって、OL_B ビットが 1b になります。

開放負荷条件が解消されると、デバイスがハードウェア・インターフェイスと SPI インターフェイスのどちらで構成されているかによって動作は異なります。

デバイスがハードウェア・インターフェイスで構成されており、開放負荷条件が解消された場合:

ENABLE ピンがロジック High の場合、nFAULT はただちに解放されます。

ENABLE ピンがハイ・インピーダンスの場合、nSLEEP リセット・パルスが印加されると nFAULT は解放されます。

デバイスが SPI インターフェイスで構成されており、開放負荷条件が解消された場合:

OL_MODE ビットが 1b の場合、nFAULT はただちに解放されます。FAULT レジスタの OL ビットと DIAG2 レジスタの OL_X ビットは、CLR_FLT ビットまたは nSLEEP リセット・パルスのいずれかによって障害クリア・コマンドが発行された後でのみクリアされます。

OL_MODE ビットが 0b の場合、CLR_FLT ビットまたは nSLEEP リセット・パルスのどちらかによって障害クリア・コマンドが発行された後、nFAULT ビットと障害ビットは解放されます。

本デバイスの電源を切って再投入した後、またはスリープ・モードから復帰した後にも、開放負荷フォルトはクリアされます。

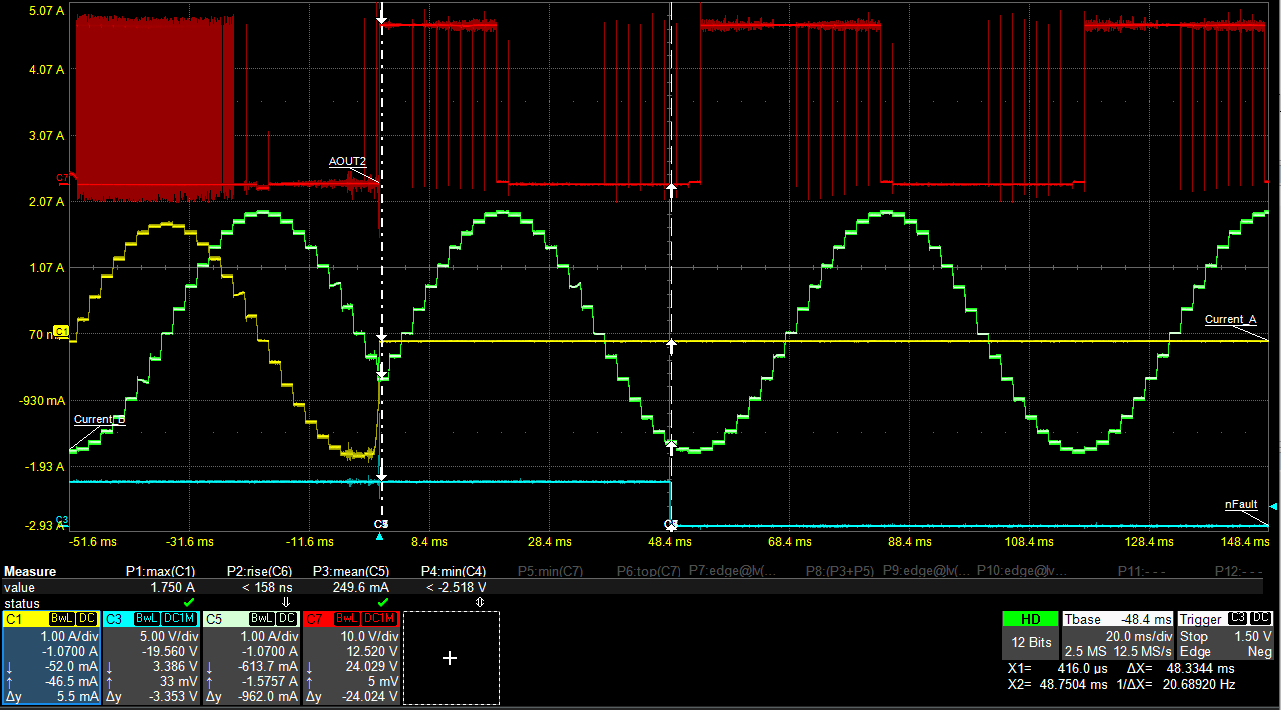

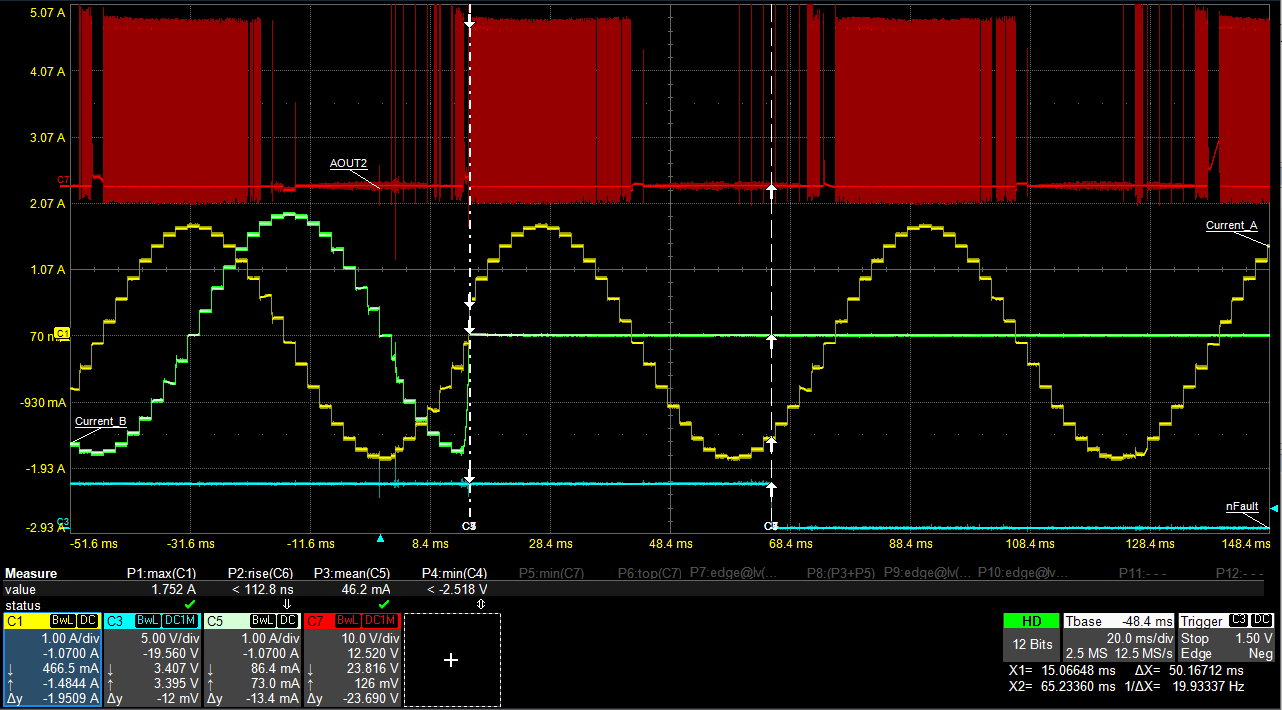

図 7-45 および図 7-46 に、コイル A とコイル B がそれぞれ開いている場合の開放負荷検出を示します。開放負荷検出時間は最大 60ms に選択され、OL_MODE ビットは 0b でした。

図 7-45 コイル A の開放負荷検出. 上から下へのパターン:AOUT2、コイル A 電流、コイル B 電流、nFAULT

図 7-45 コイル A の開放負荷検出. 上から下へのパターン:AOUT2、コイル A 電流、コイル B 電流、nFAULT 図 7-46 コイル B の開放負荷検出. 上から下へのパターン:AOUT2、コイル A 電流、コイル B 電流、nFAULT

図 7-46 コイル B の開放負荷検出. 上から下へのパターン:AOUT2、コイル A 電流、コイル B 電流、nFAULTサイレント・ステップ減衰モードでは、モーターが動作している場合のみ開放負荷障害検出が動作します。モーターが静止状態の場合、開放負荷検出はサポートされません。

開放負荷フォルトは、次の場合に検出されます。

ENABLE ピンをロジック High からハイ・インピーダンスにすぐに変更する場合は、開放負荷条件が解消されたらすぐに nSLEEP リセット・パルスを印加します。

OL_MODE を 1b から 0b に変更した場合、または EN_OL を 1b から 0b に変更した場合は、開放負荷条件が解消されたらすぐに障害クリア・コマンドを適用します。

デバイスの自動トルクがイネーブルで動作しているとき、開放負荷フォルトが検出されると、コイル電流は TRQ_DAC に対応する値になります。