JAJSP52C September 2022 – December 2022 ESD1LIN24-Q1 , ESD751-Q1 , ESD761-Q1

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings—AEC Specification

- 6.3 ESD Ratings—IEC Specification

- 6.4 ESD Ratings - ISO Specification

- 6.5 Recommended Operating Conditions

- 6.6 Thermal Information

- 6.7 Electrical Characteristics

- 6.8 Typical Characteristics – ESD751

- 6.9 Typical Characteristics – ESD1LIN24

- 6.10 Typical Characteristics - ESD761

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

6.9 Typical Characteristics – ESD1LIN24

Figure 6-7 Positive TLP Curve

Figure 6-7 Positive TLP Curve Figure 6-9 +8-kV

Clamped IEC Waveform

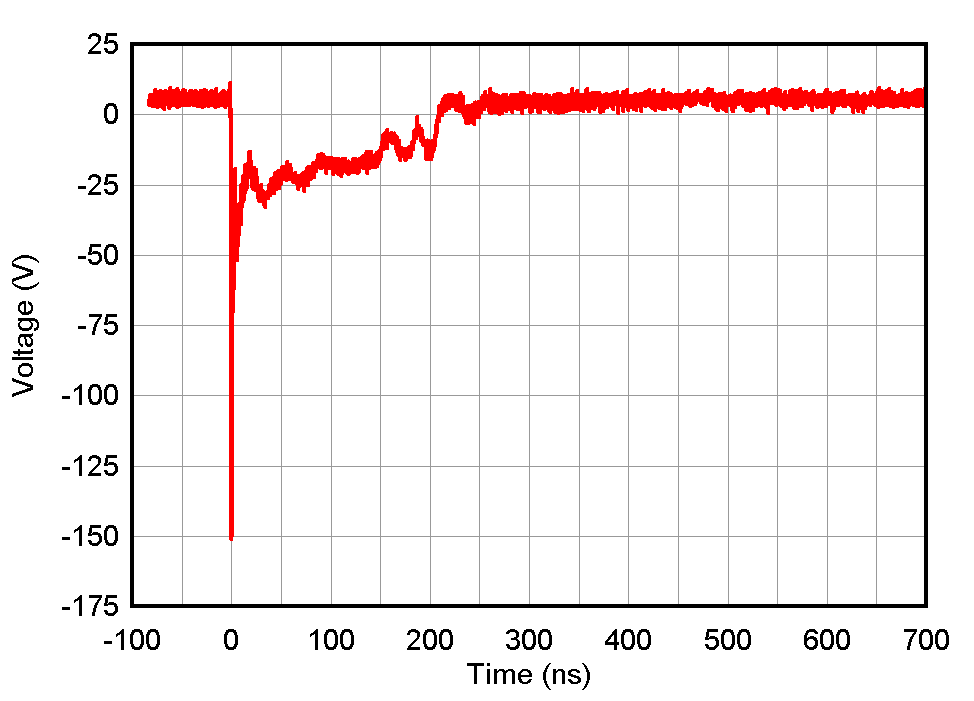

Figure 6-9 +8-kV

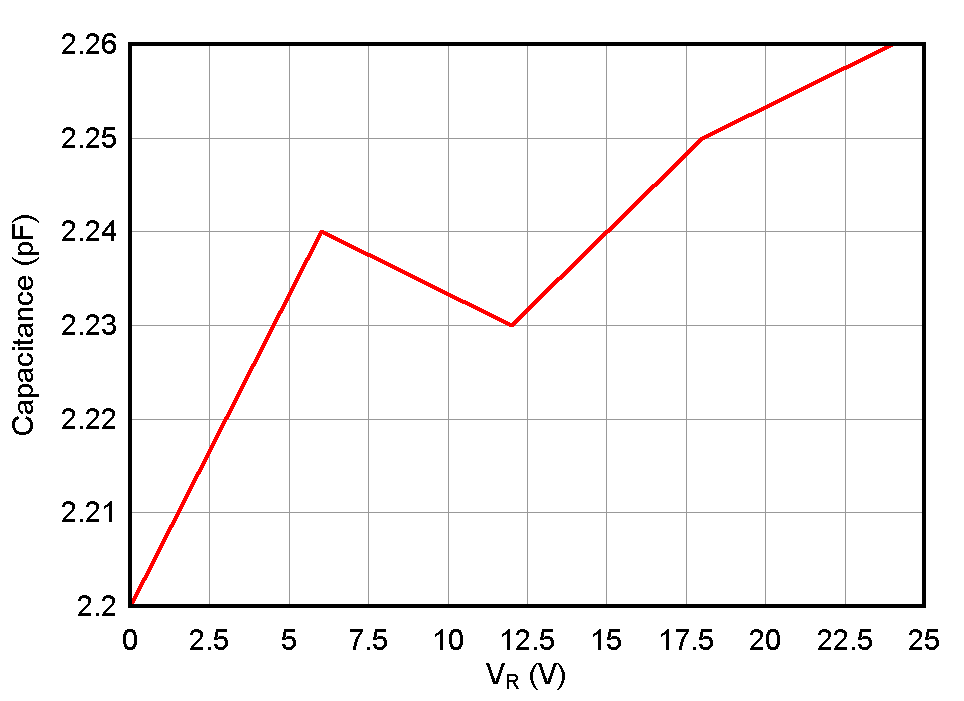

Clamped IEC Waveform Figure 6-11 Capacitance vs. Bias Voltage

Figure 6-11 Capacitance vs. Bias Voltage Figure 6-8 Negative TLP Curve

Figure 6-8 Negative TLP Curve Figure 6-10 −8-kV

Clamped IEC Waveform

Figure 6-10 −8-kV

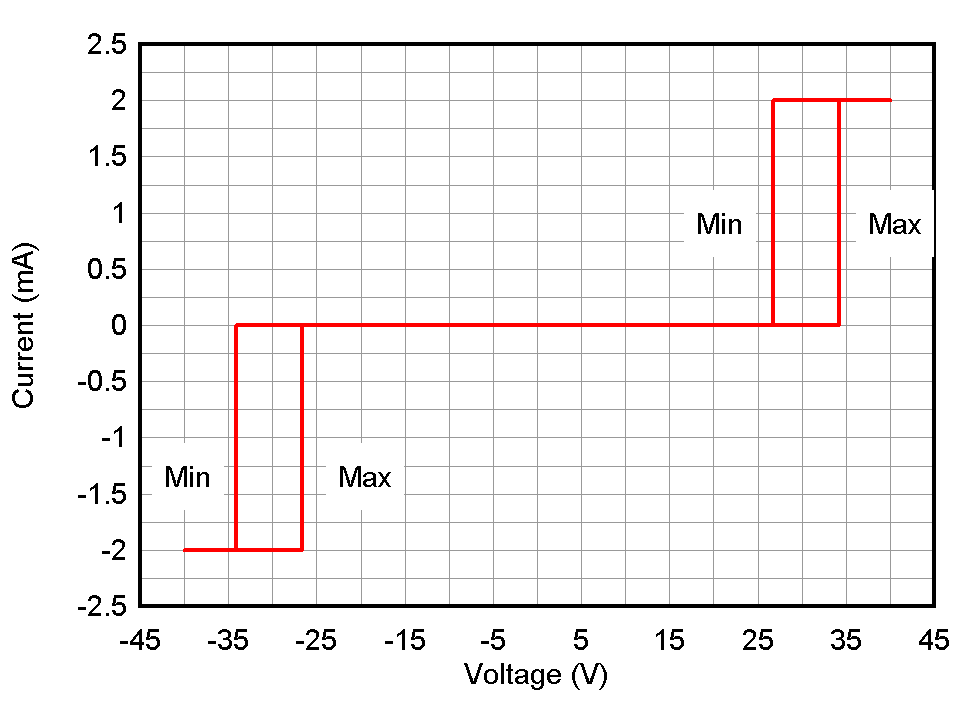

Clamped IEC Waveform Figure 6-12 DC

Voltage Sweep I-V Curve

Figure 6-12 DC

Voltage Sweep I-V Curve