JAJSB70C July 2000 – October 2018 LF198-N , LF298 , LF398-N

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 概要(続き)

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 Recommended Operating Conditions

- 7.3 Thermal Information

- 7.4 Electrical Characteristics, LF198-N and LF298

- 7.5 Electrical Characteristics, LF198A-N

- 7.6 Electrical Characteristics, LF398-N

- 7.7 Electrical Characteristics, LF398A-N (OBSOLETE)

- 7.8 Typical Characteristics

- 8 Parameter Measurement Information

- 9 Detailed Description

-

10Application and Implementation

- 10.1 Application Information

- 10.2

Typical Applications

- 10.2.1 X1000 Sample and Hold

- 10.2.2 Sample and Difference Circuit

- 10.2.3 Ramp Generator With Variable Reset Level

- 10.2.4 Integrator With Programmable Reset Level

- 10.2.5 Output Holds at Average of Sampled Input

- 10.2.6 Increased Slew Current

- 10.2.7 Reset Stabilized Amplifier

- 10.2.8 Fast Acquisition, Low Droop Sample and Hold

- 10.2.9 Synchronous Correlator for Recovering Signals Below Noise Level

- 10.2.10 2-Channel Switch

- 10.2.11 DC and AC Zeroing

- 10.2.12 Staircase Generator

- 10.2.13 Differential Hold

- 10.2.14 Capacitor Hysteresis Compensation

- 11Power Supply Recommendations

- 12Layout

- 13デバイスおよびドキュメントのサポート

- 14メカニカル、パッケージ、および注文情報

7.8 Typical Characteristics

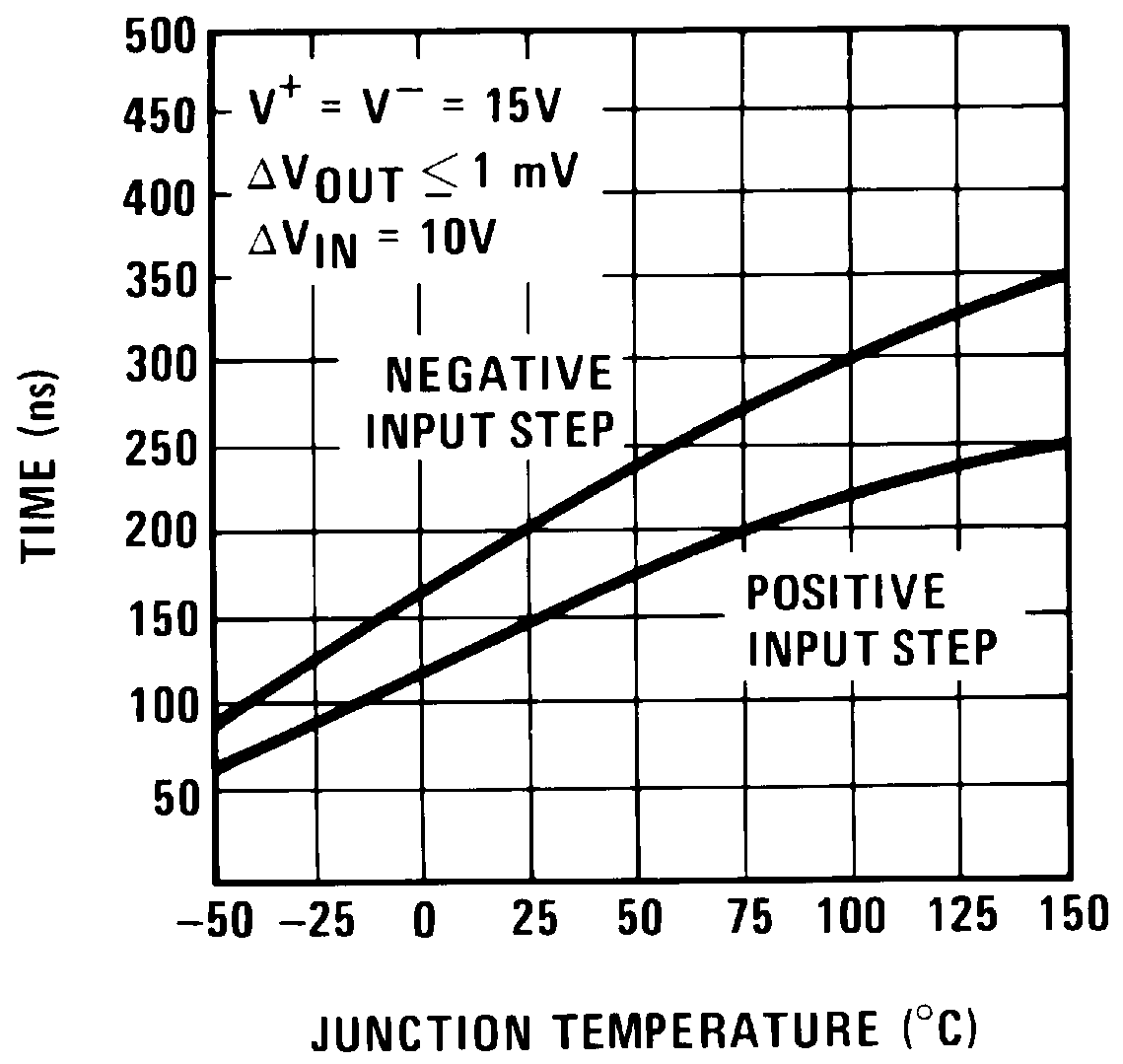

Figure 1. Aperture Time

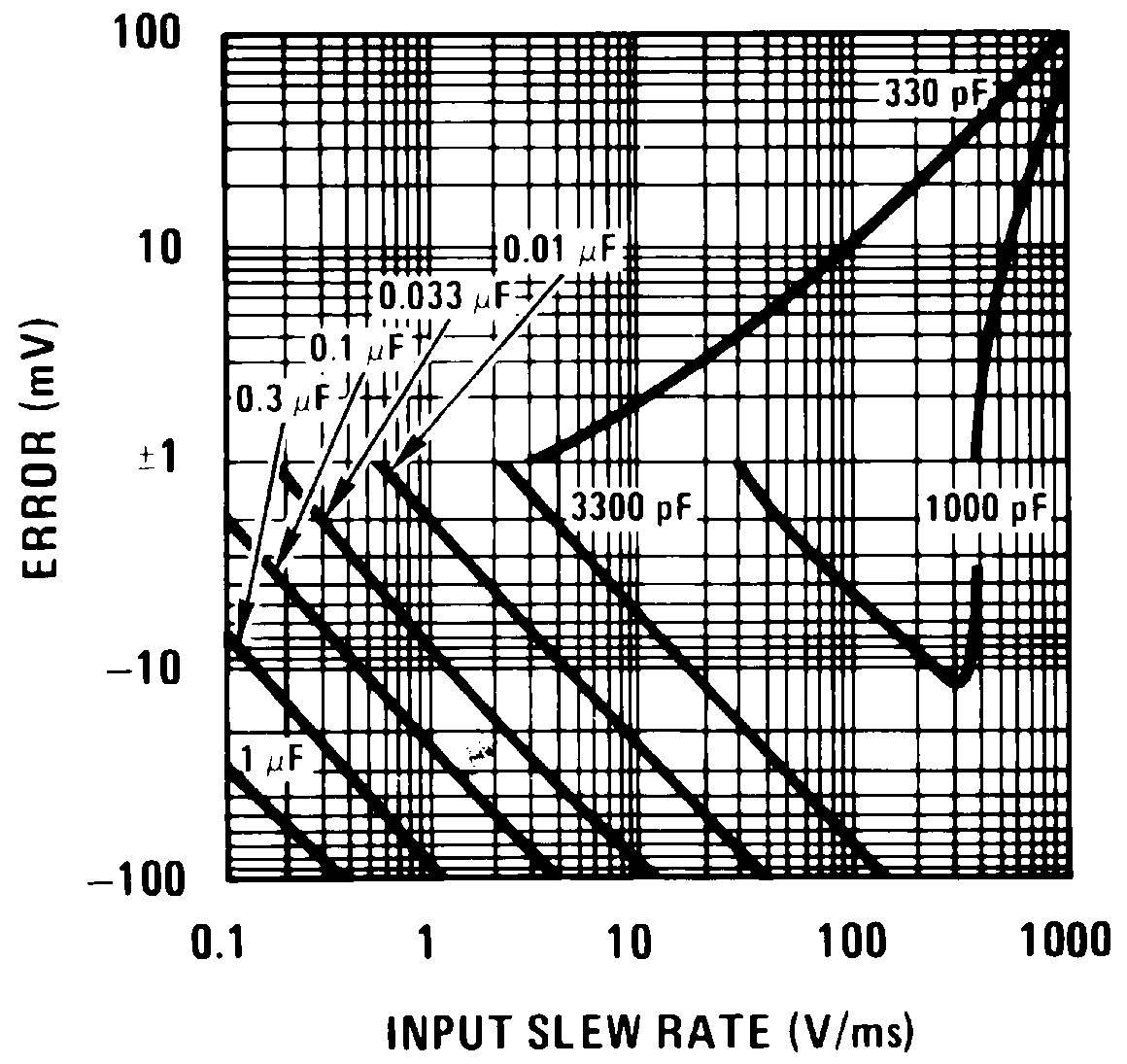

Figure 1. Aperture Time  Figure 3. Dynamic Sampling Error

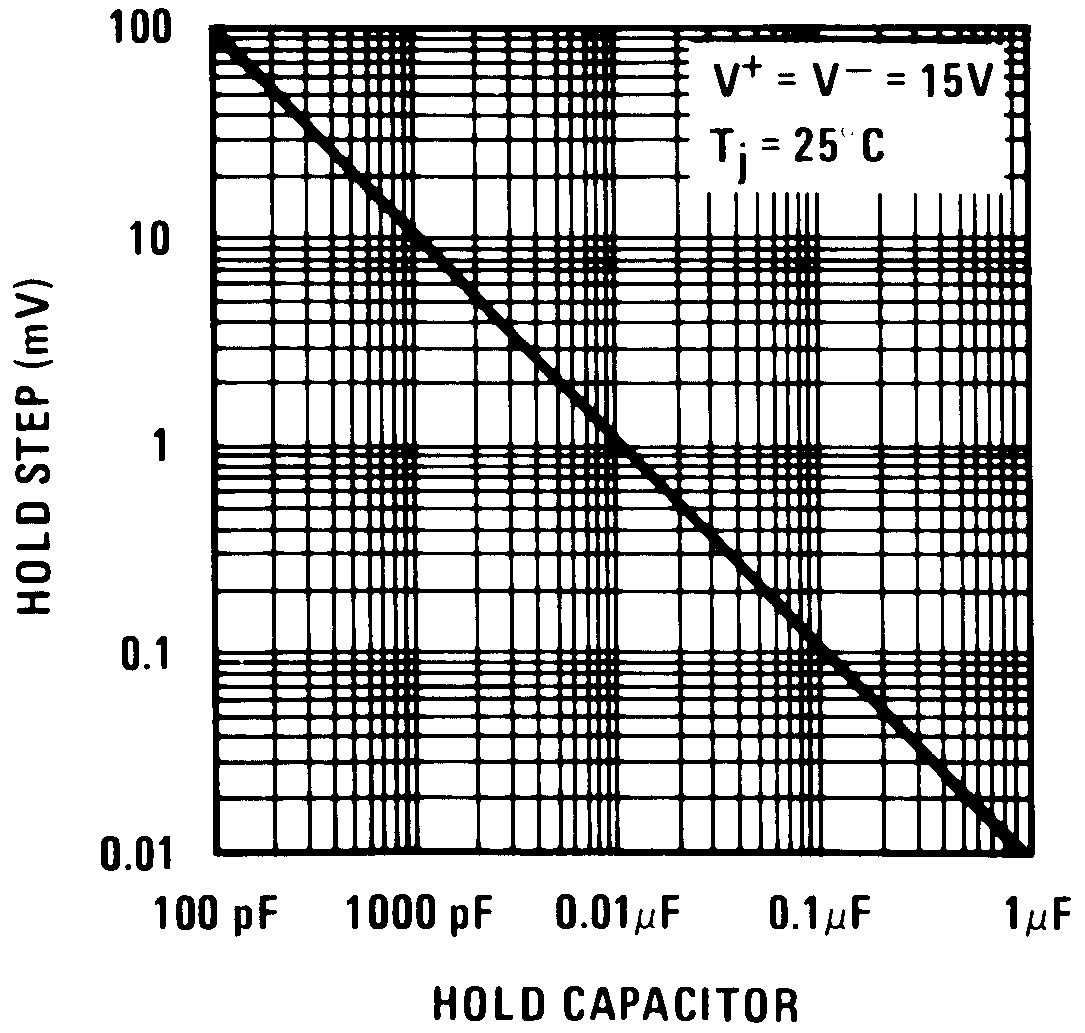

Figure 3. Dynamic Sampling Error  Figure 5. Hold Step

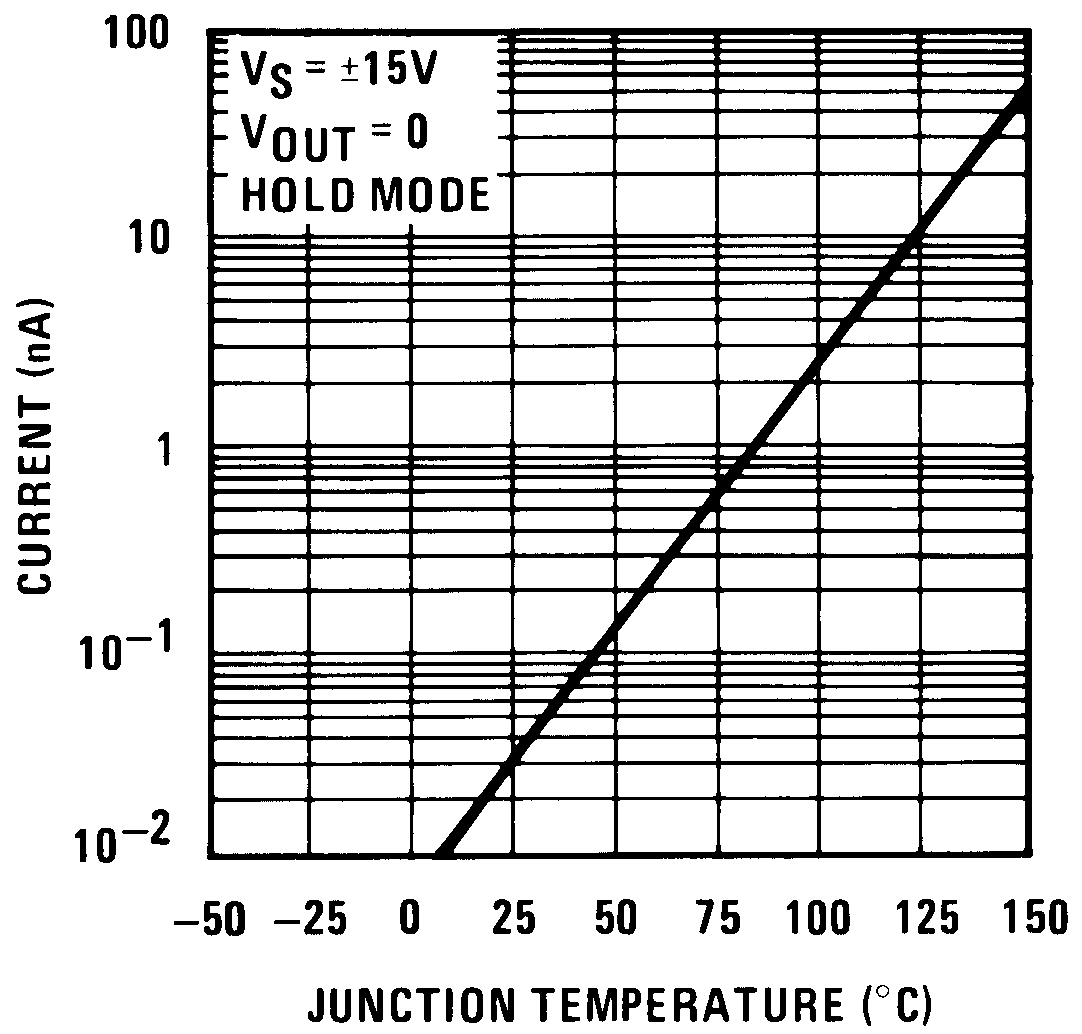

Figure 5. Hold Step  Figure 7. Leakage Current into Hold Capacitor

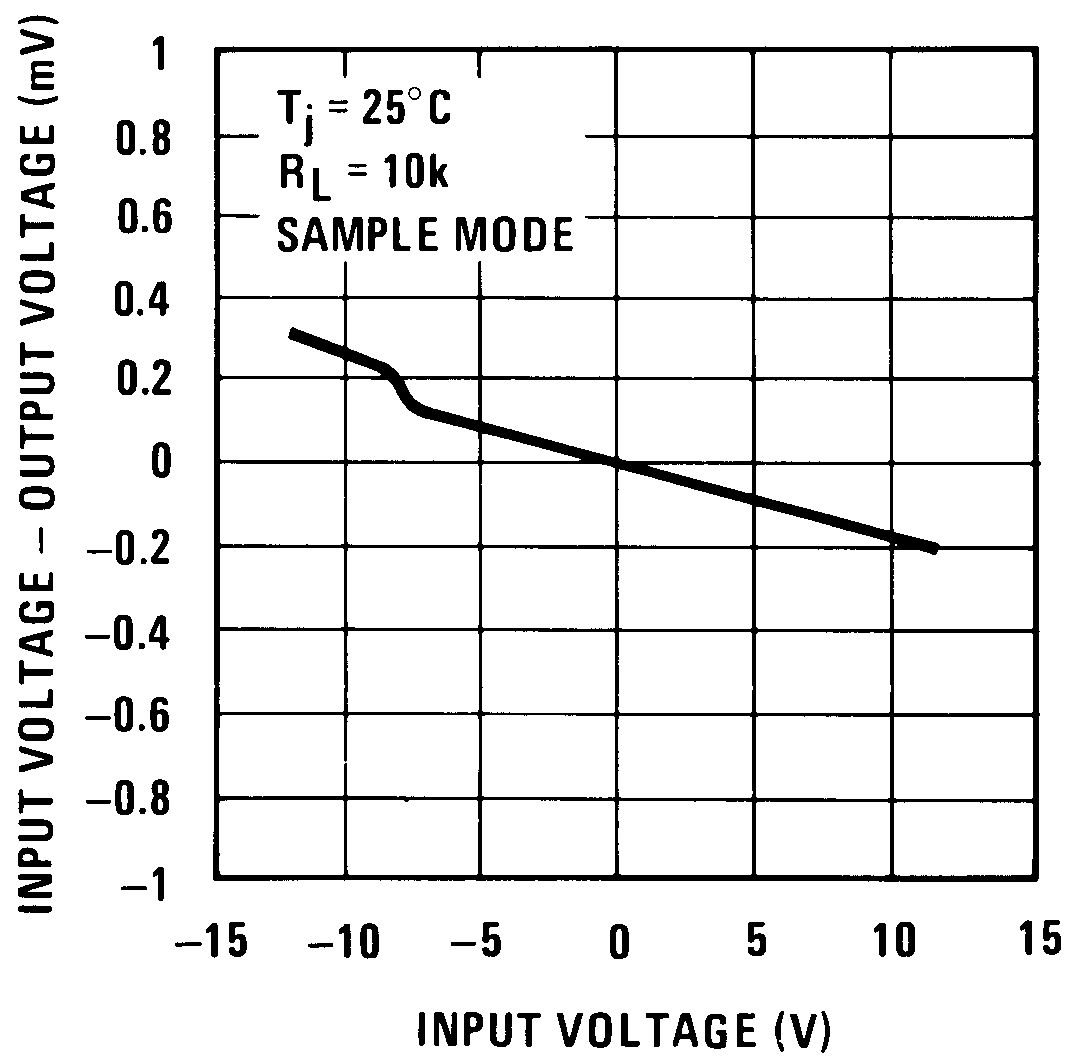

Figure 7. Leakage Current into Hold Capacitor  Figure 9. Gain Error

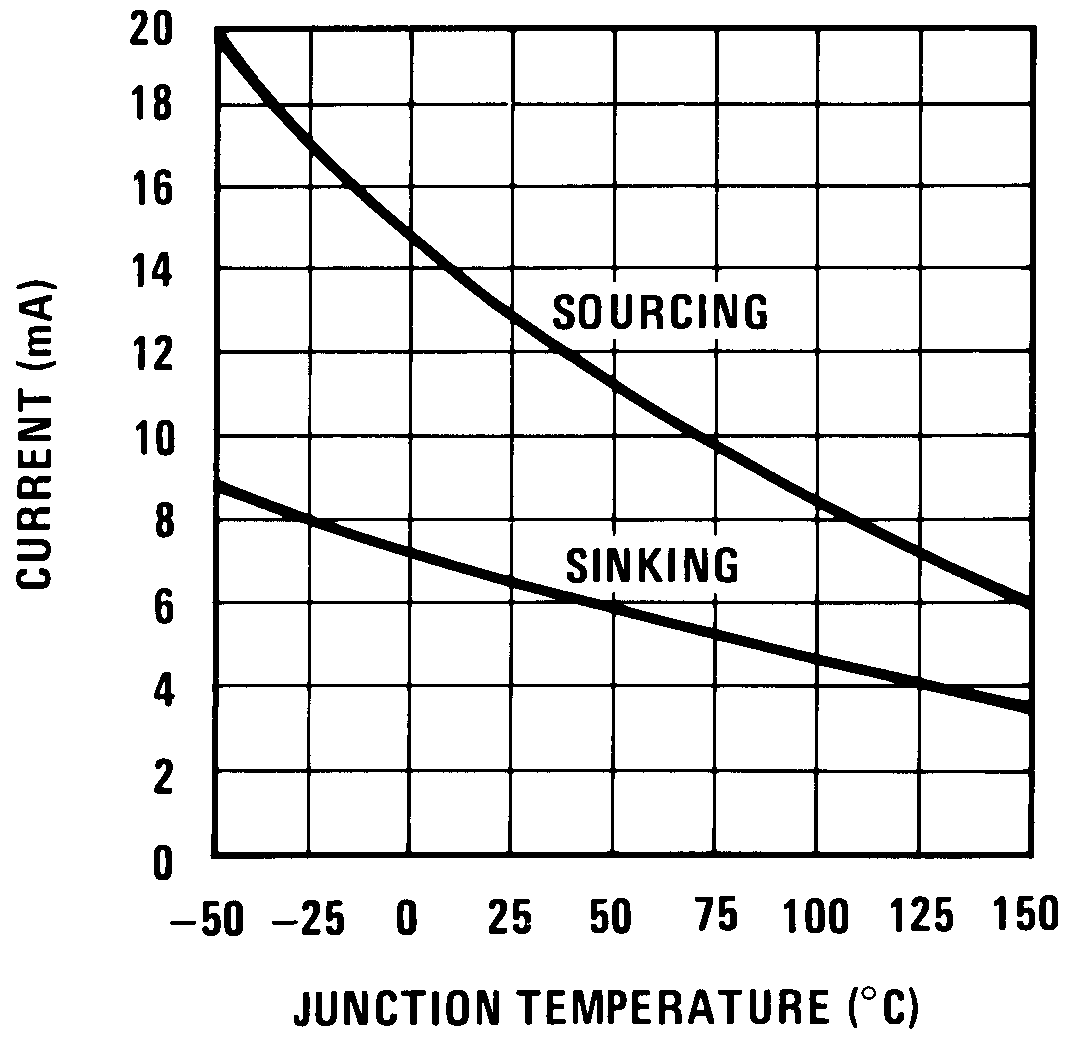

Figure 9. Gain Error  Figure 11. Output Short Circuit Current

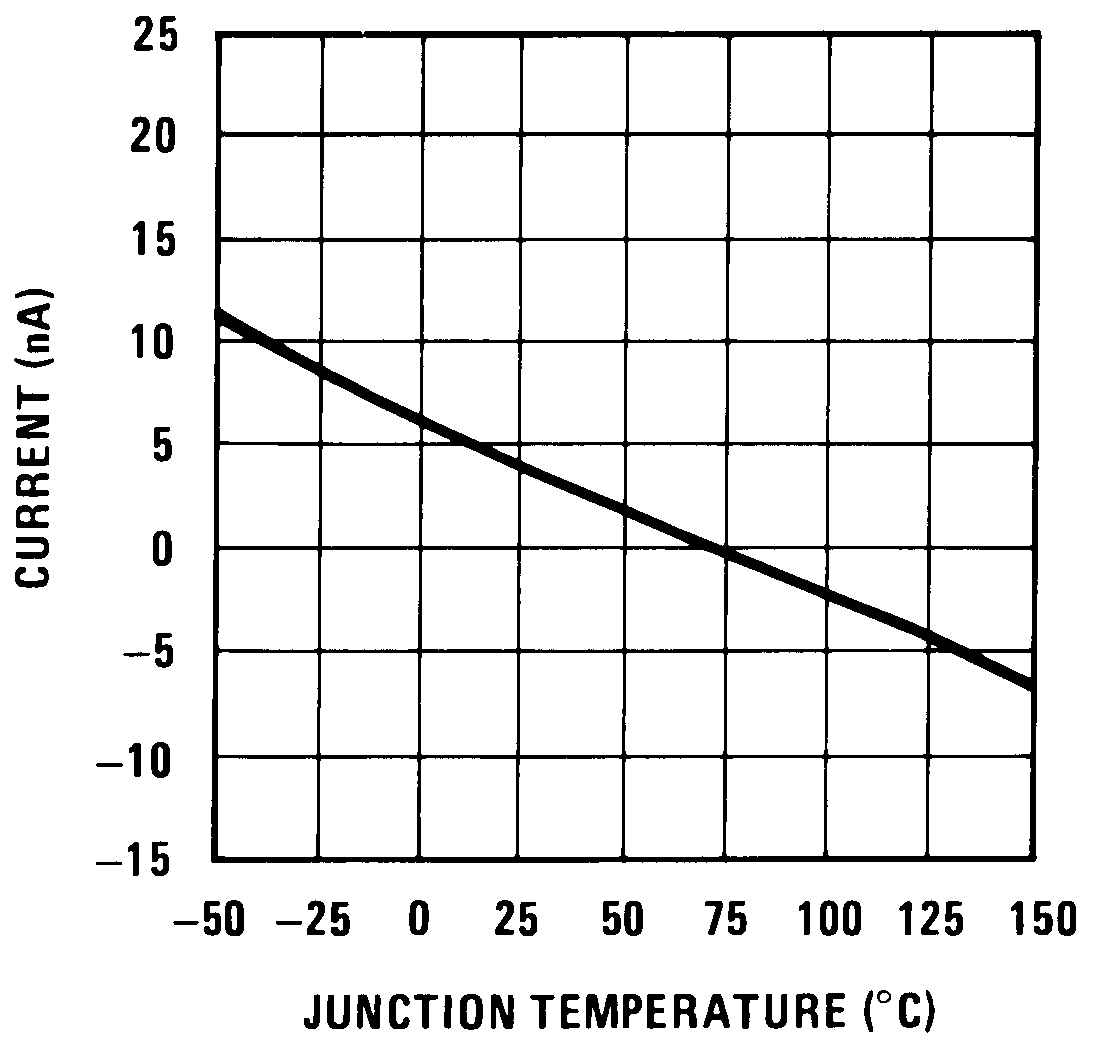

Figure 11. Output Short Circuit Current  Figure 13. Input Bias Current

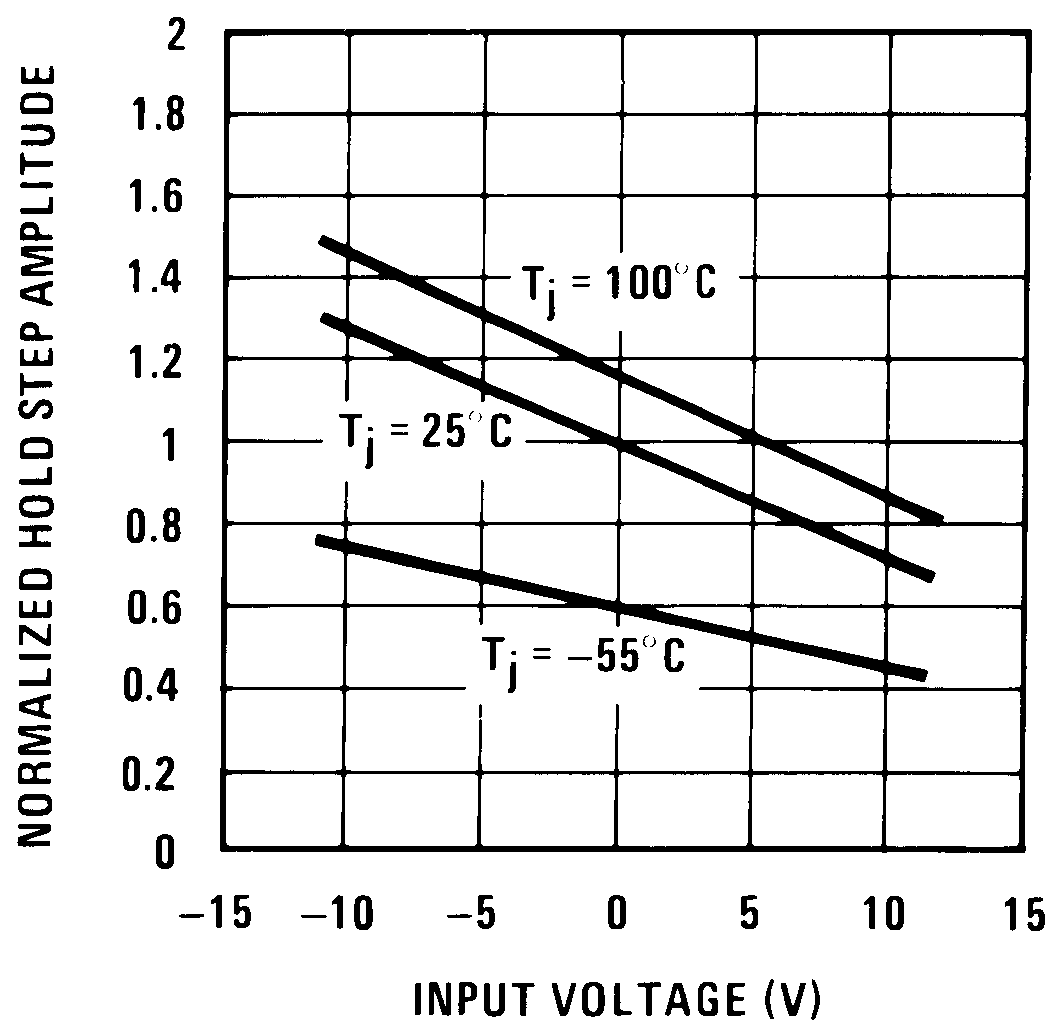

Figure 13. Input Bias Current  Figure 15. Hold Step vs Input Voltage

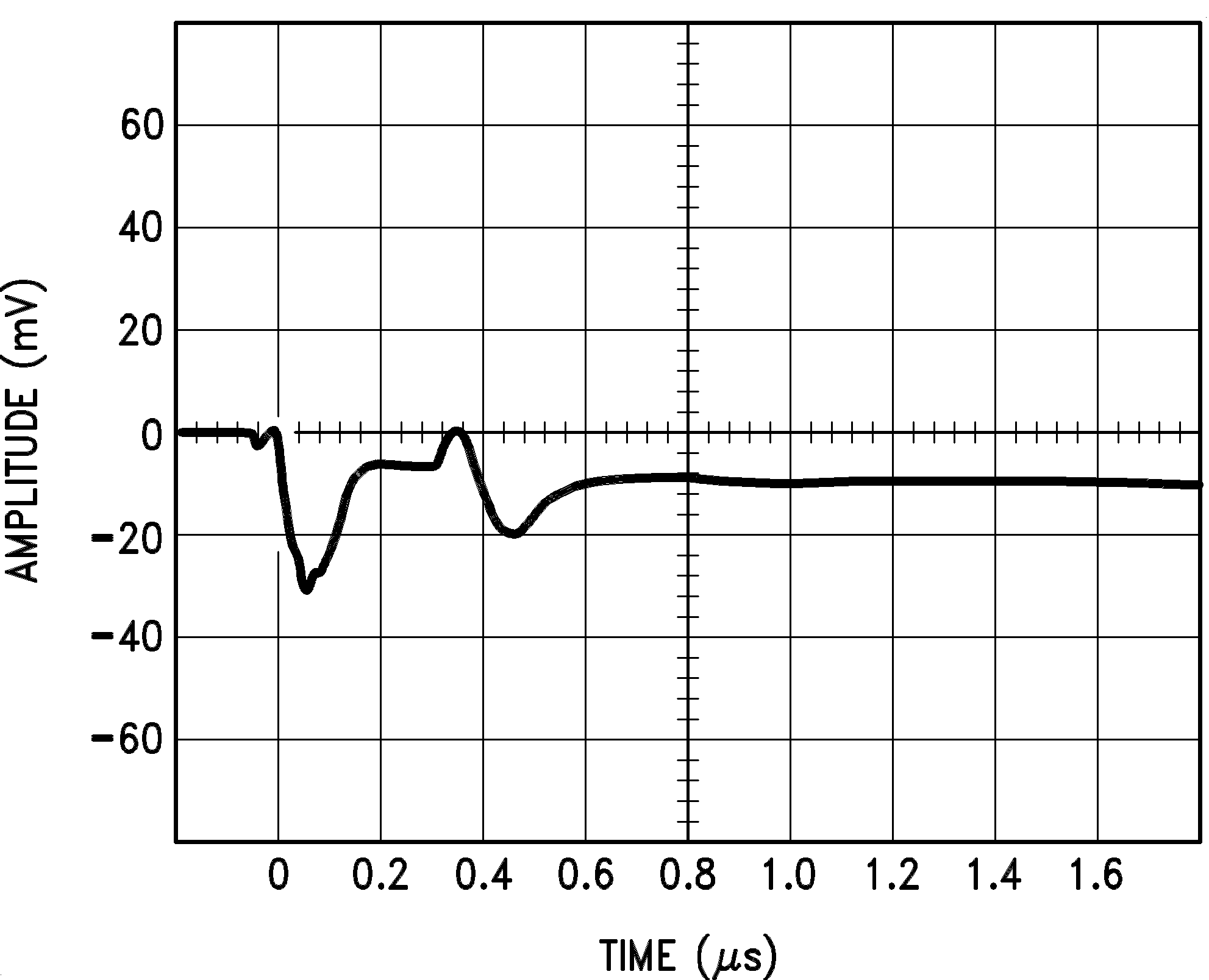

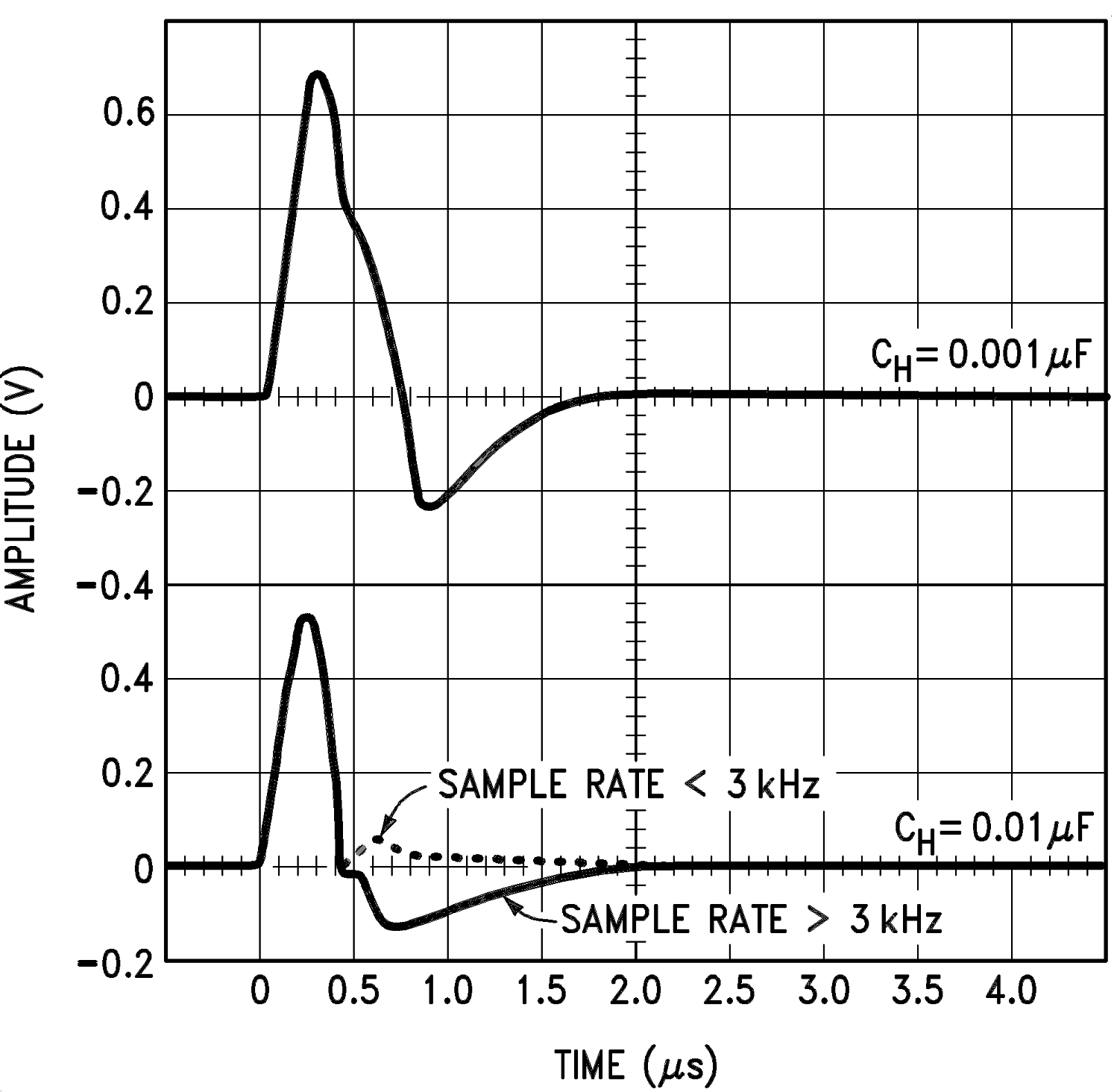

Figure 15. Hold Step vs Input Voltage  Figure 17. Output Transient at Start of Hold Mode

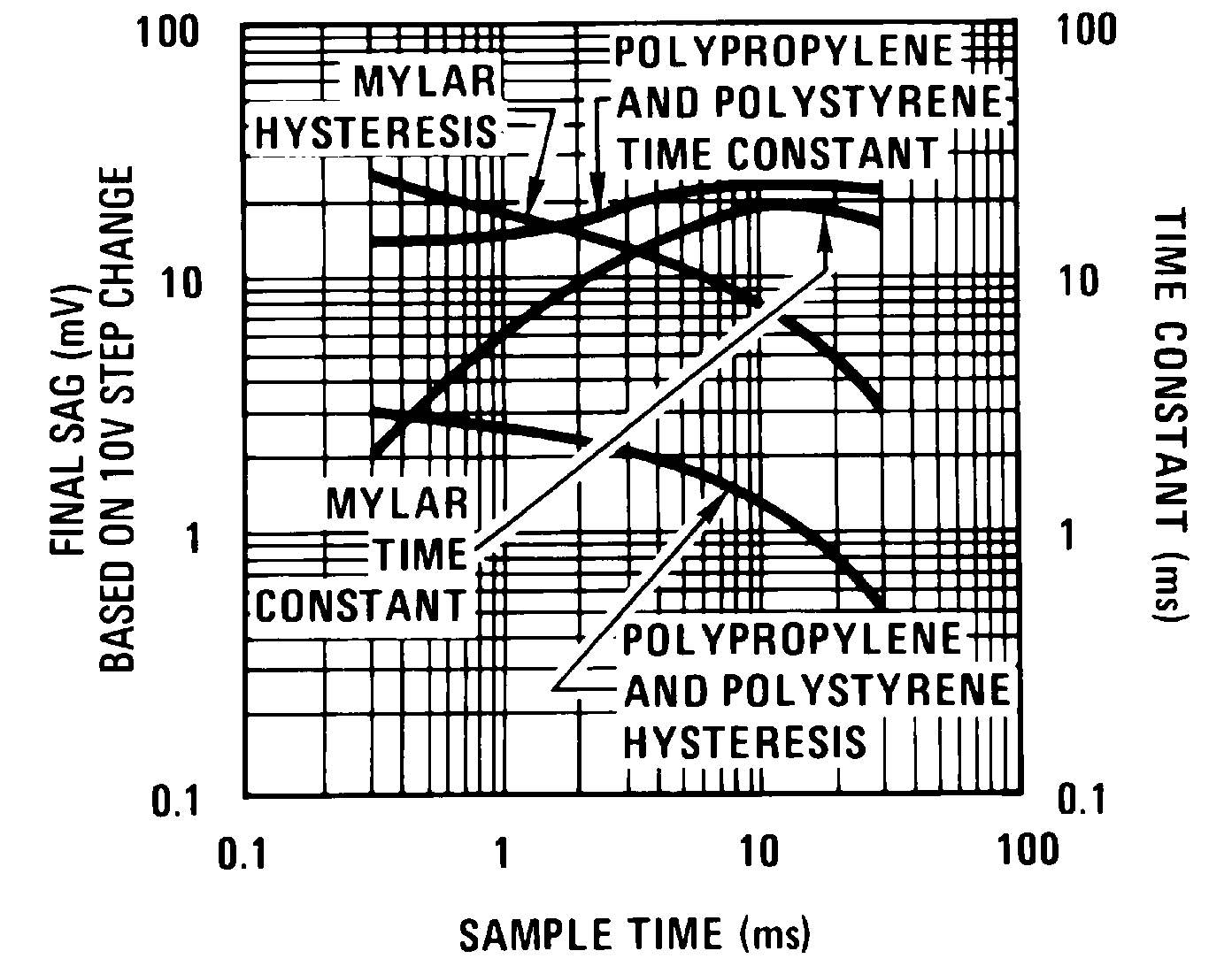

Figure 17. Output Transient at Start of Hold Mode  Figure 2. Dielectric Absorption Error in Hold Capacitor

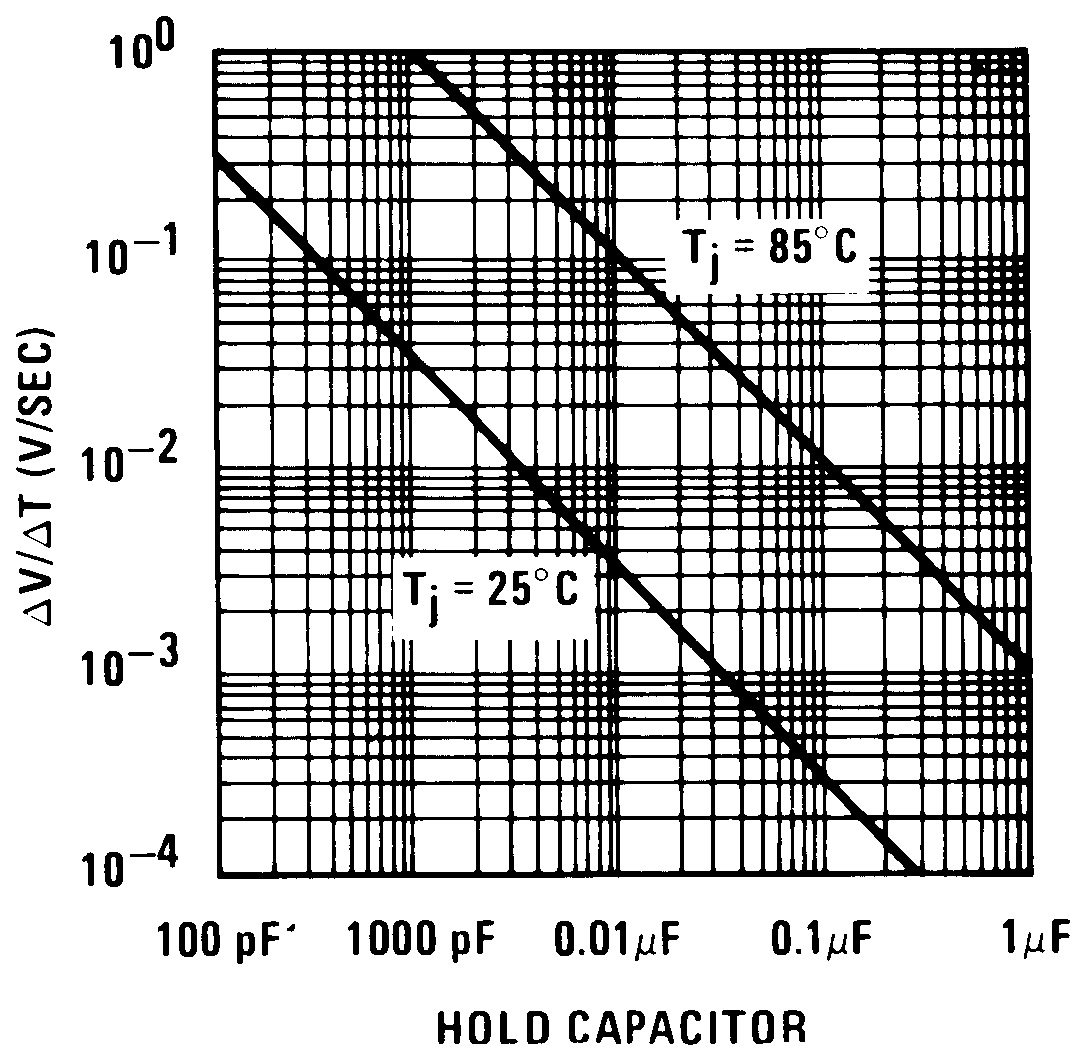

Figure 2. Dielectric Absorption Error in Hold Capacitor  Figure 4. Output Droop Rate

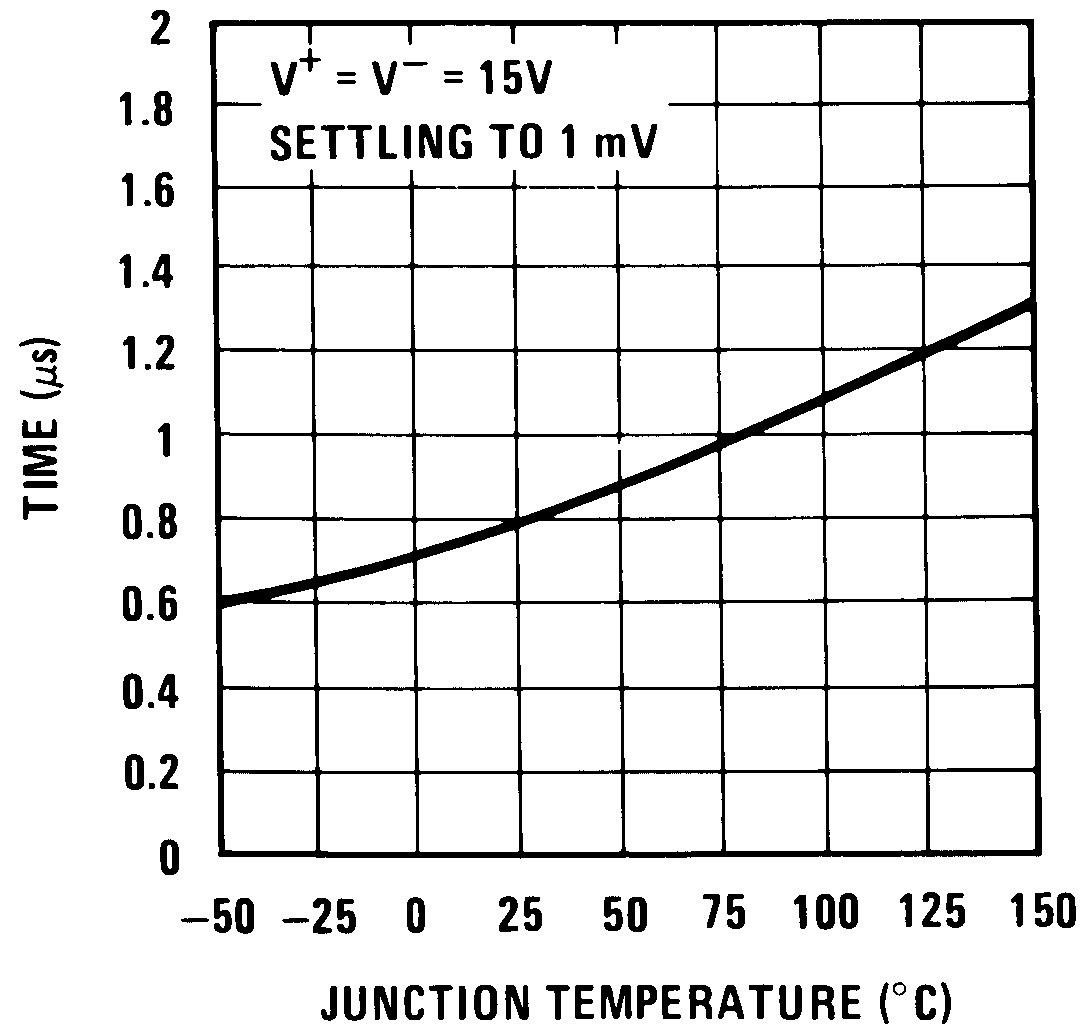

Figure 4. Output Droop Rate  Figure 6. Hold Settling Time

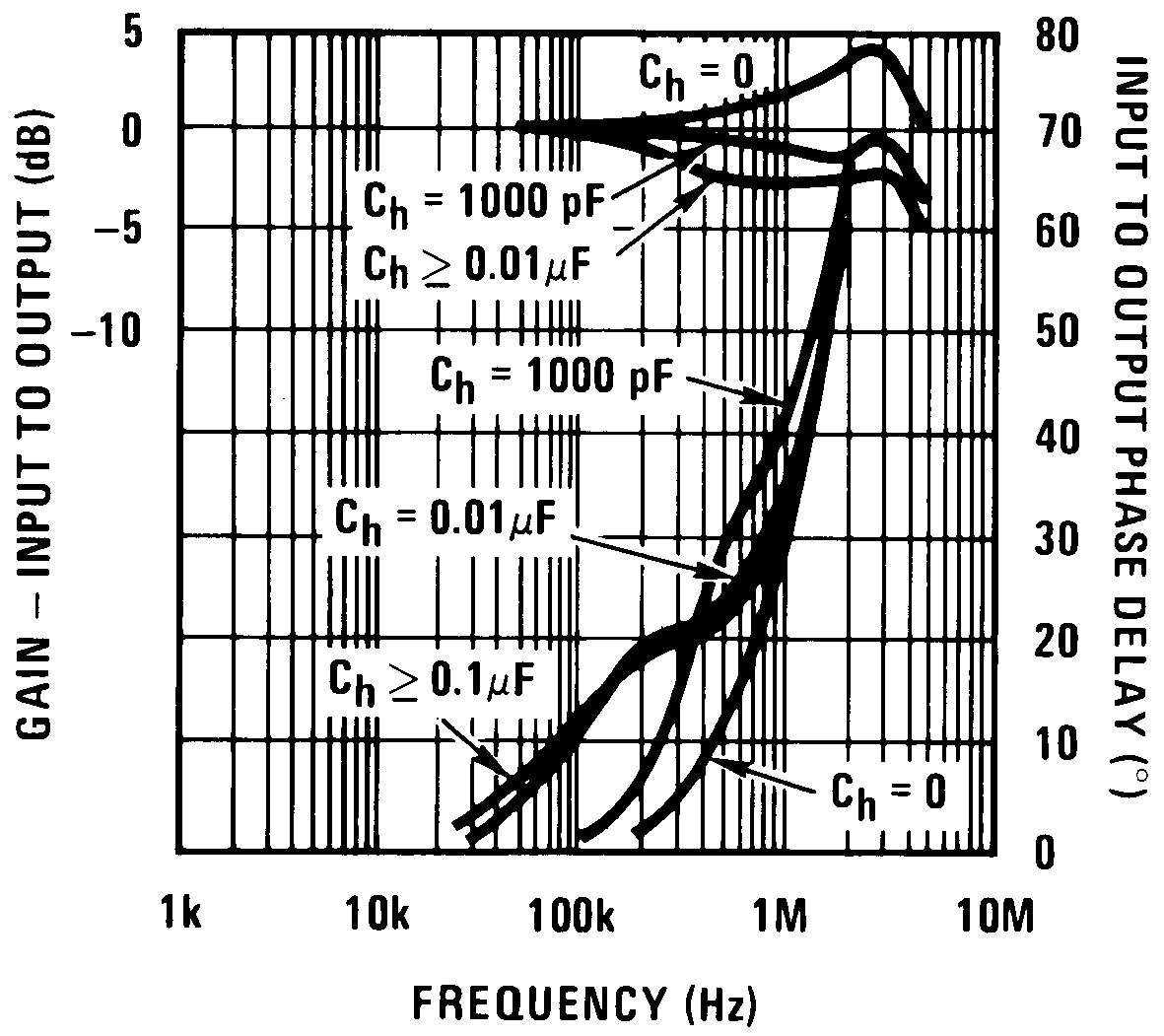

Figure 6. Hold Settling Time  Figure 8. Phase and Gain (Input to Output, Small Signal)

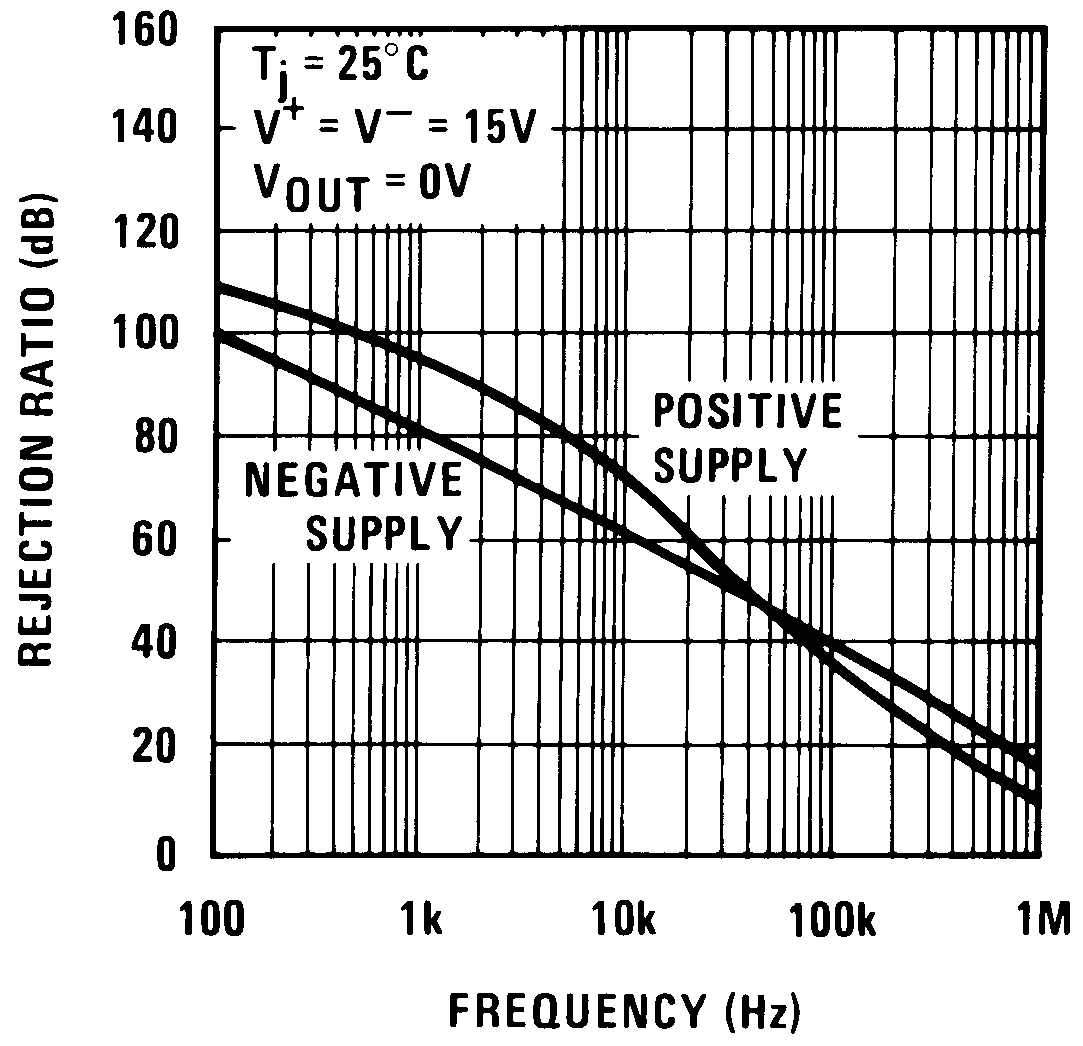

Figure 8. Phase and Gain (Input to Output, Small Signal)  Figure 10. Power Supply Rejection

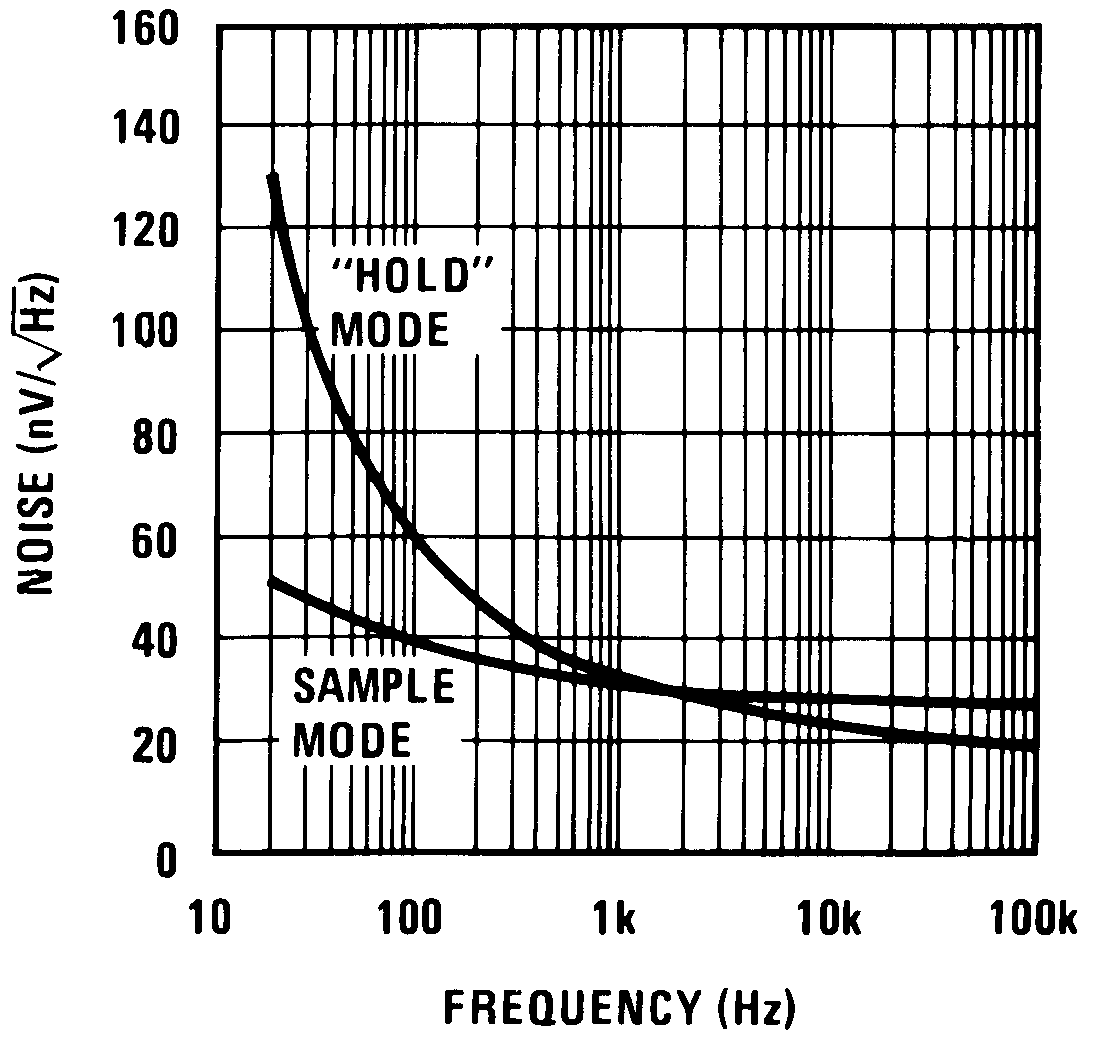

Figure 10. Power Supply Rejection  Figure 12. Output Noise

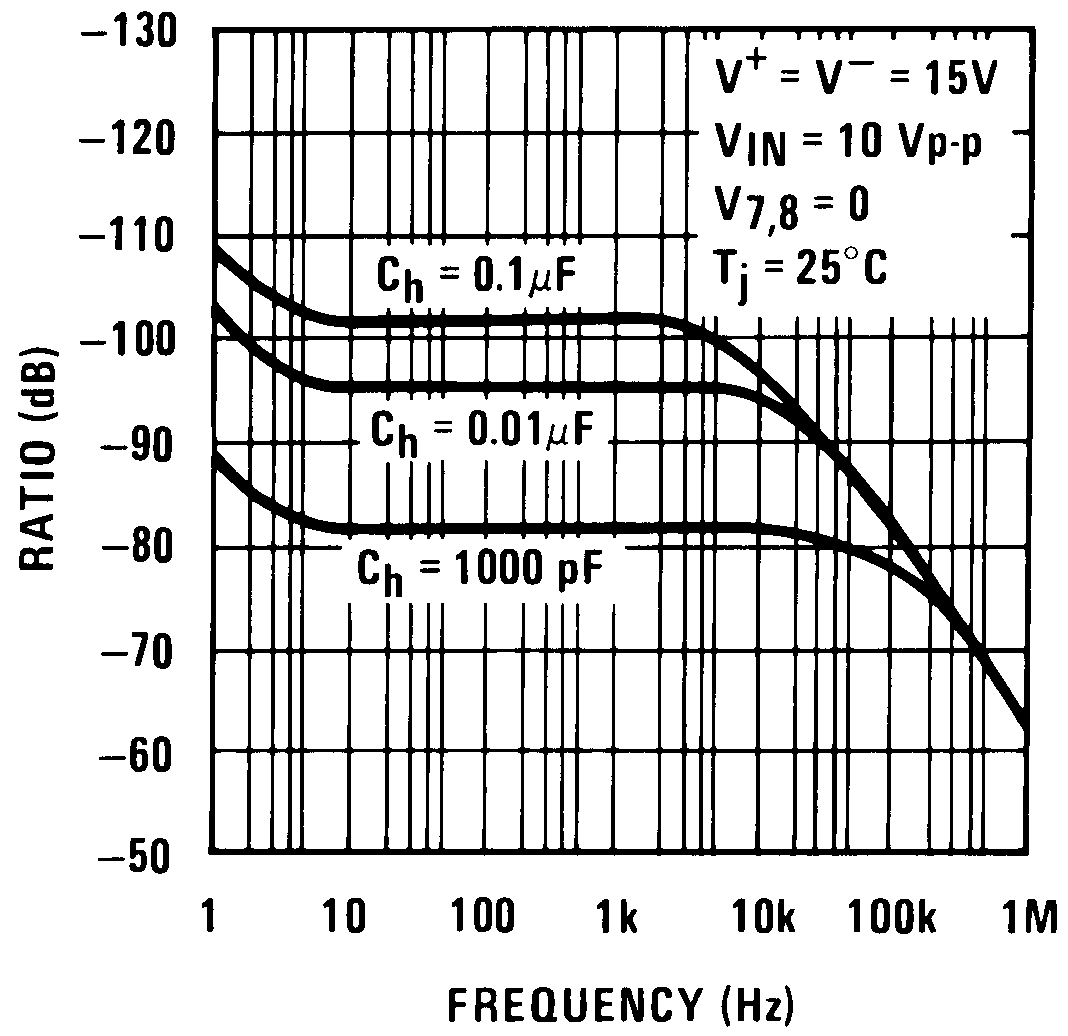

Figure 12. Output Noise  Figure 14. Feedthrough Rejection Ratio (Hold Mode)

Figure 14. Feedthrough Rejection Ratio (Hold Mode)  Figure 16. Output Transient at Start of Sample Mode

Figure 16. Output Transient at Start of Sample Mode