JAJSDE2 June 2017 LM317HV-MIL

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

-

8 Application and Implementation

- 8.1 Application Information

- 8.2

Typical Applications

- 8.2.1 1.25-V to 45-V High Voltage Adjustable Regulator

- 8.2.2 Digitally Selected Outputs

- 8.2.3 Logic Regulator (5-V) With Electronic Shutdown

- 8.2.4 Slow Turnon 15-V Regulator

- 8.2.5 Adjustable Regulator With Improved Ripple Rejection

- 8.2.6 High Stability 10-V Regulator

- 8.2.7 High Current Adjustable Regulator

- 8.2.8 Emitter Follower Current Amplifier

- 8.2.9 1-A Current Regulator

- 8.2.10 Common Emitter Amplifier

- 8.2.11 Low-Cost, 3-A Switching Regulator

- 8.2.12 Adjustable Multiple On-Card Regulators With Single Control

- 8.2.13 AC Voltage Regulator

- 8.2.14 12-V Battery Charger

- 8.2.15 Adjustable 4-A Regulator

- 8.2.16 Current Limited 6-V Charger

- 9 Power Supply Recommendations

- 10Layout

- 11デバイスおよびドキュメントのサポート

- 12メカニカル、パッケージ、および注文情報

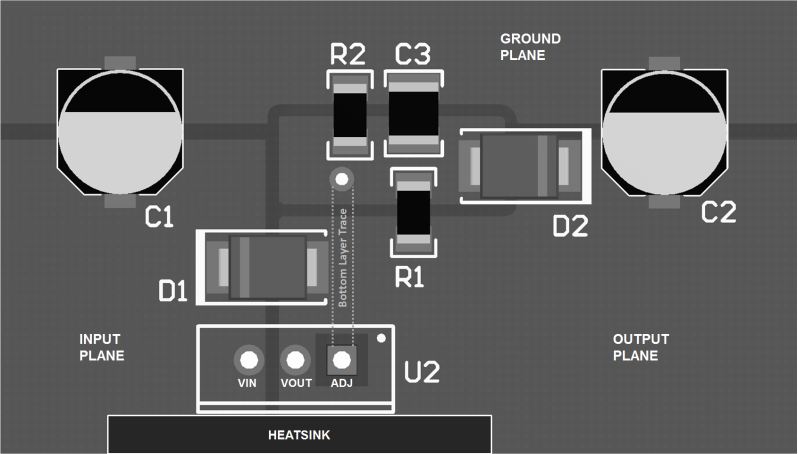

10 Layout

10.1 Layout Guidelines

Some layout guidelines should be followed to ensure proper regulation of the output voltage with minimum noise. Traces carrying the load current should be wide to reduce the amount of parasitic trace inductance and the feedback loop from V2 to ADJ should be kept as short as possible. To improve PSRR, a bypass capacitor can be placed at the ADJ pin and should be located as close as possible to the IC. In cases when VIN shorts to ground, an external diode should be placed from VOUT to VIN to divert the surge current from the output capacitor and protect the IC. Similarly, in cases when a large bypass capacitor is placed at the ADJ pin and VOUT shorts to ground, an external diode should be placed from ADJ to VOUT to provide a path for the bypass capacitor to discharge. These diodes should be placed close to the corresponding IC pins to increase their effectiveness.

10.2 Layout Example

Figure 33. Layout Example (TO-220 Package)

Figure 33. Layout Example (TO-220 Package)