JAJS807F December 1999 – May 2016 LM3411

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

-

9 Application and Implementation

- 9.1 Application Information

- 9.2

Typical Applications

- 9.2.1 LM3411 Typical Application

- 9.2.2 Isolated 250-mA Flyback Switching Regulator

- 9.2.3 Isolated 1.5-A Flyback Switching Regulator

- 9.2.4 Precision 1-A Buck Regulator

- 9.2.5 Negative Input, Negative or Positive Output Flyback Regulator

- 9.2.6 Precision 5-V, 1-A Low Dropout Regulator

- 9.2.7 3.3-V, 0.5-A Low Dropout Regulator

- 9.2.8 Precision Positive Voltage Regulator With Accurate Current Limit

- 9.2.9 Precision Negative Voltage Regulator

- 9.2.10 4.7-V Power ON Detector With Hysteresis

- 9.2.11 ±50-mV External Trim

- 9.2.12 250-mA Shunt Regulator

- 9.2.13 Voltage Detector

- 9.2.14 Overvoltage Crowbar

- 10Power Supply Recommendations

- 11Layout

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)(2)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| Input voltage, VIN | 20 | V | ||

| Output current | 20 | mA | ||

| Power dissipation (TA = 25°C)(3) | 300 | mW | ||

| Lead temperature | Vapor phase (60 s) | 215 | °C | |

| Infrared (15 s) | 220 | |||

| Junction temperature | 150 | °C | ||

| Storage temperature, Tstg | –65 | 150 | °C | |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) See AN-450 Surface Mounting Methods and Their Effect on Product Reliability (SNOA742) for methods on soldering surface-mount devices.

(3) The maximum power dissipation must be derated at elevated temperatures and is dictated by TJmax (maximum junction temperature), RθJA (junction to ambient thermal resistance), and TA (ambient temperature). The maximum allowable power dissipation at any temperature is (PDmax = TJmax – TA) / RθJA or the number given in the Absolute Maximum Ratings, whichever is lower. The typical thermal resistance (RθJA) when soldered to a printed-circuit board is approximately 306°C/W for the DBV package.

6.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±1500 | V |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)(1)| MIN | NOM | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| VI | Input voltage | LM3411x 3.3-V | 3.3 | V | ||

| LM3411x 5-V | 5 | |||||

| IO | Output current | 0 | 15 | mA | ||

| TA | Ambient temperature | –40 | 85 | °C | ||

| TJ | Operating junction temperature | –40 | 125 | °C | ||

(1) The maximum power dissipation must be derated at elevated temperatures and is dictated by TJmax (maximum junction temperature), RθJA (junction to ambient thermal resistance), and TA (ambient temperature). The maximum allowable power dissipation at any temperature is (PDmax = TJmax − TA)/RθJA or the number given in the Absolute Maximum Ratings, whichever is lower. The typical thermal resistance (RθJA) when soldered to a printed-circuit board is approximately 306°C/W for the DBV package.

6.4 Thermal Information

| THERMAL METRIC(1) | LM3411 | UNIT | |

|---|---|---|---|

| DBV (SOT-23) | |||

| 5 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 178.6 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 134.7 | °C/W |

| RθJB | Junction-to-board thermal resistance | 37.3 | °C/W |

| ψJT | Junction-to-top characterization parameter | 24.7 | °C/W |

| ψJB | Junction-to-board characterization parameter | 36.8 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | — | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

6.5 Electrical Characteristics: 3.3-V Version

Specifications are for TJ = 25°C, VIN = VREG, and VOUT = 1.5 V (unless otherwise noted).| PARAMETER | TEST CONDITIONS | MIN(1) | TYP(2) | MAX(1) | UNIT | |||

|---|---|---|---|---|---|---|---|---|

| VREG | Regulation voltage | IOUT = 5 mA | LM3411A 3.3-V | TJ = 25°C | 3.284 | 3.3 | 3.317 | V |

| –40°C ≤ TJ ≤ 125°C | 3.267 | 3.333 | ||||||

| LM3411 3.3-V | TJ = 25°C | 3.267 | 3.3 | 3.333 | ||||

| –40°C ≤ TJ ≤ 125°C | 3.234 | 3.366 | ||||||

| Regulation voltage tolerance | IOUT = 5 mA | LM3411A 3.3-V | TJ = 25°C | ±0.5% | ||||

| –40°C ≤ TJ ≤ 125°C | ±1% | |||||||

| LM3411 3.3-V | TJ = 25°C | ±1% | ||||||

| –40°C ≤ TJ ≤ 125°C | ±2% | |||||||

| Iq | Quiescent current | IOUT = 5 mA | LM3411A 3.3-V | TJ = 25°C | 85 | 110 | μA | |

| –40°C ≤ TJ ≤ 125°C | 115 | |||||||

| LM3411 3.3-V | TJ = 25°C | 85 | 125 | |||||

| –40°C ≤ TJ ≤ 125°C | 150 | |||||||

| Gm | Transconductance ΔIOUT/ΔVREG |

20 μA ≤ IOUT ≤ 1 mA | LM3411A 3.3-V | TJ = 25°C | 1.5 | 3.3 | mA/mV | |

| –40°C ≤ TJ ≤ 125°C | 0.75 | |||||||

| LM3411 3.3-V | TJ = 25°C | 1 | 3.3 | |||||

| –40°C ≤ TJ ≤ 125°C | 0.5 | |||||||

| 1 mA ≤ IOUT ≤ 15 mA | LM3411A 3.3-V | TJ = 25°C | 3.3 | 6 | ||||

| –40°C ≤ TJ ≤ 125°C | 2 | |||||||

| LM3411 3.3-V | TJ = 25°C | 2.5 | 6 | |||||

| –40°C ≤ TJ ≤ 125°C | 1.7 | |||||||

| AV | Voltage gain ΔVOUT/ΔVREG |

RL = 140 Ω(3) | LM3411A 3.3-V | TJ = 25°C, 1 V ≤ VOUT ≤ VREG – 1.2 V |

550 | 1000 | V/V | |

| −40°C ≤ TJ ≤ 125°C, 1 V ≤ VOUT ≤ VREG – 1.3 V |

250 | |||||||

| LM3411 3.3-V | TJ = 25°C, 1 V ≤ VOUT ≤ VREG – 1.2 V |

450 | 1000 | |||||

| −40°C ≤ TJ ≤ 125°C, 1 V ≤ VOUT ≤ VREG – 1.3 V |

200 | |||||||

| RL = 2 kΩ | LM3411A 3.3-V | TJ = 25°C, 1 V ≤ VOUT ≤ VREG – 1.2 V |

1500 | 3500 | ||||

| −40°C ≤ TJ ≤ 125°C, 1 V ≤ VOUT ≤ VREG – 1.3 V |

900 | |||||||

| LM3411 3.3-V | TJ = 25°C, 1 V ≤ VOUT ≤ VREG – 1.2 V |

1000 | 3500 | |||||

| −40°C ≤ TJ ≤ 125°C, 1 V ≤ VOUT ≤ VREG – 1.3 V |

700 | |||||||

| VSAT | Output saturation(4) | VIN = VREG + 100 mV, IOUT = 15 mA |

LM3411A 3.3-V | TJ = 25°C | 1 | 1.2 | V | |

| –40°C ≤ TJ ≤ 125°C | 1.3 | |||||||

| LM3411 3.3-V | TJ = 25°C | 1 | 1.2 | |||||

| –40°C ≤ TJ ≤ 125°C | 1.3 | |||||||

| IL | Output leakage current | VIN = VREG – 100 mV, VOUT = 0 V |

LM3411A 3.3-V | TJ = 25°C | 0.1 | 0.5 | μA | |

| –40°C ≤ TJ ≤ 125°C | 1 | |||||||

| LM3411 3.3-V | TJ = 25°C | 0.1 | 0.5 | |||||

| –40°C ≤ TJ ≤ 125°C | 1 | |||||||

| Rf | Internal feedback resistor | LM3411A 3.3-V | 39 | 52 | 65 | kΩ | ||

| LM3411 3.3-V | 39 | 52 | 65 | |||||

| En | Output noise voltage | IOUT = 1 mA, 10 Hz ≤ f ≤ 10 kHz | 50 | μVRMS | ||||

(1) Limits are 100% production tested at 25°C. Limits over the operating temperature range are ensured through correlation using Statistical Quality Control (SQC) methods. The limits are used to calculate TIs Averaging Outgoing Level (AOQL).

(2) Typical numbers are at 25°C and represent the most likely parametric norm.

(3) Actual test is done using equivalent current sink instead of a resistor load.

(4) VSAT = VIN – VOUT, when the voltage at the IN pin is forced 100 mV above the nominal regulating voltage (VREG).

6.6 Electrical Characteristics: 5-V Version

Specifications are for TJ = 25°C, VIN = VREG, and VOUT = 1.5 V (unless otherwise noted).| PARAMETER | TEST CONDITIONS | MIN(1) | TYP(2) | MAX(1) | UNIT | |||

|---|---|---|---|---|---|---|---|---|

| VREG | Regulation voltage | IOUT = 5 mA | LM3411A 5-V | TJ = 25°C | 4.975 | 5 | 5.025 | V |

| –40°C ≤ TJ ≤ 125°C | 4.95 | 5.05 | ||||||

| LM3411 5-V | TJ = 25°C | 4.95 | 5 | 5.05 | ||||

| –40°C ≤ TJ ≤ 125°C | 4.9 | 5.1 | ||||||

| Regulation voltage tolerance | IOUT = 5 mA | LM3411A 5-V | TJ = 25°C | ±0.5% | ||||

| –40°C ≤ TJ ≤ 125°C | ±1% | |||||||

| LM3411 5-V | TJ = 25°C | ±1% | ||||||

| –40°C ≤ TJ ≤ 125°C | ±2% | |||||||

| Iq | Quiescent current | IOUT = 5 mA | LM3411A 5-V | TJ = 25°C | 85 | 110 | μA | |

| –40°C ≤ TJ ≤ 125°C | 115 | |||||||

| LM3411 5-V | TJ = 25°C | 85 | 125 | |||||

| –40°C ≤ TJ ≤ 125°C | 150 | |||||||

| Gm | Transconductance ΔIOUT/ΔVREG |

20 μA ≤ IOUT ≤ 1 mA | LM3411A 5-V | TJ = 25°C | 1.5 | 3.3 | mA/mV | |

| –40°C ≤ TJ ≤ 125°C | 0.75 | |||||||

| LM3411 5-V | TJ = 25°C | 1 | 3.3 | |||||

| –40°C ≤ TJ ≤ 125°C | 0.5 | |||||||

| 1 mA ≤ IOUT ≤ 15 mA | LM3411A 5-V | TJ = 25°C | 3.3 | 6 | ||||

| –40°C ≤ TJ ≤ 125°C | 2 | |||||||

| LM3411 5-V | TJ = 25°C | 2.5 | 6 | |||||

| –40°C ≤ TJ ≤ 125°C | 1.7 | |||||||

| AV | Voltage gain ΔVOUT/ΔVREG |

RL = 250 Ω(3) | LM3411A 5-V | TJ = 25°C, 1 V ≤ VOUT ≤ VREG – 1.2 V |

750 | 1000 | V/V | |

| −40°C ≤ TJ ≤ 125°C, 1 V ≤ VOUT ≤ VREG – 1.3 V |

350 | |||||||

| LM3411 5-V | TJ = 25°C, 1 V ≤ VOUT ≤ VREG – 1.2 V |

650 | 1000 | |||||

| −40°C ≤ TJ ≤ 125°C, 1 V ≤ VOUT ≤ VREG – 1.3 V |

300 | |||||||

| RL = 2 kΩ | LM3411A 5-V | TJ = 25°C, 1 V ≤ VOUT ≤ VREG – 1.2 V |

1500 | 3500 | ||||

| −40°C ≤ TJ ≤ 125°C, 1 V ≤ VOUT ≤ VREG – 1.3 V |

900 | |||||||

| LM3411 5-V | TJ = 25°C, 1 V ≤ VOUT ≤ VREG – 1.2 V |

1000 | 3500 | |||||

| −40°C ≤ TJ ≤ 125°C, 1 V ≤ VOUT ≤ VREG – 1.3 V |

700 | |||||||

| VSAT | Output saturation(4) | VIN = VREG + 100 mV, IOUT = 15 mA |

LM3411A 5-V | TJ = 25°C | 1 | 1.2 | V | |

| –40°C ≤ TJ ≤ 125°C | 1.3 | |||||||

| LM3411 5-V | TJ = 25°C | 1 | 1.2 | |||||

| –40°C ≤ TJ ≤ 125°C | 1.3 | |||||||

| IL | Output leakage current | VIN = VREG – 100 mV, VOUT = 0 V |

LM3411A 5-V | TJ = 25°C | 0.1 | 0.5 | μA | |

| –40°C ≤ TJ ≤ 125°C | 1 | |||||||

| LM3411 5-V | TJ = 25°C | 0.1 | 0.5 | |||||

| –40°C ≤ TJ ≤ 125°C | 1 | |||||||

| Rf | Internal feedback resistor | LM3411A 5-V | 70 | 94 | 118 | kΩ | ||

| LM3411 5-V | 70 | 94 | 118 | |||||

| En | Output noise voltage | IOUT = 1 mA, 10 Hz ≤ f ≤ 10 kHz | 80 | μVRMS | ||||

(1) Limits are 100% production tested at 25°C. Limits over the operating temperature range are ensured through correlation using Statistical Quality Control (SQC) methods. The limits are used to calculate TIs Averaging Outgoing Level (AOQL).

(2) Typical numbers are at 25°C and represent the most likely parametric norm.

(3) Actual test is done using equivalent current sink instead of a resistor load.

(4) VSAT = VIN – VOUT, when the voltage at the IN pin is forced 100 mV above the nominal regulating voltage (VREG).

6.7 Typical Characteristics

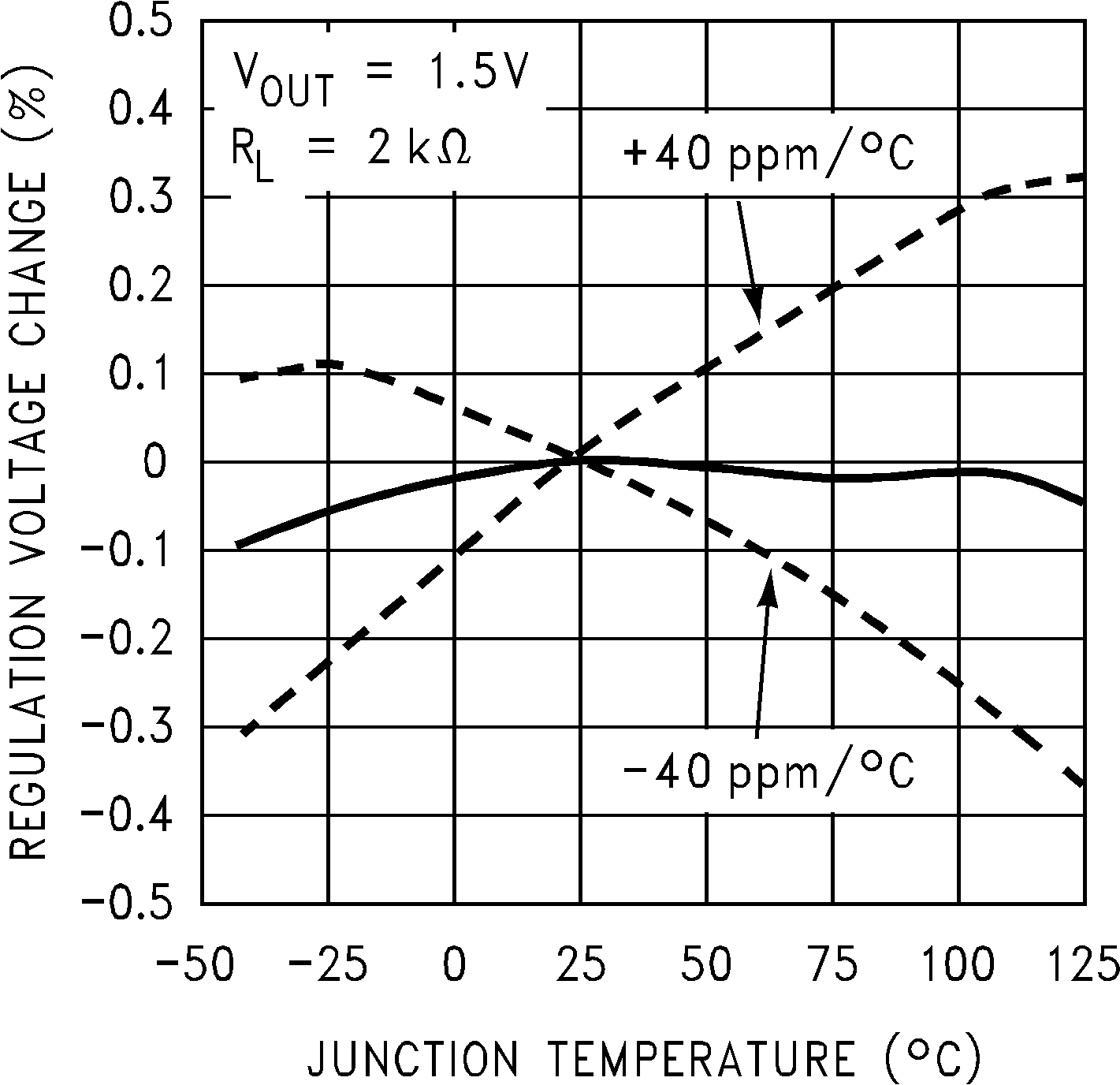

Figure 1. Normalized Temperature Drift

Figure 1. Normalized Temperature Drift

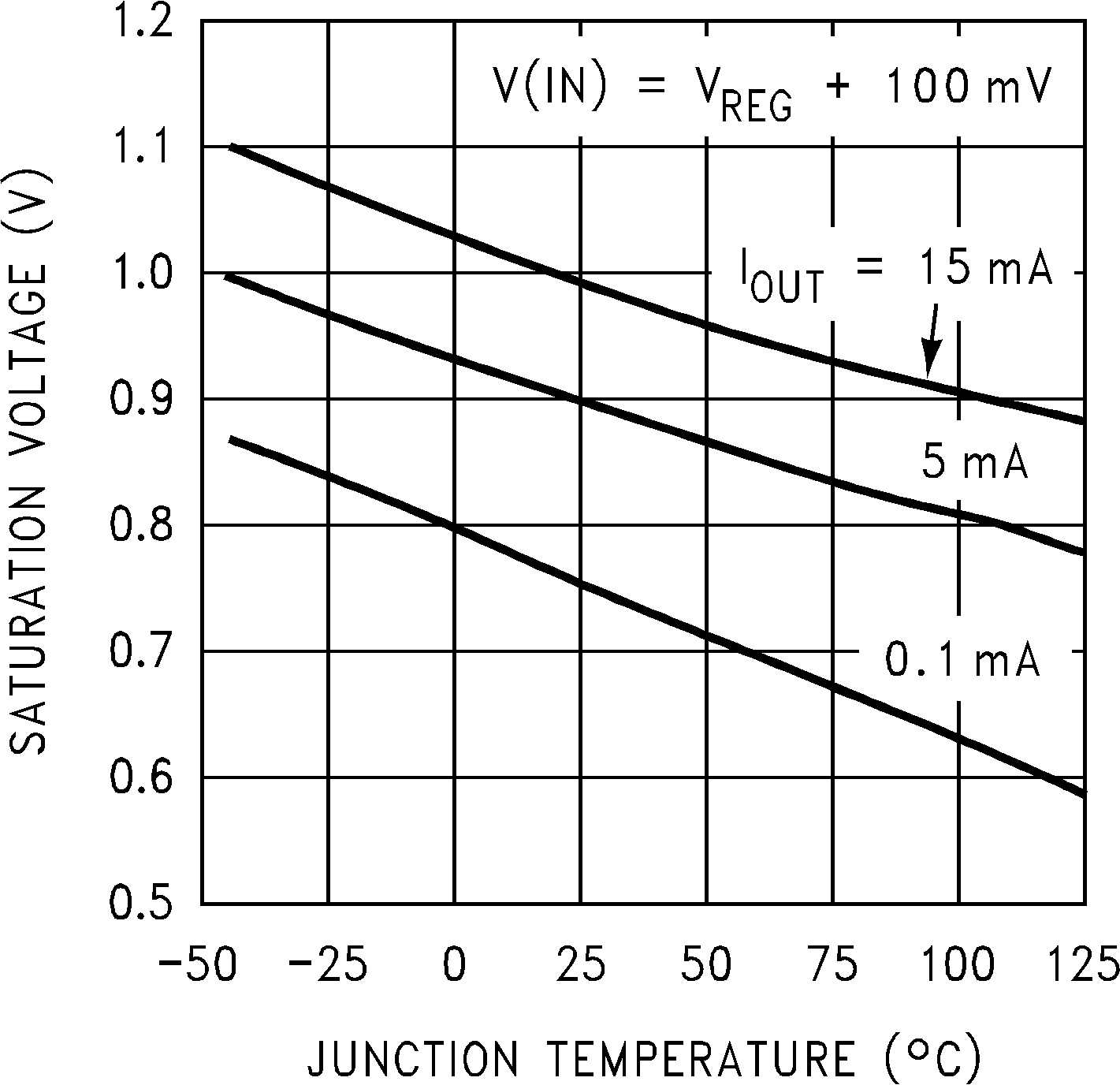

Figure 3. Output Saturation Voltage, VSAT

Figure 3. Output Saturation Voltage, VSAT

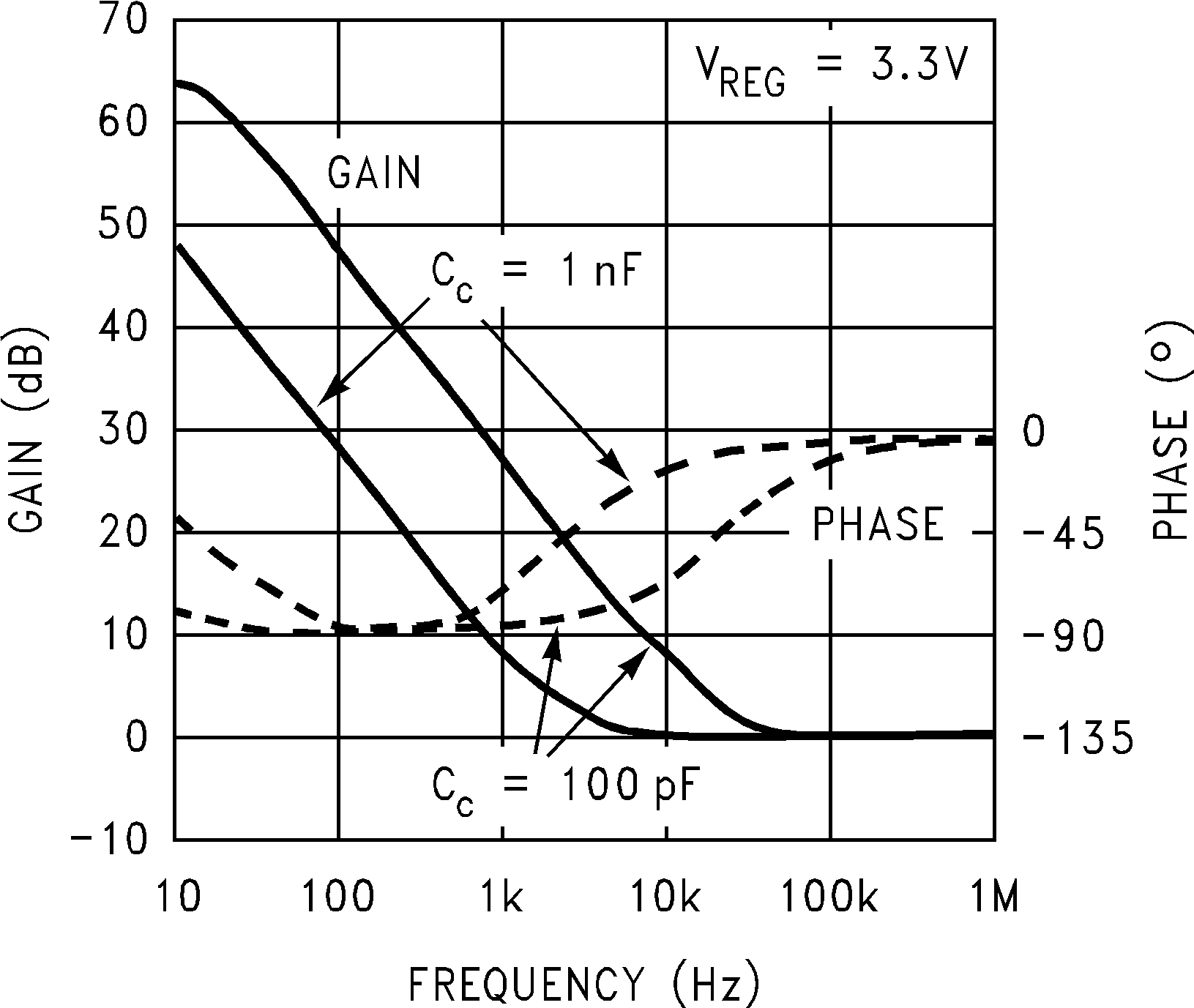

Figure 5. Bode Plot

Figure 5. Bode Plot

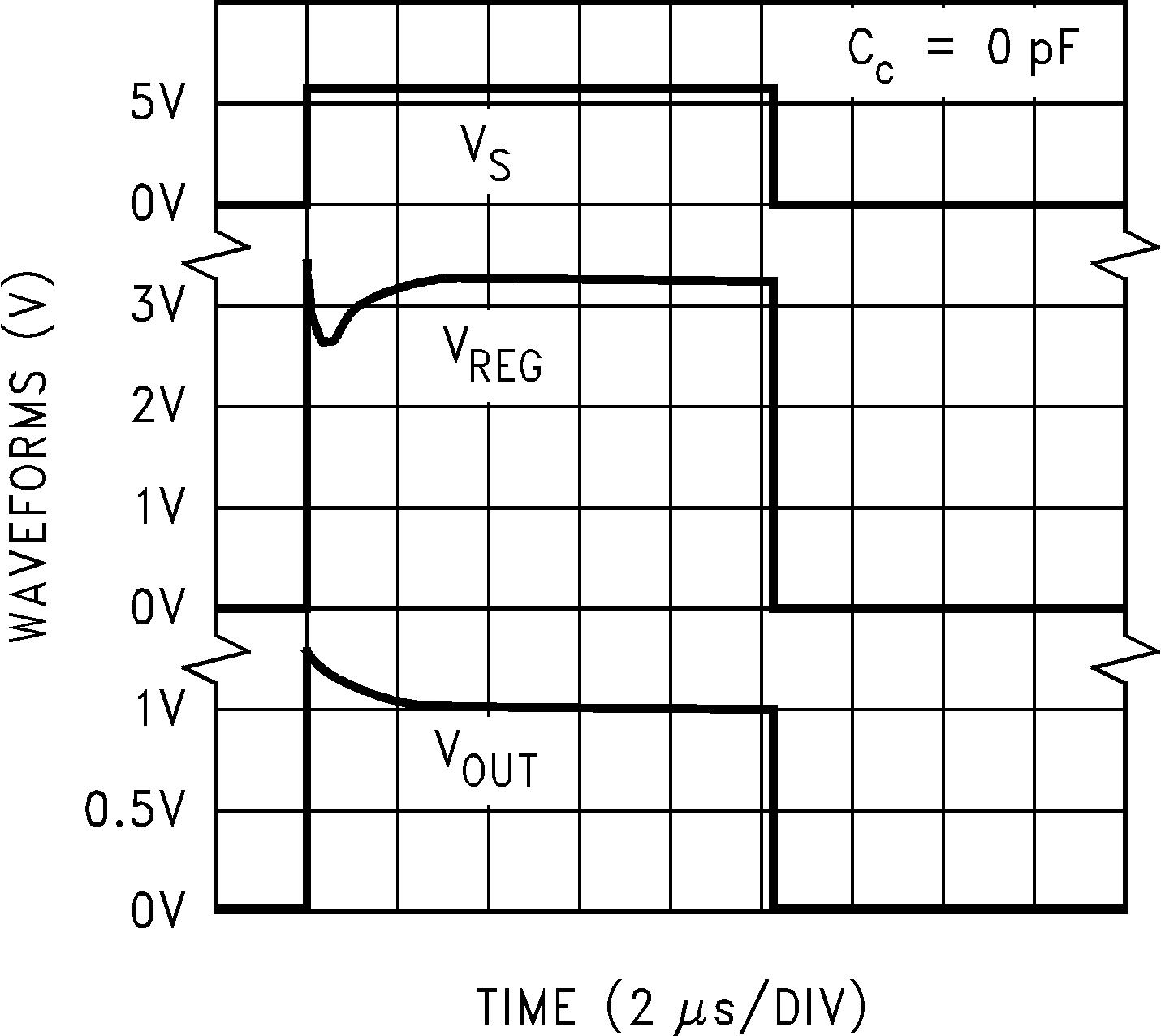

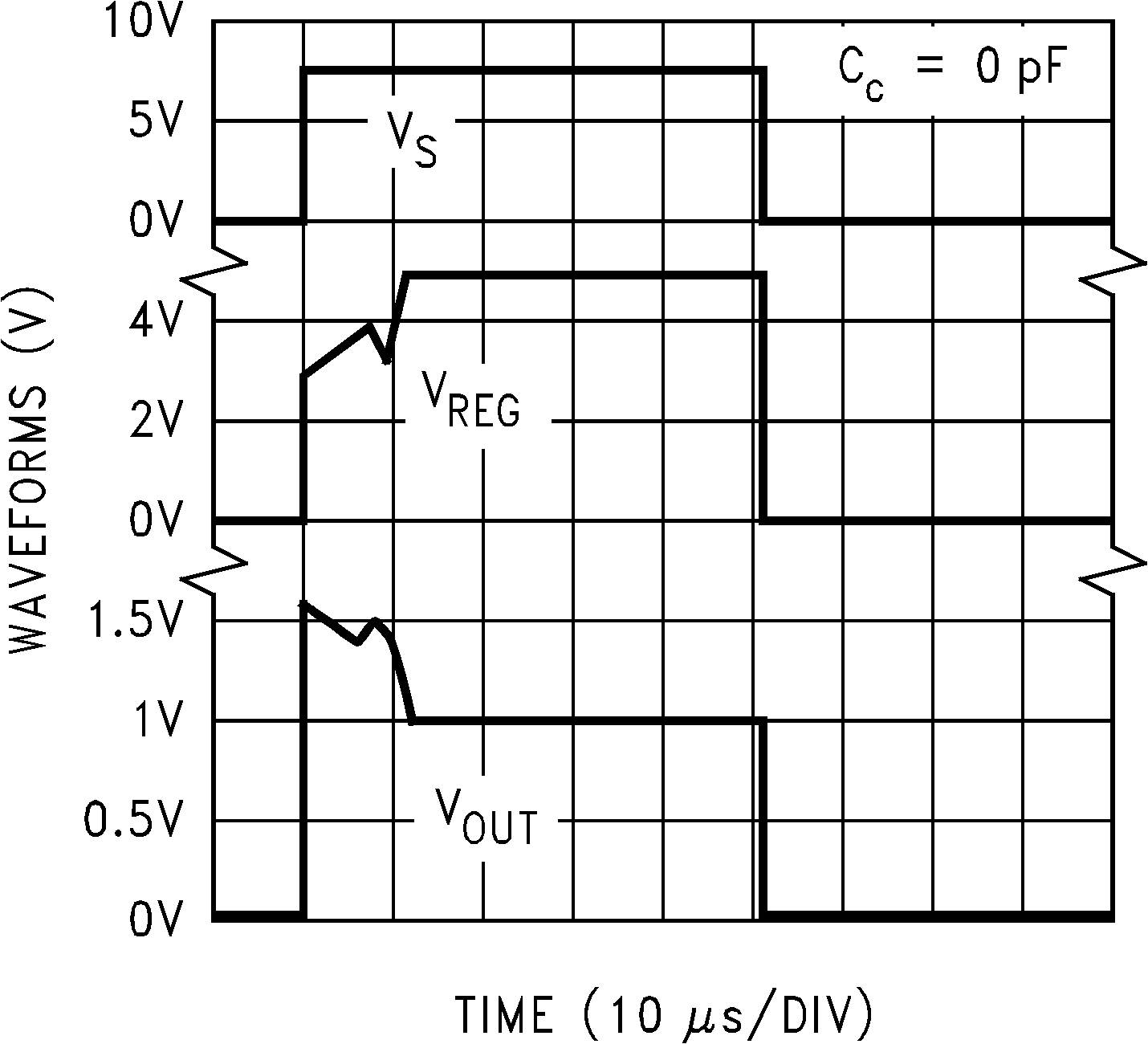

Figure 7. Response Time for 3.3-V Version (CC = 0 pF)

Figure 7. Response Time for 3.3-V Version (CC = 0 pF)

Figure 9. Response Time for 5-V Version (CC = 0 pF)

Figure 9. Response Time for 5-V Version (CC = 0 pF)

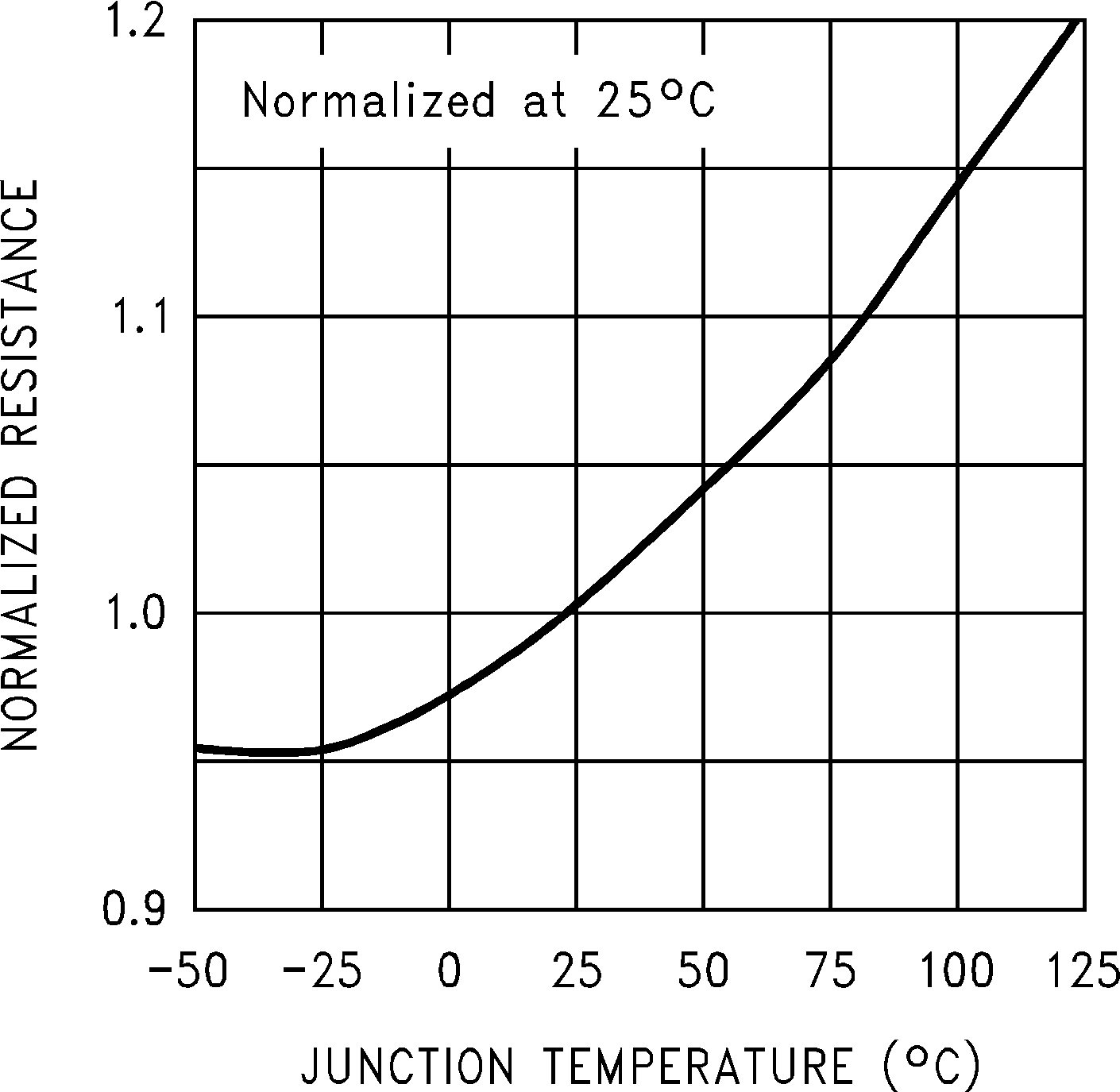

Figure 11. Tempco of Internal Feedback Resistor (Rf)

Figure 11. Tempco of Internal Feedback Resistor (Rf)

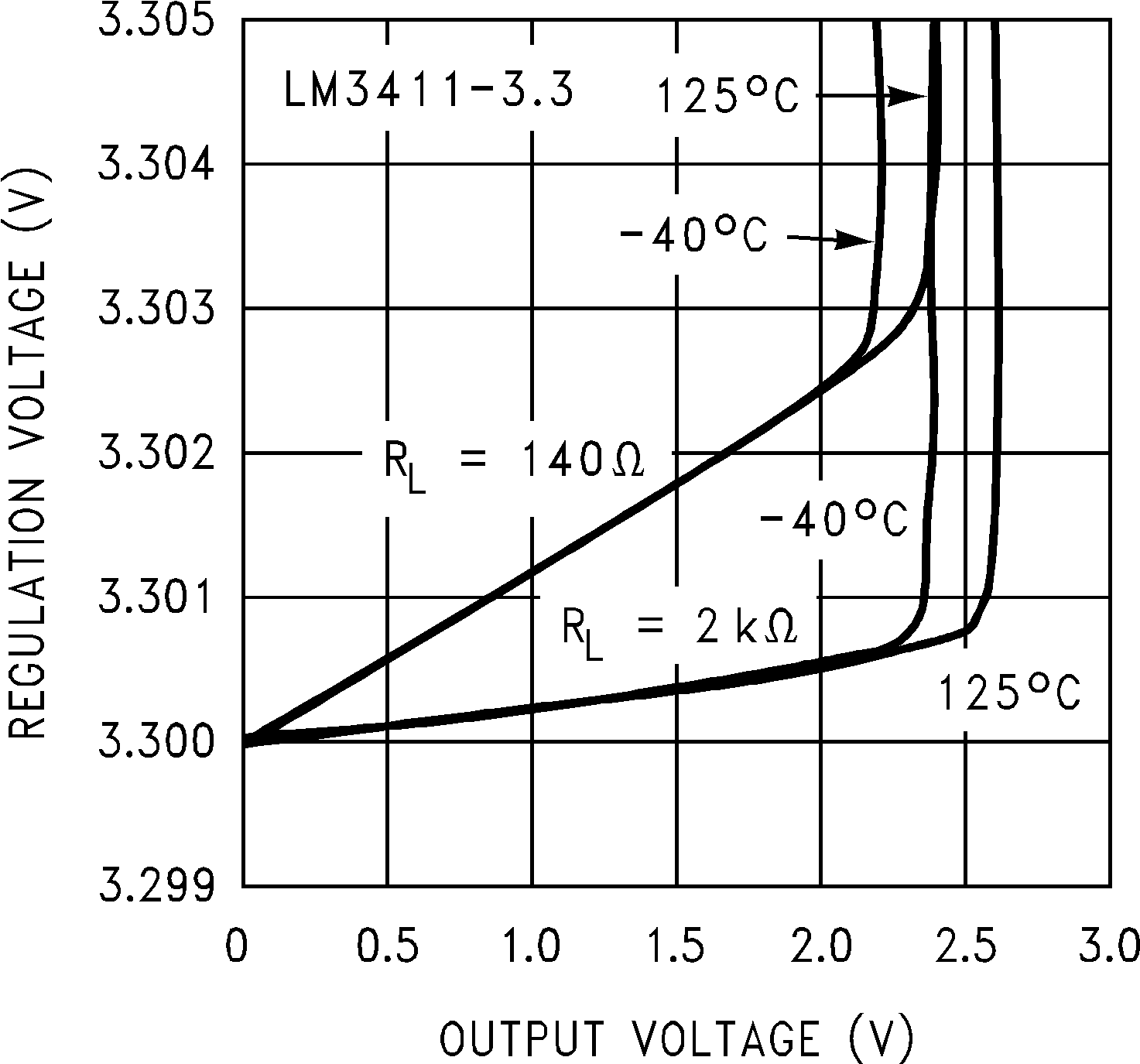

Figure 13. Regulation Voltage vs Output Voltage

Figure 13. Regulation Voltage vs Output Voltageand Load Resistance

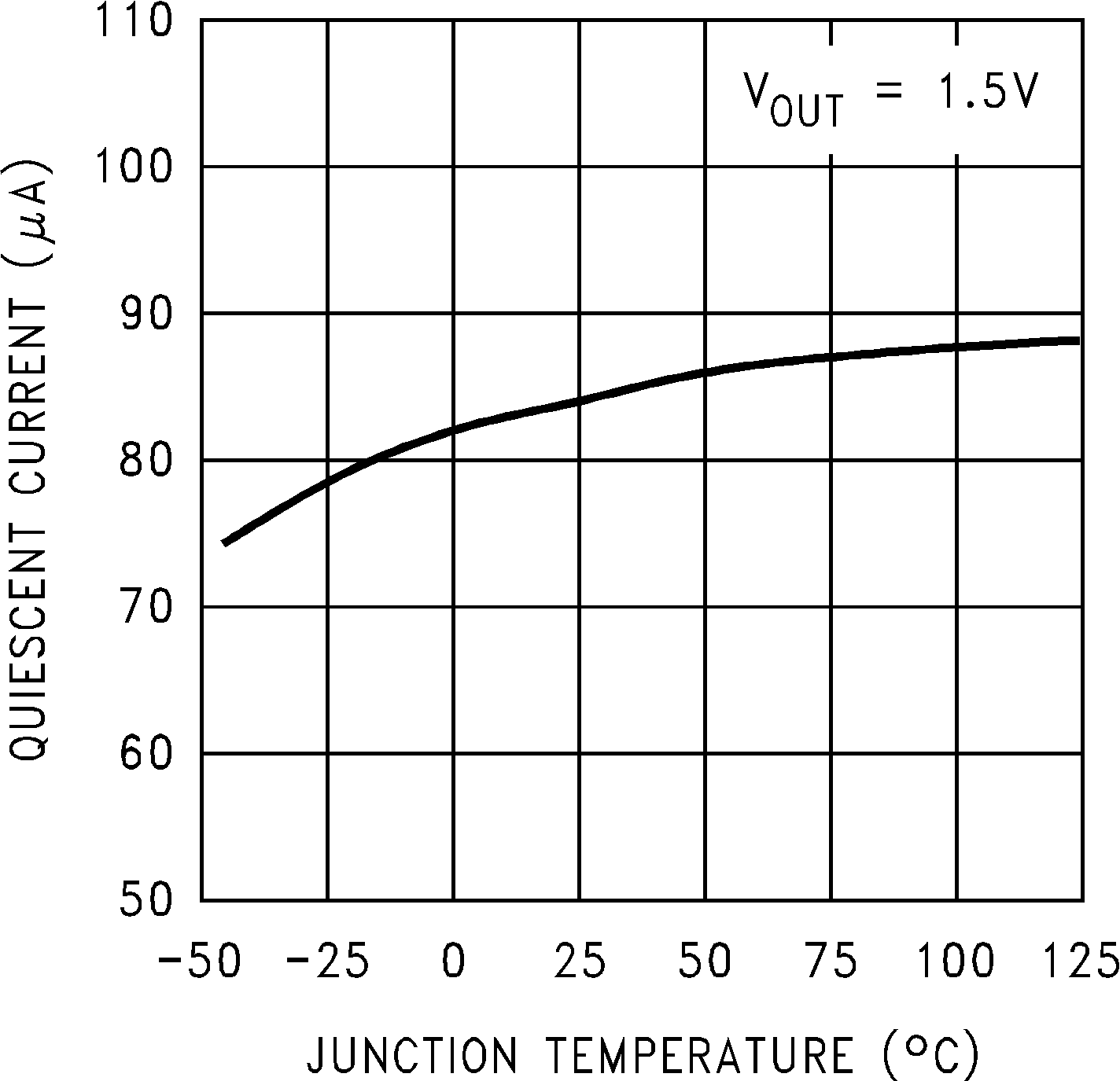

Figure 2. Quiescent Current

Figure 2. Quiescent Current

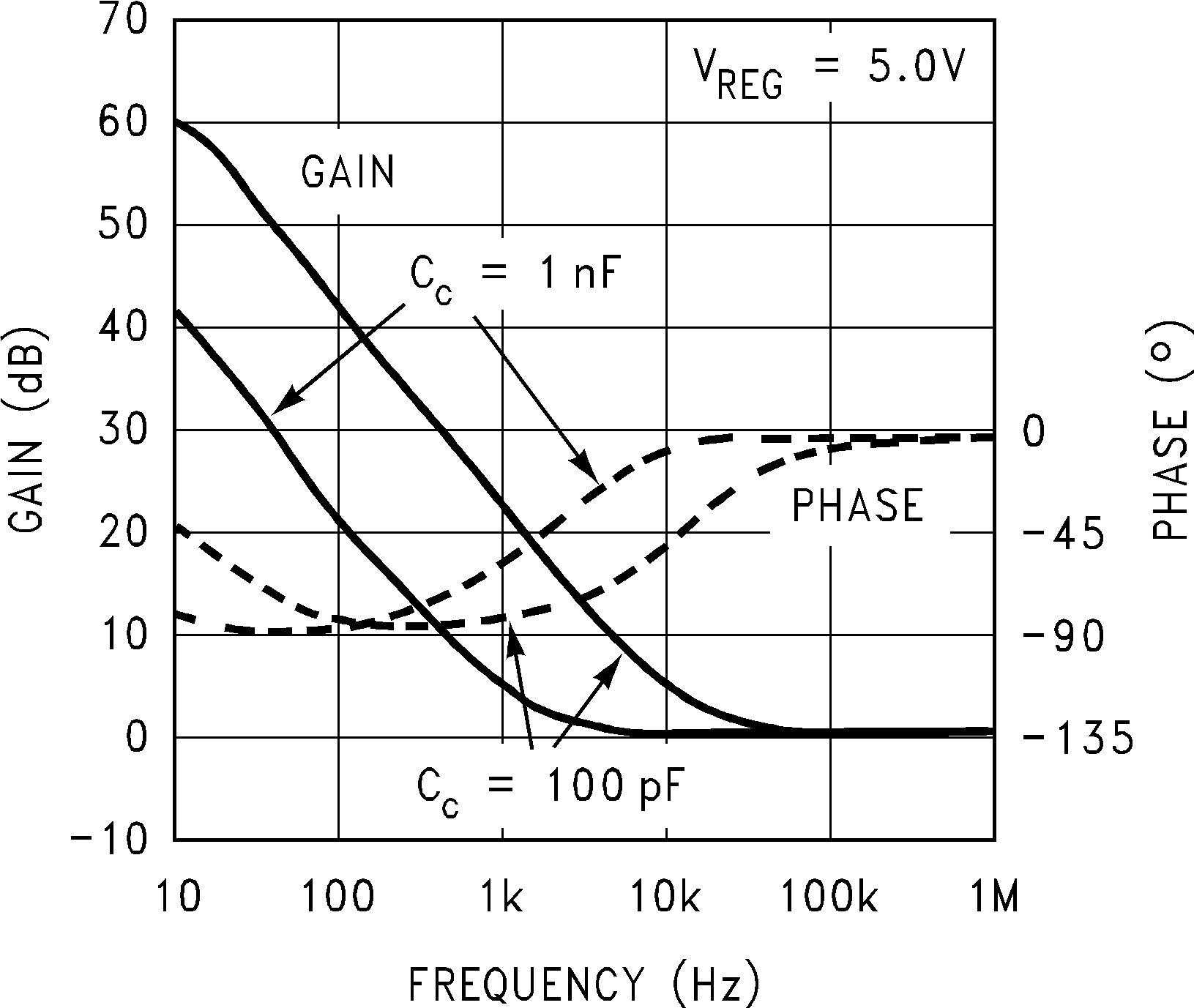

Figure 4. Bode Plot

Figure 4. Bode Plot

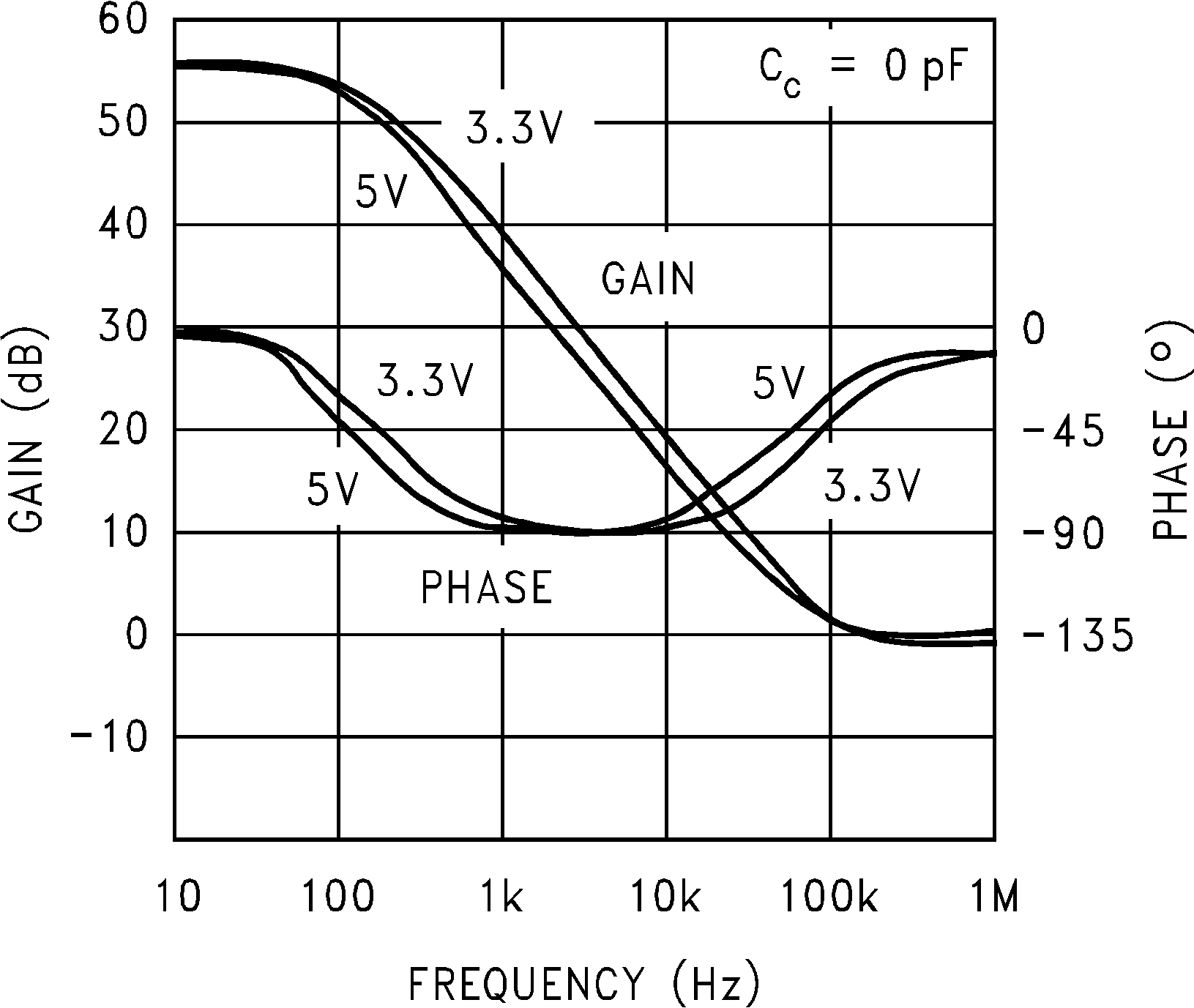

Figure 6. Bode Plot

Figure 6. Bode Plot

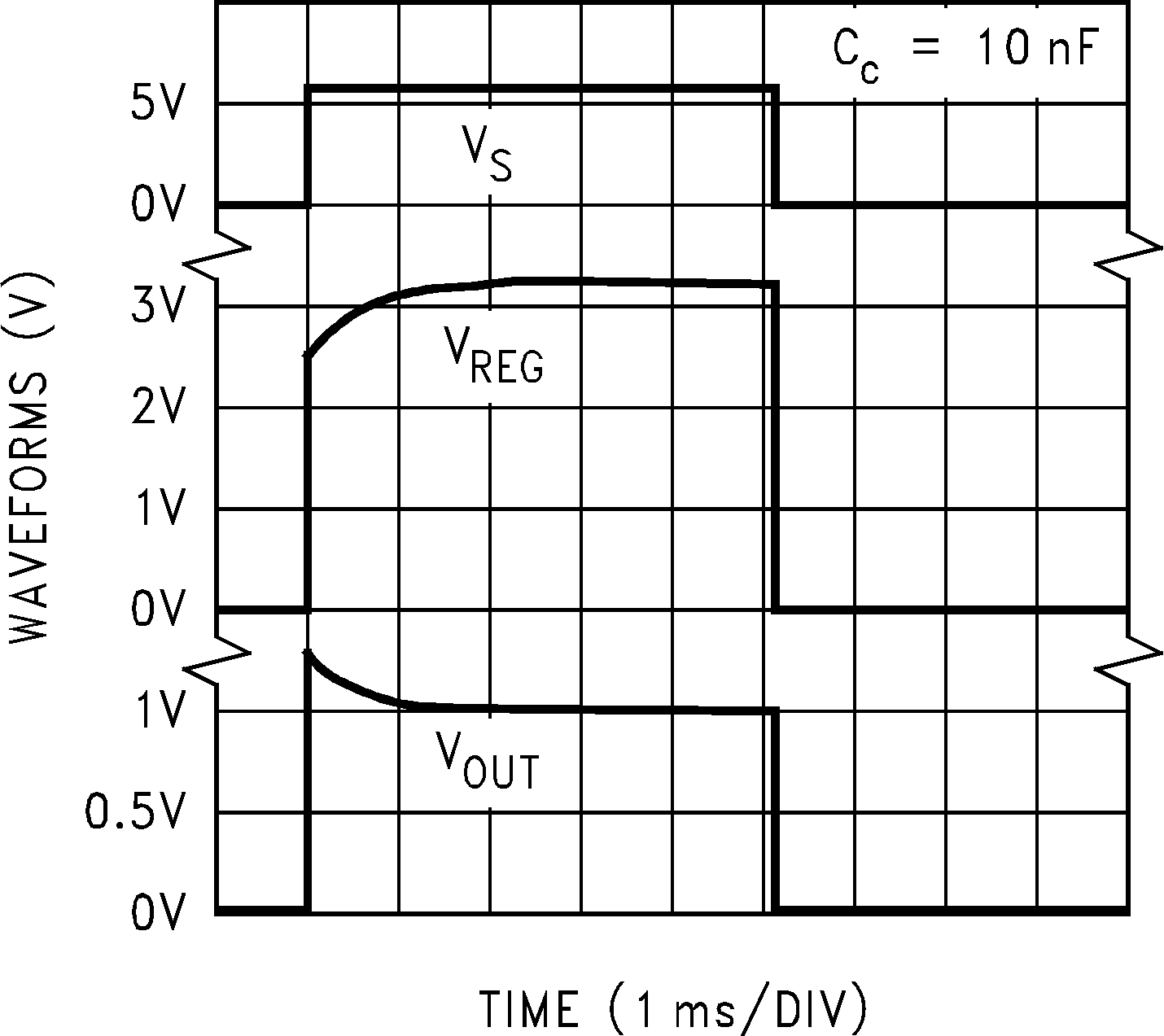

Figure 8. Response Time for 3.3-V Version (CC = 10 nF)

Figure 8. Response Time for 3.3-V Version (CC = 10 nF)

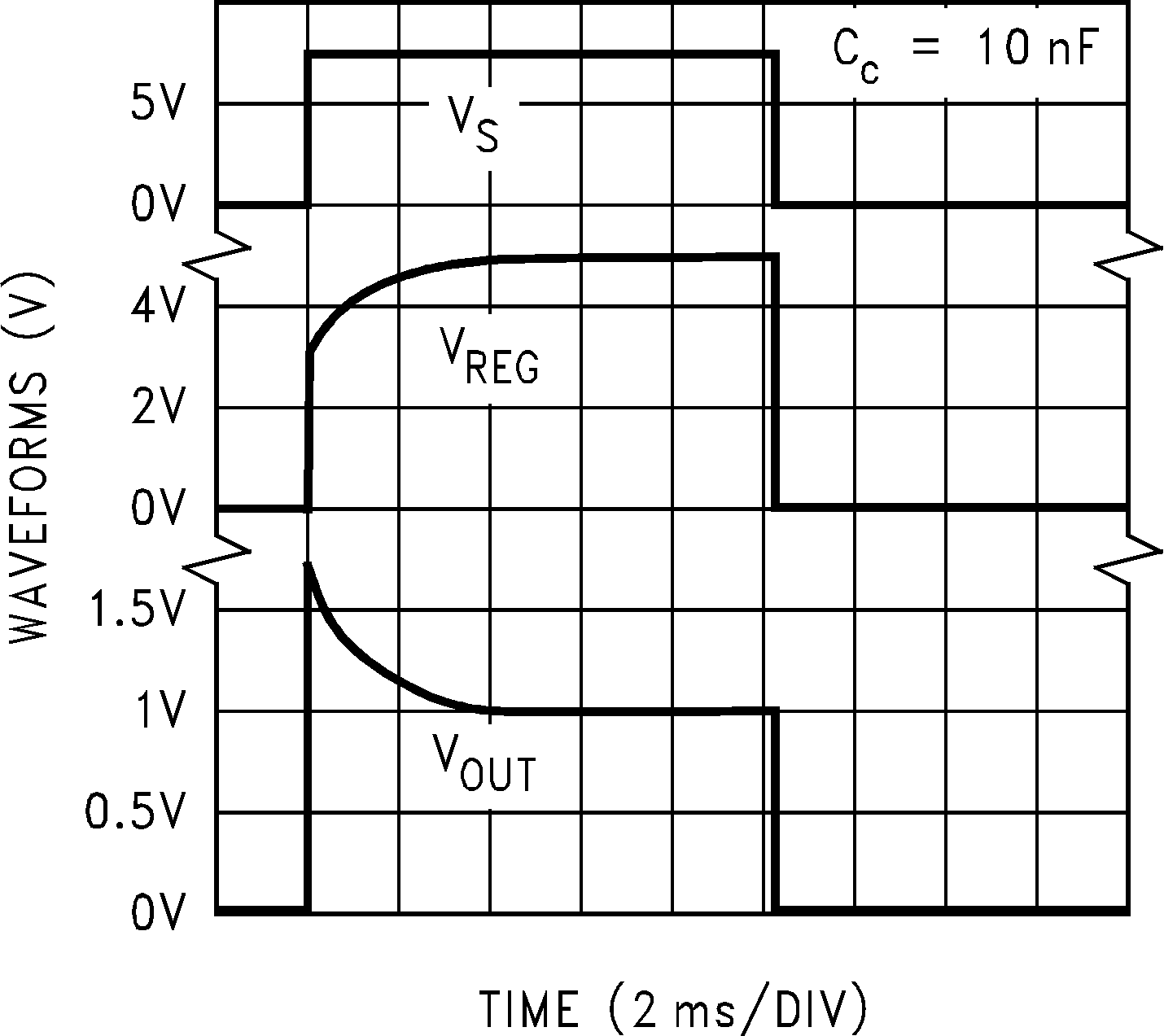

Figure 10. Response Time for 5-V Version (CC = 10 nF)

Figure 10. Response Time for 5-V Version (CC = 10 nF)

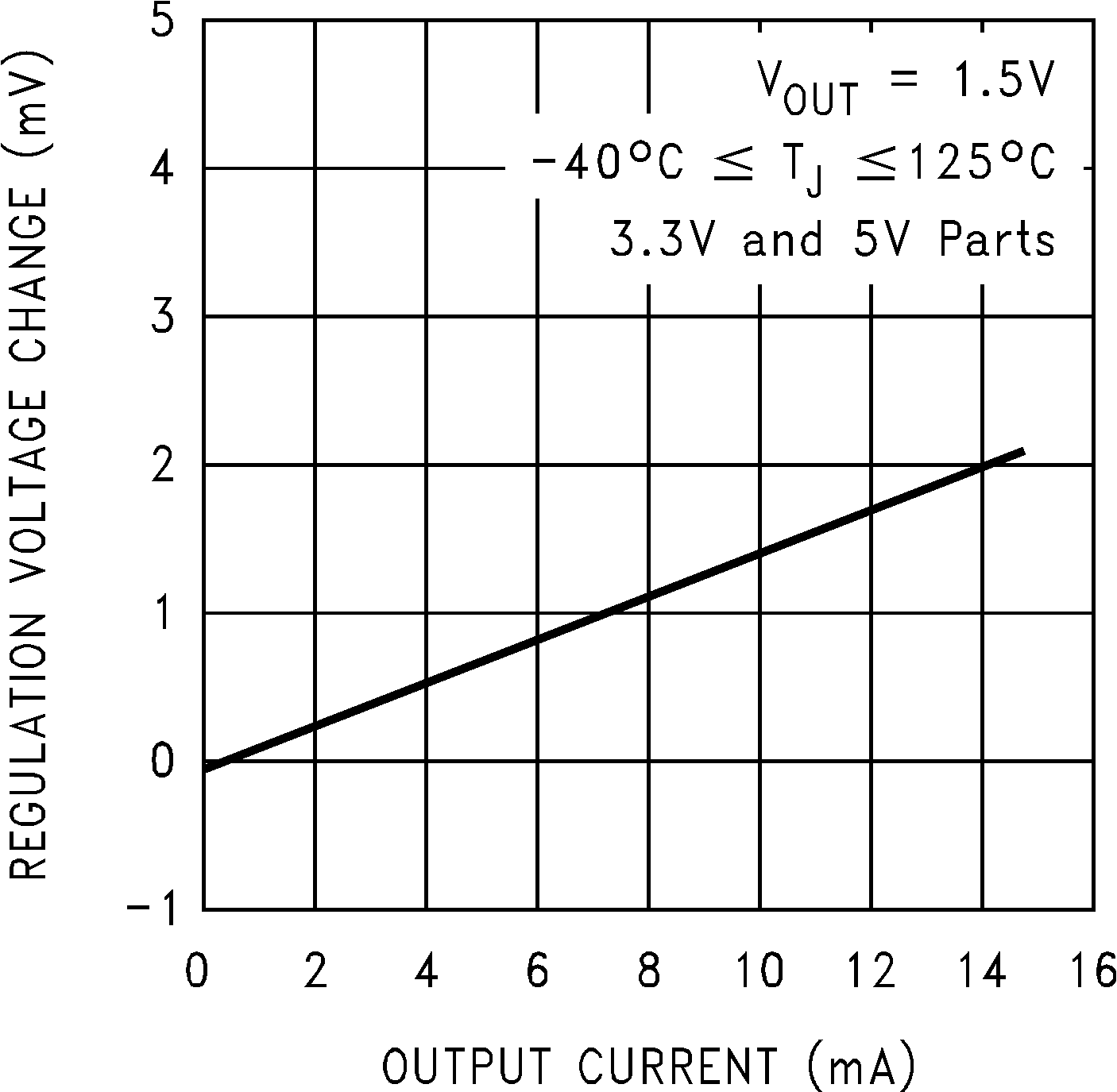

Figure 12. Regulation Voltage Change vs Output Current

Figure 12. Regulation Voltage Change vs Output Current

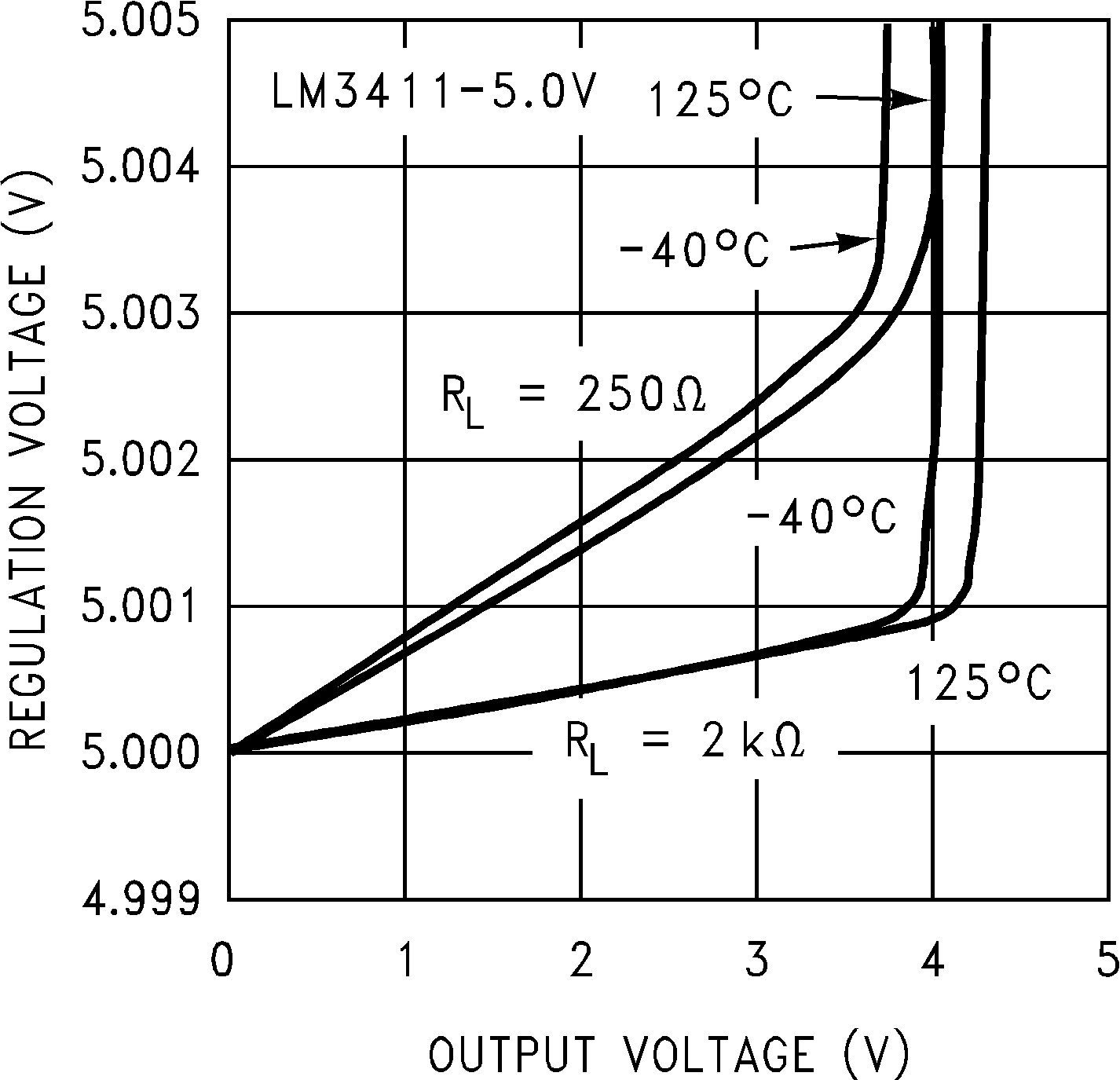

Figure 14. Regulation Voltage vs Output Voltage

Figure 14. Regulation Voltage vs Output Voltageand Load Resistance