JAJSDP5D February 2016 – March 2018 LM36273

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Features Description

- 7.3.1 Enabling the LM36273

- 7.3.2 Backlight

- 7.3.3 LCM Bias

- 7.3.4 Software Reset

- 7.3.5 HWEN Input

- 7.3.6 Thermal Shutdown (TSD)

- 7.4 Device Functional Modes

- 7.5 Programming

- 7.6

Register Maps

- 7.6.1 Revision Register (Address = 0x01)[Reset = 0x01]

- 7.6.2 Backlight Configuration1 Register (Address = 0x02)[Reset = 0x28]

- 7.6.3 Backlight Configuration 2 Register (Address = 0x03)[Reset = 0x8D]

- 7.6.4 Backlight Brightness LSB Register (Address = 0x04)[Reset = 0x07]

- 7.6.5 Backlight Brightness MSB Register (Address = 0x05)[Reset = 0xFF]

- 7.6.6 Backlight Auto-Frequency Low Threshold Register (Address = 0x06)[Reset = 0x00]

- 7.6.7 Backlight Auto-Frequency High Threshold Register (Address = 0x07)[Reset = 0x00]

- 7.6.8 Backlight Enable Register (Address = 0x08)[Reset = 0x00]

- 7.6.9 Bias Configuration 1 Register (Address = 0x09)[Reset = 0x18]

- 7.6.10 Bias Configuration 2 register (Address = 0x0A)[Reset = 0x11]

- 7.6.11 Bias Configuration 3 Register (Address = 0x0B)[Reset = 0x00]

- 7.6.12 LCM Boost Bias Register (Address = 0x0C)[Reset = 0x28]

- 7.6.13 VPOS Bias Register (Address = 0x0D)[Reset = 0x1E]

- 7.6.14 VNEG Bias Register (Address = 0x0E)[Reset = 0x1C]

- 7.6.15 Flags Register (Address = 0x0F)[Reset = 0x00]

- 7.6.16 Option 1 Register (Address = 0x10)[Reset = 0x06]

- 7.6.17 Option 2 Register (Address = 0x11)[Reset = 0x35]

- 7.6.18 PWM-to-Digital Code Readback LSB Register (Address = 0x12)[Reset = 0x00]

- 7.6.19 PWM-to-Digital Code Readback MSB Register (Address = 0x13)[Reset = 0x00]

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11デバイスおよびドキュメントのサポート

- 12メカニカル、パッケージ、および注文情報

8.2.2.1.2 Boost Output Capacitor Selection

At least an 1-μF capacitor is recommended for the backlight boost converter output capacitor. A high-quality ceramic type X5R or X7R is recommended. Voltage rating must be greater than the maximum output voltage that is used. The effective output capacitance must always remain higher than 0.4 μF for stable operation.

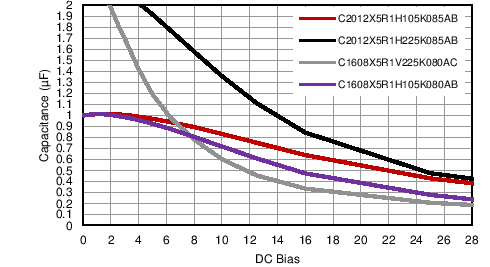

Table 31 lists possible backlight output capacitors that can be used with the LM36273. Figure 68 shows the DC bias of the four TDK capacitors. The useful voltage range is determined from the effective output voltage range for a given capacitor as determined by Equation 6:

Table 31. Recommended Backlight Output Capacitors

| PART NUMBER | MANUFACTURER | CASE SIZE | VOLTAGE RATING (V) | NOMINAL CAPACITANCE (µF) | TOLERANCE (%) | TEMPERATURE COEFFICIENT (%) | RECOMMENDED MAX OUTPUT VOLTAGE (FOR SINGLE CAPACITOR) |

|---|---|---|---|---|---|---|---|

| C2012X5R1H105K085AB | TDK | 0805 | 50 | 1 | ±10 | ±15 | 22 |

| C2012X5R1H225K085AB | TDK | 0805 | 50 | 2.2 | ±10 | ±15 | 24 |

| C1608X5R1V225K080AC | TDK | 0603 | 35 | 2.2 | ±10 | ±15 | 12 |

| C1608X5R1H105K080AB | TDK | 0603 | 50 | 1 | ±10 | ±15 | 15 |

For example, with a 10% tolerance, and a 15% temperature coefficient, the DC voltage derating must be ≥ 0.4 / (0.9 × 0.85) = 0.523 µF. For the C1608X5R1H225K080AB (0603, 50-V) device, the useful voltage range occurs up to the point where the DC bias derating falls below 0.523 µF, or around 12 V. For configurations where VOUT is > 15 V, two of these capacitors can be paralleled, or a larger capacitor such as the C2012X5R1H105K085AB must be used.

Figure 68. DC Bias Derating for 0805 Case Size and

Figure 68. DC Bias Derating for 0805 Case Size and

0603 Case Size 35-V and 50-V Ceramic Capacitors

For the LCM bias boost output a high-quality 10-μF ceramic type X5R or X7R capacitor is recommended. Voltage rating must be greater than the maximum output voltage that is used.