JAJSI47B April 2017 – October 2019 LMH0397

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 概要(続き)

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 4-Level Input Pins and Thresholds

- 8.3.2 Equalizer (EQ) and Cable Driver (CD) Mode Control

- 8.3.3 Input Carrier Detect

- 8.3.4 –6-dB Splitter Mode Launch Amplitude for SDI_IO+ (EQ Mode Only)

- 8.3.5 Continuous Time Linear Equalizer (CTLE)

- 8.3.6 Clock and Data (CDR) Recovery

- 8.3.7 Internal Eye Opening Monitor (EOM)

- 8.3.8 Output Function Control

- 8.3.9 Output Driver Control

- 8.3.10 Status Indicators and Interrupts

- 8.3.11 Additional Programmability

- 8.4 Device Functional Modes

- 8.5 Register Maps

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- RTV|32

サーマルパッド・メカニカル・データ

- RTV|32

発注情報

9.2.1.3 Application Curves

Depending on operation in EQ or CD Mode, the LMH0397 performance was measured with the test setups shown in Figure 22 and Figure 23.

Figure 22. Test Setup for LMH0397 in EQ Mode

Figure 22. Test Setup for LMH0397 in EQ Mode  Figure 23. Test Setup for LMH0397 in CD Mode

Figure 23. Test Setup for LMH0397 in CD Mode The eye diagrams in this subsection show how the LMH0397 improves overall signal integrity in the data path for 75-Ω coax at SDI_IO+ when operating in EQ Mode and 100-Ω differential FR4 PCB trace at IN0± when operating in CD Mode.

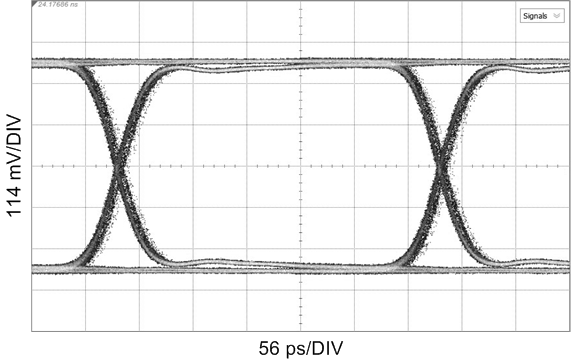

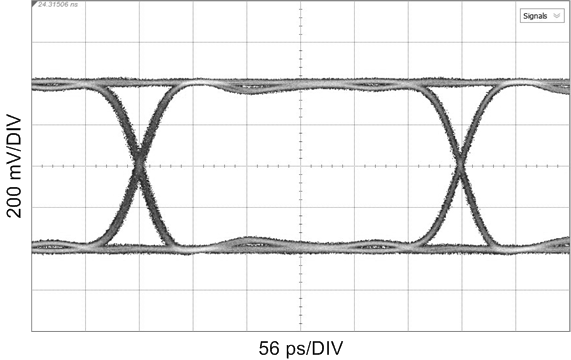

EQ Mode, measured at OUT0±

HOST_EQ0 = F, SDI_OUT_SEL = H, OUT_CTRL = F

Figure 24. 2.97 Gbps, CC = 200-m Belden 1694A, Reclocked HOST_EQ0 = F, SDI_OUT_SEL = H, OUT_CTRL = F

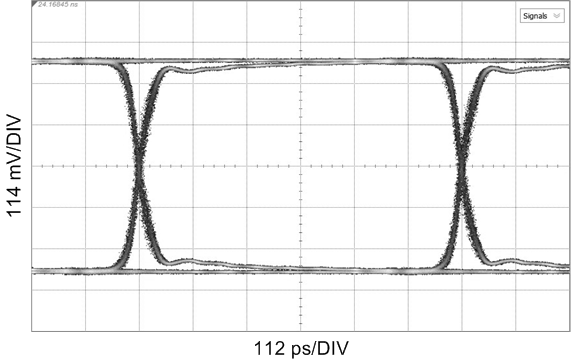

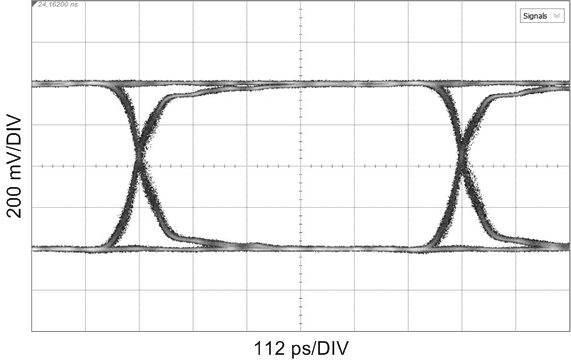

EQ Mode, measured at OUT0±

HOST_EQ0 = F, SDI_OUT_SEL = H, OUT_CTRL = F

Figure 26. 1.485 Gbps, CC = 300-m Belden 1694A, Reclocked HOST_EQ0 = F, SDI_OUT_SEL = H, OUT_CTRL = F

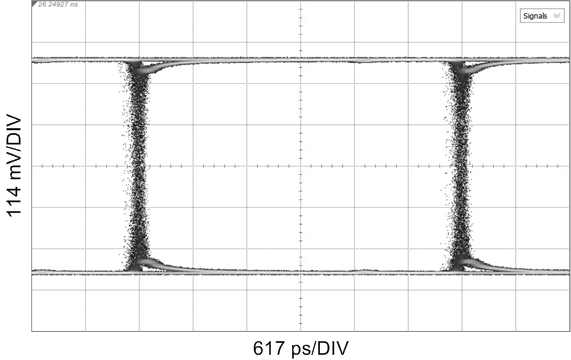

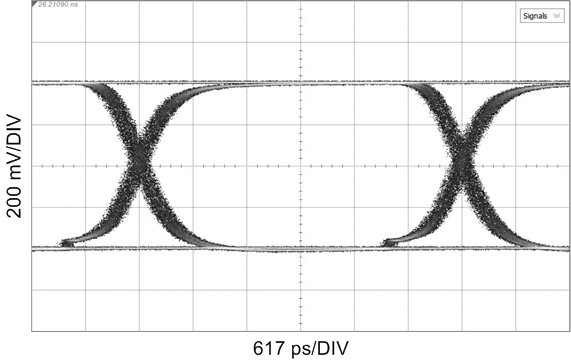

EQ Mode, measured at OUT0±

HOST_EQ0 = F, SDI_OUT_SEL = H, OUT_CTRL = F

Figure 28. 270 Mbps, CC = 600-m Belden 1694A, Reclocked HOST_EQ0 = F, SDI_OUT_SEL = H, OUT_CTRL = F

CD Mode, measured at SDI_IO+

HOST_EQ0 = F, SDI_OUT_SEL = H, OUT_CTRL = F

Figure 25. 2.97 Gbps, TL = 20" FR4, Reclocked HOST_EQ0 = F, SDI_OUT_SEL = H, OUT_CTRL = F

CD Mode, measured at SDI_IO+

HOST_EQ0 = F, SDI_OUT_SEL = H, OUT_CTRL = F

Figure 27. 1.485 Gbps, TL = 20" FR4, Reclocked HOST_EQ0 = F, SDI_OUT_SEL = H, OUT_CTRL = F

CD Mode, measured at SDI_IO+

HOST_EQ0 = F, SDI_OUT_SEL = H, OUT_CTRL = F

Figure 29. 270 Mbps, TL = 20" FR4, Reclocked HOST_EQ0 = F, SDI_OUT_SEL = H, OUT_CTRL = F