JAJSI47B April 2017 – October 2019 LMH0397

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 概要(続き)

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 4-Level Input Pins and Thresholds

- 8.3.2 Equalizer (EQ) and Cable Driver (CD) Mode Control

- 8.3.3 Input Carrier Detect

- 8.3.4 –6-dB Splitter Mode Launch Amplitude for SDI_IO+ (EQ Mode Only)

- 8.3.5 Continuous Time Linear Equalizer (CTLE)

- 8.3.6 Clock and Data (CDR) Recovery

- 8.3.7 Internal Eye Opening Monitor (EOM)

- 8.3.8 Output Function Control

- 8.3.9 Output Driver Control

- 8.3.10 Status Indicators and Interrupts

- 8.3.11 Additional Programmability

- 8.4 Device Functional Modes

- 8.5 Register Maps

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- RTV|32

サーマルパッド・メカニカル・データ

- RTV|32

発注情報

9.2.2.3 Application Curves

In EQ Mode, the LMH0397 SDI_OUT performance was measured with the test setup shown in Figure 31.

Figure 31. Test Setup for LMH0397 Loop-Through in EQ Mode

Figure 31. Test Setup for LMH0397 Loop-Through in EQ Mode The eye diagrams in this subsection show the LMH0397 75-Ω loop-through output at SDI_OUT+.

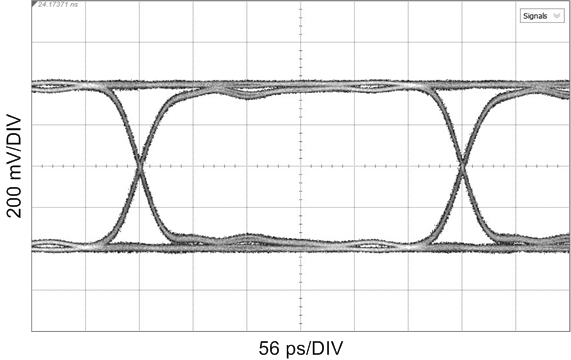

EQ Mode, measured at SDI_OUT+

HOST_EQ0 = F, SDI_OUT_SEL = L, OUT_CTRL = F

Figure 32. 2.97 Gbps, CC = 200-m Belden 1694A, Reclocked HOST_EQ0 = F, SDI_OUT_SEL = L, OUT_CTRL = F

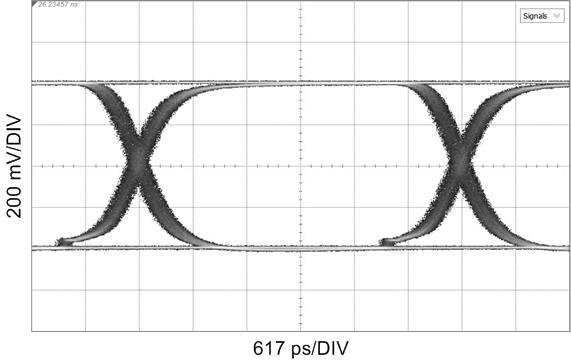

EQ Mode, measured at SDI_OUT+

HOST_EQ0 = F, SDI_OUT_SEL = L, OUT_CTRL = F

Figure 34. 270 Mbps, CC = 600-m Belden 1694A, Reclocked HOST_EQ0 = F, SDI_OUT_SEL = L, OUT_CTRL = F

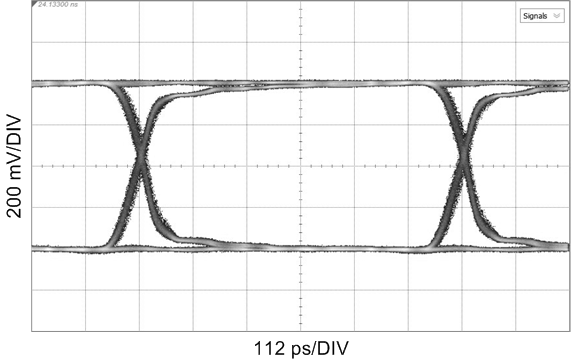

EQ Mode, measured at SDI_OUT+

HOST_EQ0 = F, SDI_OUT_SEL = L, OUT_CTRL = F

Figure 33. 1.485 Gbps, CC = 280-m Belden 1694A, Reclocked HOST_EQ0 = F, SDI_OUT_SEL = L, OUT_CTRL = F