JAJSJ18A June 2024 – October 2024 LMH1229 , LMH1239

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Pin Configuration and Functions

- 5 Specifications

-

6 Detailed Description

- 6.1 Overview

- 6.2 Functional Block Diagram

- 6.3

Feature Description

- 6.3.1 4-Level Input Pins and Thresholds

- 6.3.2 Input and Output Signal Flow Control

- 6.3.3 Input Carrier Detect

- 6.3.4 Adaptive Cable Equalizer (SDI_IN±, SDI_IN1±)

- 6.3.5 Clock and Data (CDR) Recovery

- 6.3.6 CDR Loop Bandwidth Control

- 6.3.7 Output Function Control

- 6.3.8 Output Driver Control

- 6.3.9 Debug and Diagnostic Features

- 6.4 Device Functional Modes

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- RTV|32

サーマルパッド・メカニカル・データ

- RTV|32

発注情報

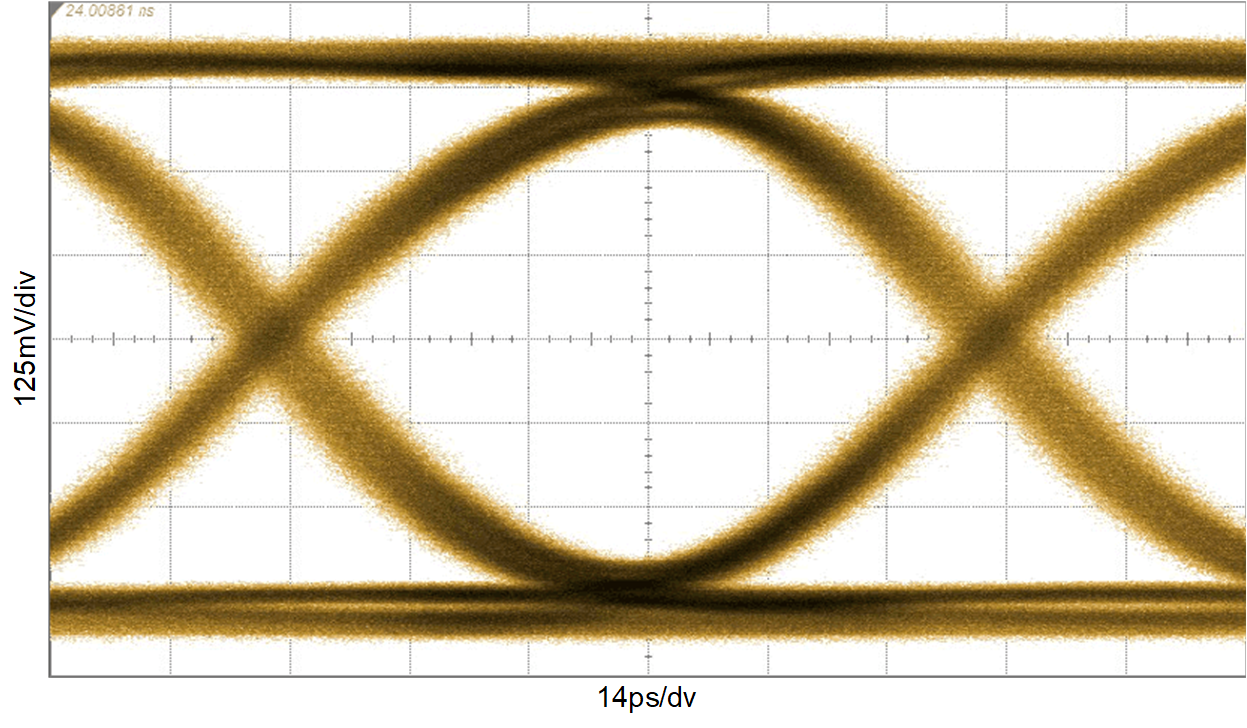

7.2.2.3 Application Curves

The LMH1239 output eye performance was measured with the test setup shown in Figure 7-12.

Figure 7-12 Test Setup for

LMH1239 PCB Output with Redundant SDI Input

Figure 7-12 Test Setup for

LMH1239 PCB Output with Redundant SDI InputThe eye diagrams measured on the LMH1239EVM in this subsection show the LMH1239 100Ω differential PCB output at OUT0± and OUT1± (Figure 7-14 - Figure 7-17).

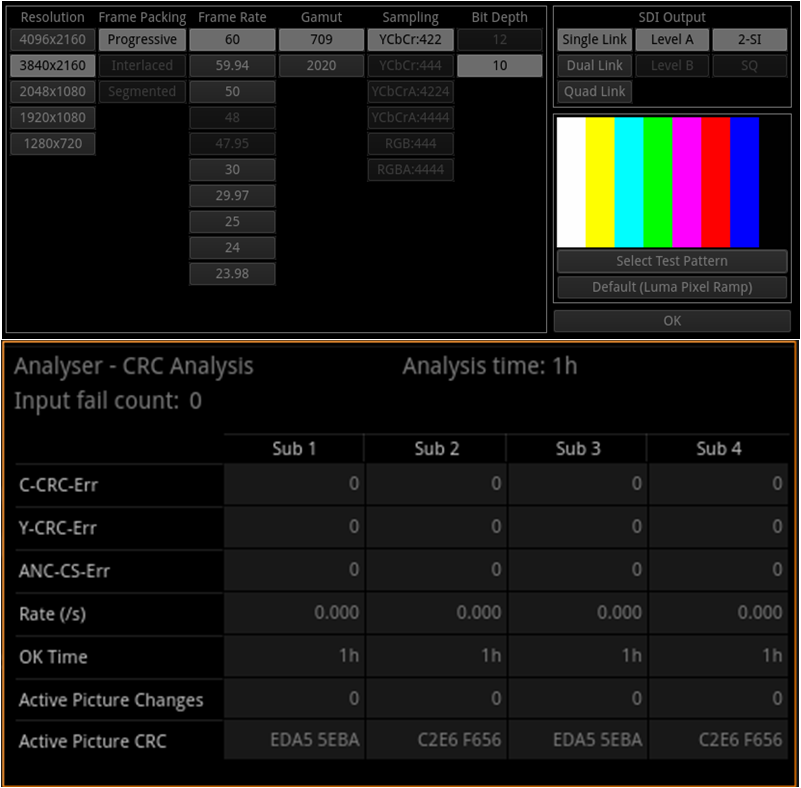

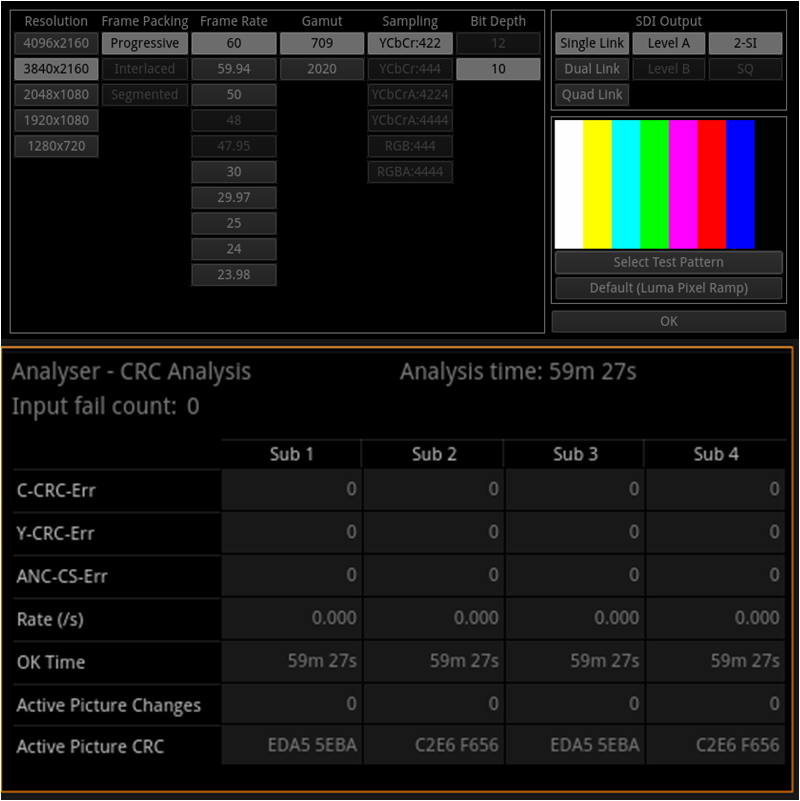

Additionally, LMH1239 BER (bit error rate) performance was measured with the test setup shown in Figure 7-13. Phabrix Qx BER results on the LMH1239EVM are shown in Figure 7-18 and Figure 7-19.

Figure 7-13 Test Setup for

LMH1239 BER Performance (OUT0±) with Redundant SDI Input

Figure 7-13 Test Setup for

LMH1239 BER Performance (OUT0±) with Redundant SDI Input

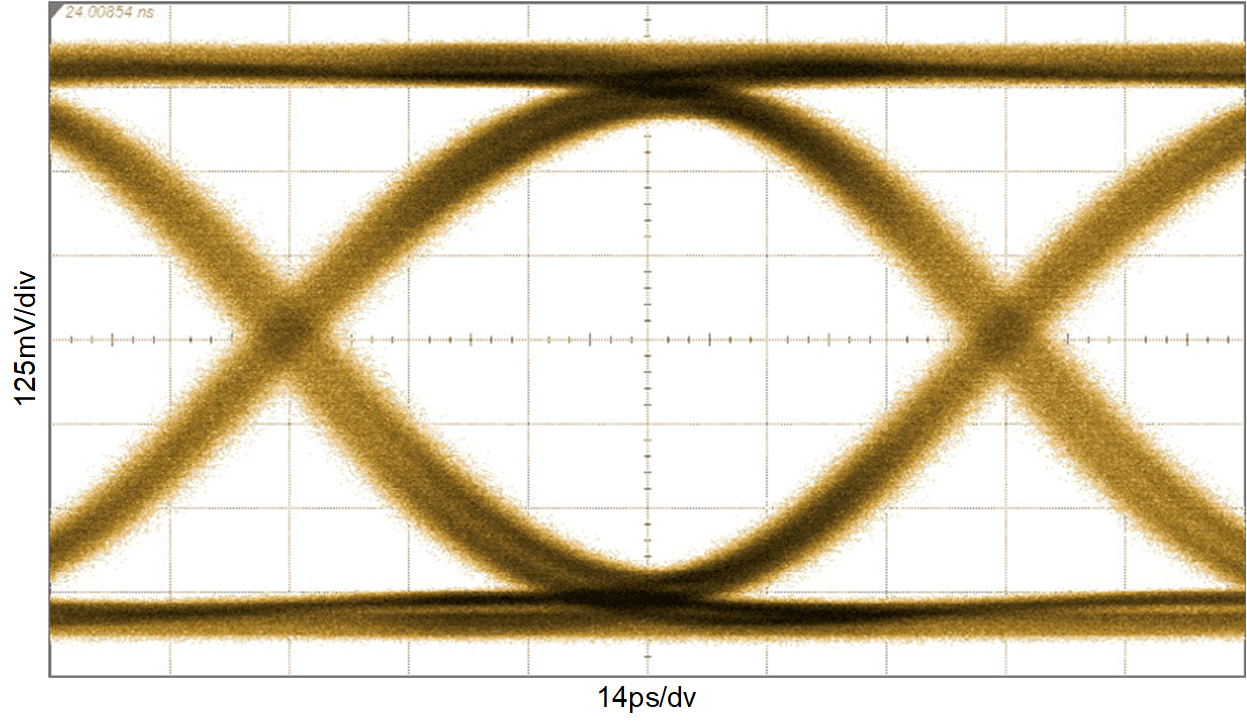

IN_MUX_SEL = F, VOD_DE

= F, SDI_OUT_SEL = H, OUT_CTRL = F

Figure 7-14 OUT0± at 11.88

Gbps (12G-SDI), CC = 100m Belden 1694A at SDI_IN+, Reclocked

IN_MUX_SEL = F, VOD_DE = F, SDI_OUT_SEL = H,

OUT_CTRL = F

Figure 7-16 OUT1± at 11.88

Gbps (12G-SDI), CC = 100m Belden 1694A at SDI_IN+, Reclocked

IN_MUX_SEL = F (SDI_IN selected), VOD_DE =

F, SDI_OUT_SEL = H, OUT_CTRL = F

Figure 7-18 OUT0± BER at

11.88Gbps (12G-SDI), CC = 100m Belden 1694A, Reclocked

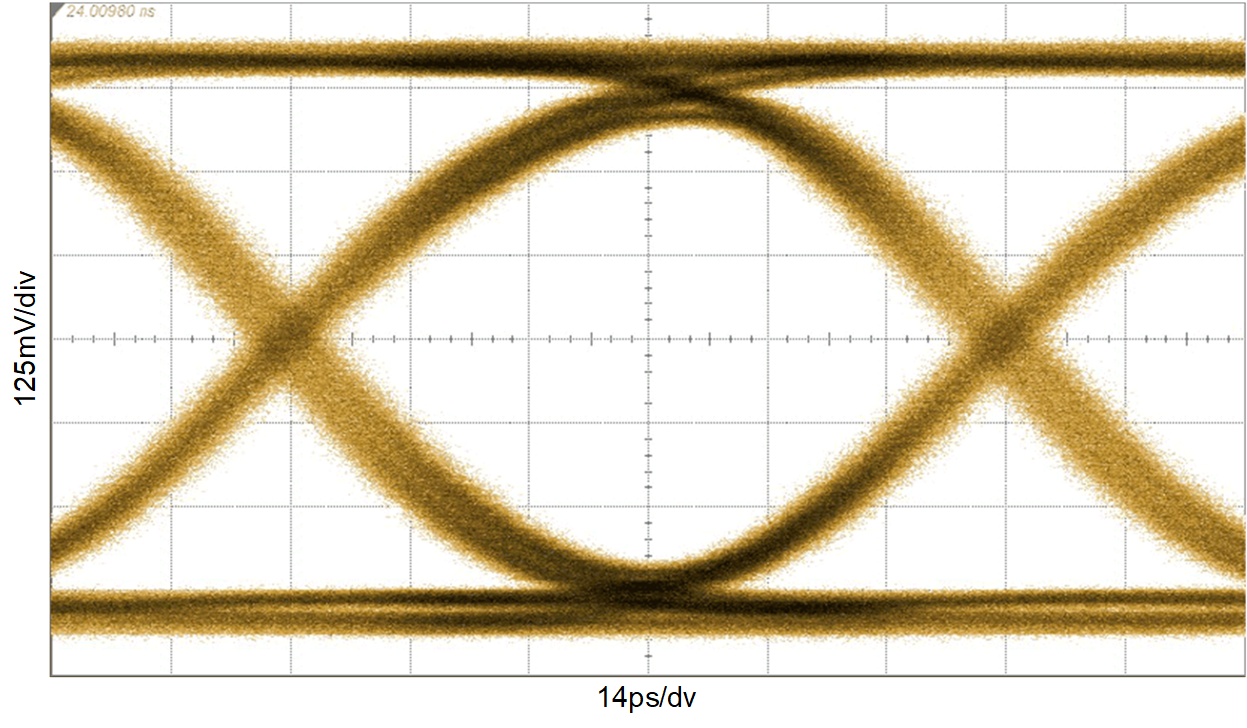

IN_MUX_SEL = L, VOD_DE = F, SDI_OUT_SEL = H,

OUT_CTRL = F

Figure 7-15 OUT0± at 11.88

Gbps (12G-SDI), CC = 100m Belden 1694A at SDI_IN1+, Reclocked

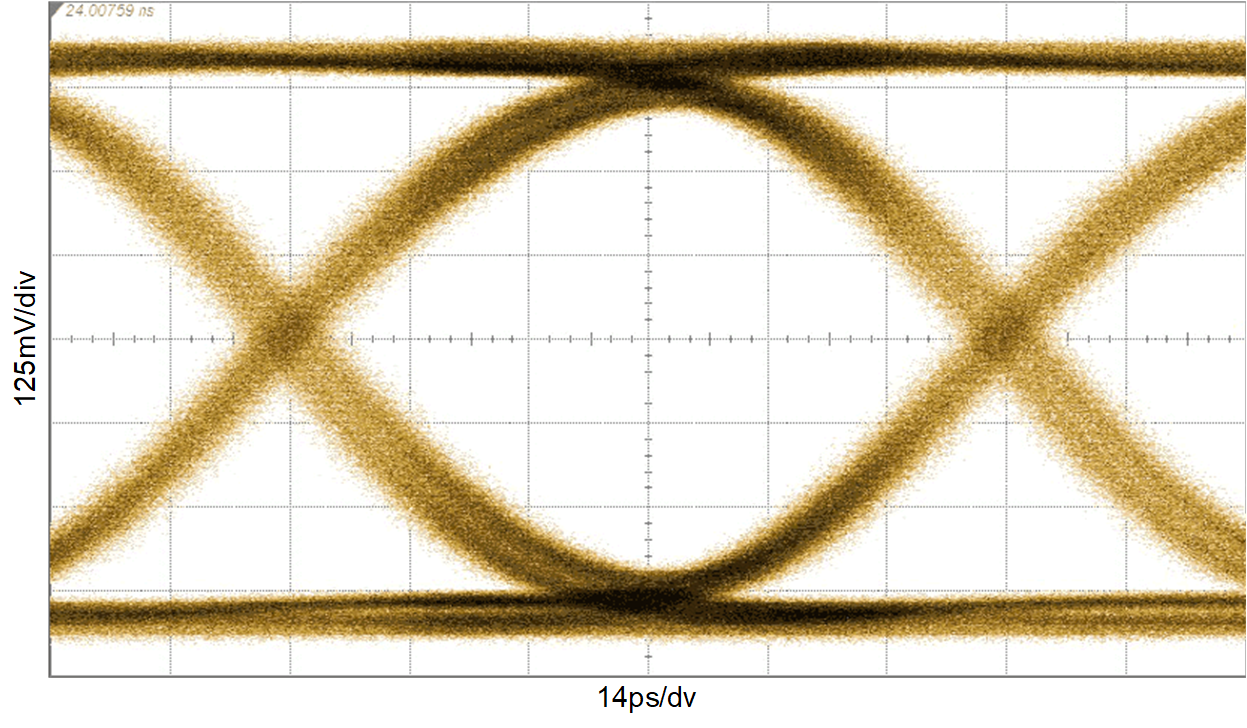

IN_MUX_SEL = L, VOD_DE = F, SDI_OUT_SEL = H,

OUT_CTRL = F

Figure 7-17 OUT1± at 11.88

Gbps (12G-SDI), CC = 100m Belden 1694A at SDI_IN1+, Reclocked

IN_MUX_SEL = L (SDI_IN1 selected), VOD_DE =

F, SDI_OUT_SEL = H, OUT_CTRL = F

Figure 7-19 OUT0± BER at

11.88Gbps (12G-SDI), CC = 100m Belden 1694A, Reclocked