JAJSCD8C August 2015 – May 2017 LP8861-Q1

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 デバイス比較表

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Electrical Characteristics

- 7.6 Internal LDO Electrical Characteristics

- 7.7 Protection Electrical Characteristics

- 7.8 Power Line FET Control Electrical Characteristics

- 7.9 Current Sinks Electrical Characteristics

- 7.10 PWM Brightness Control Electrical Characteristics

- 7.11 Boost/SEPIC Converter Characteristics

- 7.12 Logic Interface Characteristics

- 7.13 Typical Characteristics

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3 Feature Description

- 8.4 Device Functional Modes

-

9 Application and Implementation

- 9.1 Application Information

- 9.2 Typical Applications

- 10Power Supply Recommendations

- 11Layout

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- PWP|20

サーマルパッド・メカニカル・データ

- PWP|20

発注情報

8.3.1 Integrated Boost/SEPIC Converter

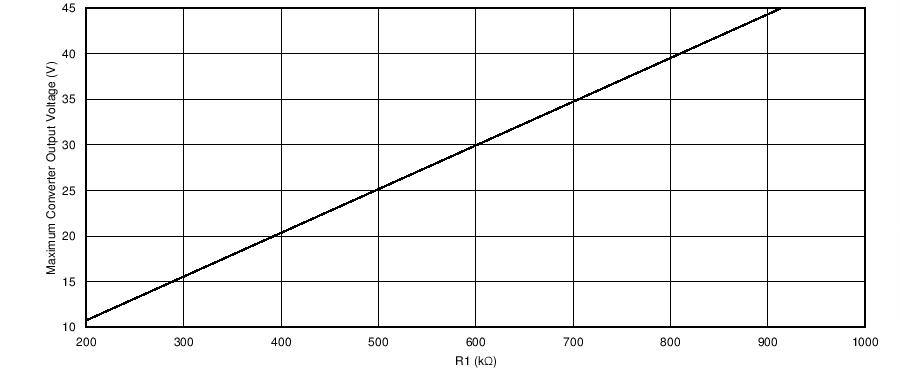

The LP8861-Q1 boost/SEPIC DC-DC converter generates supply voltage for the LEDs. The maximum output voltage VMAX BOOST is defined by an external resistive divider (R1, R2).

Maximum voltage must be chosen based on the maximum voltage required for LED strings. Recommended VMAX BOOST is about 30% higher than maximum LED string voltage. DC-DC output voltage is adjusted automatically based on LED current sink headroom voltage. Maximum, minimum, and initial boost voltages can be calculated with Equation 1:

Figure 9. Maximum Converter Output Voltage vs R1 Resistance

Figure 9. Maximum Converter Output Voltage vs R1 Resistance Alternatively, a T-divider can be used if resistance less than 100 kΩ is required for the external resistive divider. Refer to LP8861-Q1EVM Evaluation Module for details.

The converter is a current mode DC-DC converter, where the inductor current is measured and controlled with the feedback. Switching frequency is adjustable between 300 kHz and 2.2 MHz with RFSET resistor as shown in Equation 2:

where

- ƒSW is switching frequency, kHz

- RFSET is frequency setting resistor, kΩ

In most cases lower frequency has higher system efficiency. Boost parameters are chosen automatically during start-up according to the selected switching frequency (see Table 2). In boost mode a 15-pF capacitor CFB must be placed across resistor R1 when operating in 300 kHz ... 500 kHz range (see Figure 24). When operating in the 1.8-MHz...2.2-MHz range, CFB = 4.7 pF (see Figure 29).

Figure 10. Boost Block Diagram

Figure 10. Boost Block Diagram Boost clock can be driven by an external SYNC signal between 300 kHz…2.2 MHz. If the external synchronization input disappears, boost continues operation at the frequency defined by RFSET resistor. When external frequency disappears and SYNC pin level is low, boost continues operation without spread spectrum immediately. If SYNC remains high, boost continues switching with spread spectrum enabled after 256 µs.

External SYNC frequency must be 1.2…1.5 times higher than the frequency defined by the RFSET resistor. Minimum frequency setting with RFSET is 250 kHz to support minimum switching frequency with external clock frequency 300 kHz.

The optional spread-spectrum feature (±3% from central frequency, 1-kHz modulation frequency) reduces EMI noise spikes at the switching frequency and its harmonic frequencies. When external synchronization is used, spread spectrum is not available.

Table 1. Boost Synchronization Mode

| SYNC PIN STATUS | MODE |

|---|---|

| Low | Spread spectrum disabled |

| High | Spread spectrum enabled |

| 300...2200 kHz frequency | Spread spectrum disabled, external synchronization mode |

Table 2. Boost Parameters(1)

| RANGE | FREQUENCY (kHz) | TYPICAL

INDUCTANCE (µH) |

TYPICAL BOOST INPUT

AND OUTPUT CAPACITORS (µF) |

MIN SWITCH

OFF TIME (ns)(2) |

BLANK

TIME (ns) |

CURRENT

RAMP (A/s) |

CURRENT RAMP

DELAY (ns) |

|---|---|---|---|---|---|---|---|

| 1 | 300...480 | 33 | 2 × 10 (cer.) + 33 (electr.) | 150 | 95 | 24 | 550 |

| 2 | 480...1150 | 15 | 10 (cer.) +33 (electr.) | 60 | 95 | 43 | 300 |

| 3 | 1150...1650 | 10 | 3 × 10 (cer.) | 40 | 95 | 79 | 0 |

| 4 | 1650...2200 | 4.7 | 3 × 10 (cer.) | 40 | 70 | 145 | 0 |

Boost SW pin DC current is limited to 2 A (typical). To support warm start transient condition the current limit is automatically increased to 2.5 A for a short period of 1.5 seconds when a 2-A limit is reached.

NOTE

Application condition where the 2-A limit is exceeded continuously is not allowed. In this case the current limit would be 2 A for 1.5 seconds followed by 2.5-A limit for 1.5 seconds, and this 3-second period repeats.

To keep switching voltage within safe levels there is a 48-V limit comparator in the event that FB loop is broken.