JAJSTR9D May 1980 – March 2024 MC3487

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Parameter Measurement Information

- 7 Device Functional Modes

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- NS|16

- N|16

- D|16

サーマルパッド・メカニカル・データ

発注情報

3 概要

MC3487 には、ANSI TIA/EIA-422-B および ITU 勧告 V.11 の仕様を満たすように設計された、4 つの独立した差動ライン ドライバが搭載されています。各ドライバには TTL 互換の入力がバッファされており、電流の低減と負荷の最小化を実現します。

ドライバ出力は 3 ステート回路を利用して、適切な出力イネーブルが Low ロジック レベルのとき、差動出力の任意のペアで高インピーダンス状態を実現します。出力イネーブルが Low の場合、電源オンおよび電源オフ遷移時間中、内部回路は差動出力で高インピーダンス状態になります。

MC3487 は、MC3486 クワッド ライン レシーバと組み合わせたときに最適な性能を発揮するよう設計されています。このデバイスは 16 ピンのデュアル インライン パッケージで供給され、5V 単一電源で動作します。

パッケージ情報

| 部品番号 | パッケージ (1) | パッケージ サイズ(2) |

|---|---|---|

| MC3486 | D (SOIC、16) | 19.3mm × 9.4mm |

| N (PDIP、16) | 19.3mm × 9.4mm | |

| NS (SOP、16) | 10.2mm × 7.8mm |

(1) 詳細については、セクション 10 を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

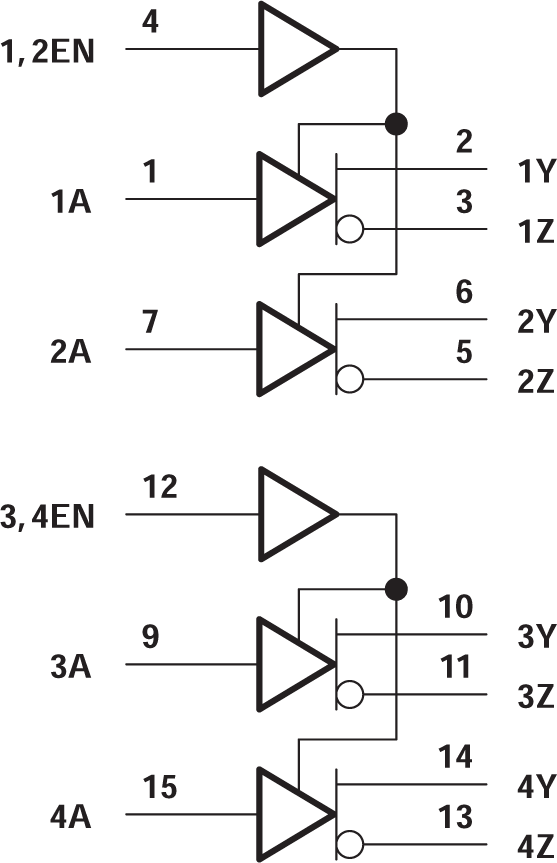

論理図 (正論理)

論理図 (正論理)