JAJSSZ3E February 1990 – February 2024 SN751177 , SN751178

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Parameter Measurement Information

- 7 Detailed Description

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- NS|16

- N|16

サーマルパッド・メカニカル・データ

発注情報

3 概要

SN751177 および SN751178 デュアル差動ドライバ / レシーバは、最大 10Mbit の速度で平衡マルチポイント バス伝送を実現するように設計されたモノリシック集積回路です。これらのデバイスは、長いバス ラインでの全二重データ通信の性能を向上させるように設計されており、ANSI 規格 TIA/EIA-422-B および TIA/EIA-485-A と ITU 勧告 V.10 および V.11 に適合しています。

SN751177 および SN751178 のドライバ出力は正と負の両方の電流を制限し、伝送バス ラインのライン フォルト状態からのサーマル シャットダウン保護が可能です。

レシーバは少なくとも 12kΩ の高入力インピーダンスを備え、入力感度は -12V~12V の同相入力電圧範囲で ±200mV、入力ヒステリシスは 50mV (標準値) です。フェイルセーフ設計により、レシーバ入力はオープンとなり、レシーバ出力は常に High になります。

SN751177 および SN751178 は −20℃~85℃で動作が規定されています。

(1) 詳細については、セクション 10を参照してください。

(2) パッケージ サイズ (長さ×幅) は公称値で、該当する場合はピンも含まれます。

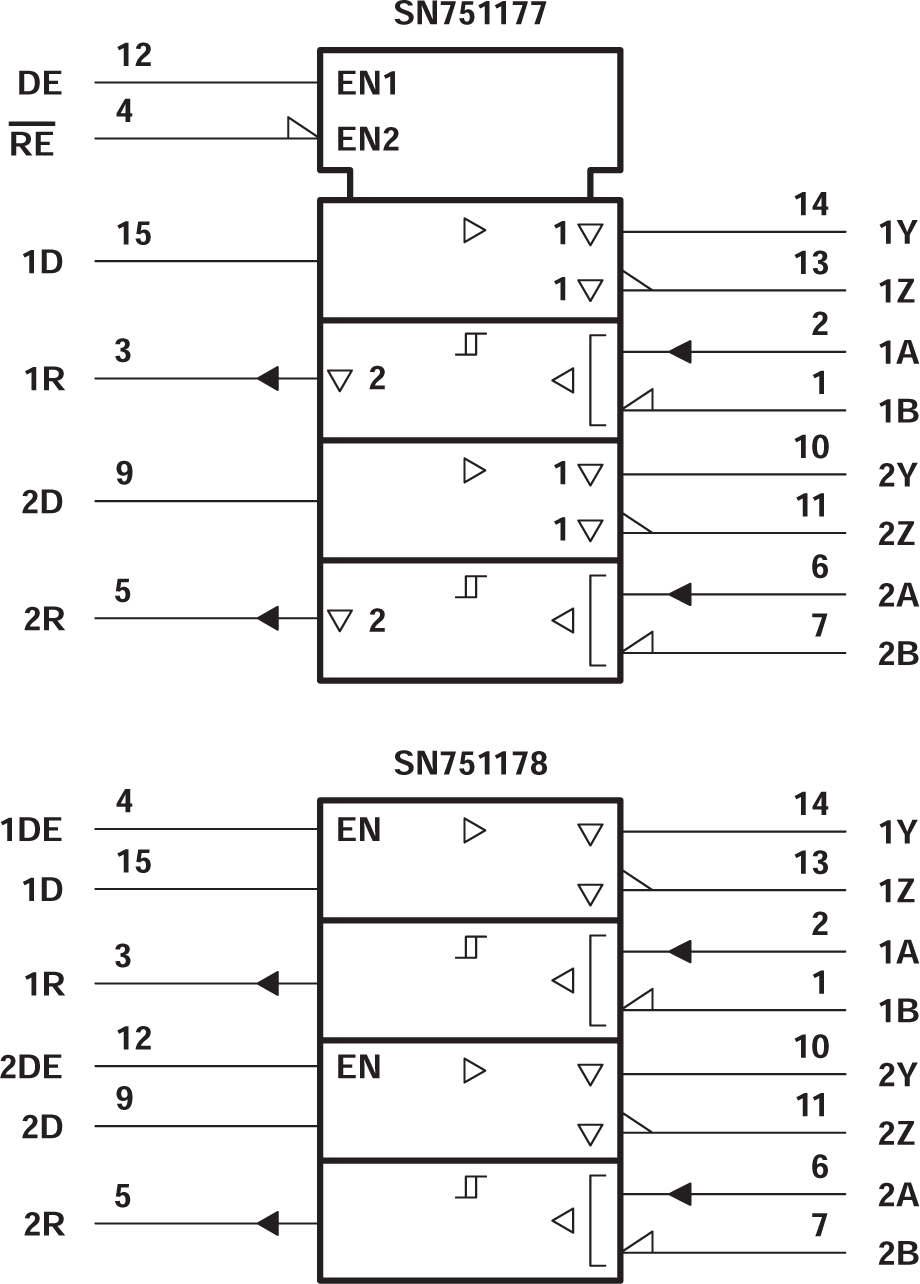

論理記号(1)

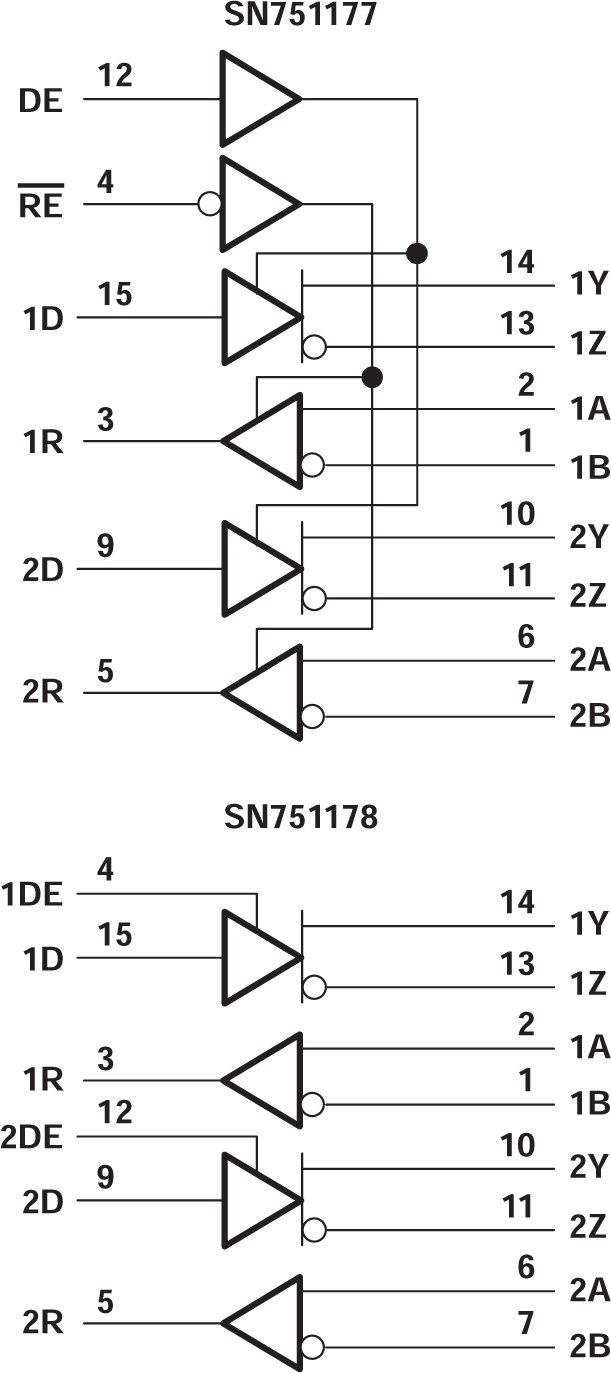

論理記号(1) 論理図 (正論理)

論理図 (正論理)†. これらの記号は ANSI/IEEE 規格 91-1984 と IEC Publication 617-12 に準拠しています。