JAJSS03F October 1993 – November 2023 SN65LBC173 , SN75LBC173

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Parameter Measurement Information

- 7 Detailed Description

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- N|16

- D|16

サーマルパッド・メカニカル・データ

発注情報

3 概要

SN65LBC173 および SN75LBC173 は、3 ステート出力を搭載したモノリシック クワッド差動ライン レシーバです。どちらも、ANSI 規格 EIA/TIA-422-B、EIA/TIA-423-B、RS-485 と ITU 勧告 V.10 および V.11 の要件を満たすように設計されています。これらのデバイスは、最大で毎秒 10 メガビット、さらにそれ以上のデータ転送速度でのバランスのとれたマルチポイント バス伝送用に最適化されています。4 つのレシーバは 2 つの論理和イネーブル入力を共有しています。1 つは High のとき、もう 1 つは Low のときアクティブです。

各レシーバは、高い入力インピーダンス、ノイズ耐性を高める入力ヒステリシス、12V~-7V の同相入力電圧範囲にわたって ±200mV の入力感度を特長としています。フェイルセーフ設計により、入力が開路の場合、出力は常に High になります。どちらのデバイスも、低消費電力、高速スイッチング、堅牢性を実現するテキサス・インスツルメンツ独自の LinBiCMOS™ テクノロジーを使用して設計されています。

これらのデバイスは、SN75LBC172 または SN75LBC174 クワッド ライン ドライバとともに使用したとき、最高のパフォーマンスを発揮します。SN65LBC173 および SN75LBC173 は、16 ピンの DIP (N) および SOIC (D) パッケージで供給されます。

SN65LBC173 は -40℃~85℃の産業用温度範囲で動作が規定されています。SN75LBC173 は 0℃~70℃の商業用温度範囲で動作が規定されています。

| 部品番号 | パッケージ (1) | パッケージ・サイズ (2) |

|---|---|---|

| SN65LBC173 SN75LBC173 |

D (SOIC、16) | 9.9mm × 6mm |

| N (PDIP、16) | 19.3mm × 9.4mm |

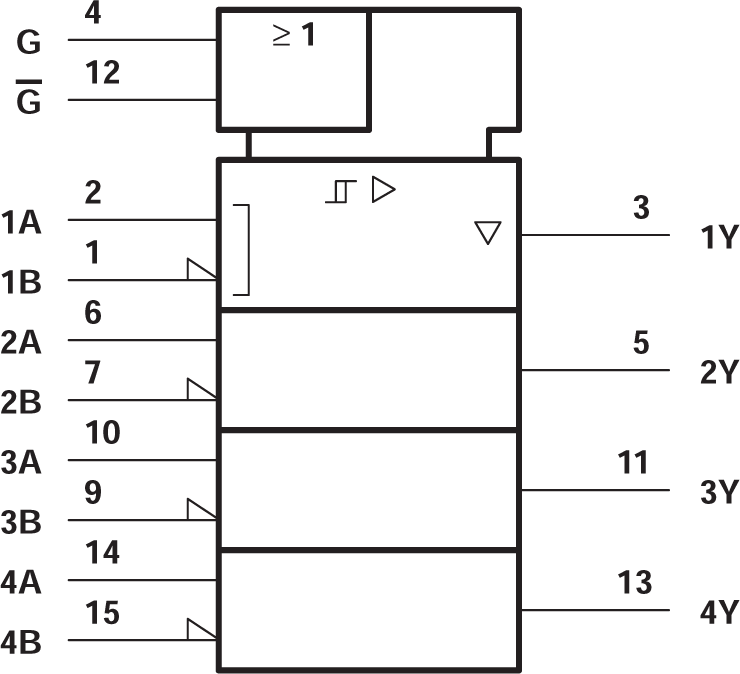

論理記号(1)

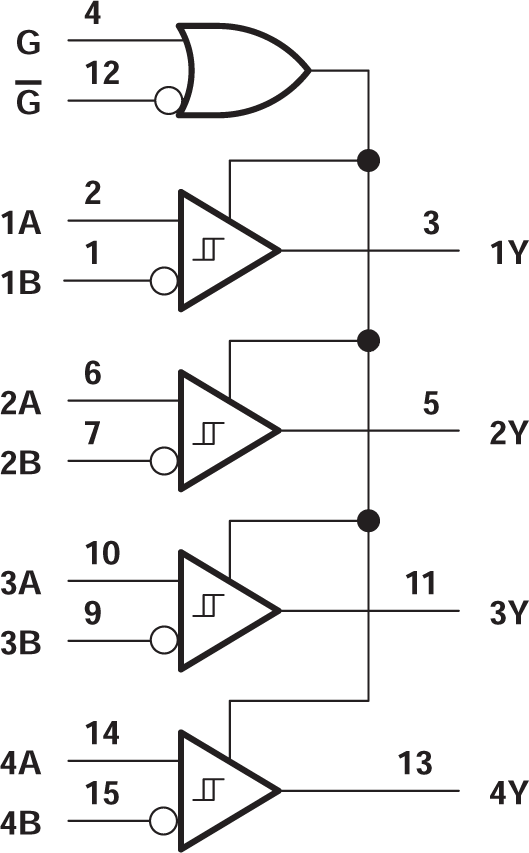

論理記号(1) 論理図 (正論理)

論理図 (正論理)