JAJSC60F April 2016 – June 2024 THS6212

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Detailed Description

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- RHF|24

サーマルパッド・メカニカル・データ

発注情報

7.2.2.2.2 Computing Total Driver Power for Line-Driving Applications

The total internal power dissipation for the THS6212 in a line-driver application is the sum of the quiescent power and the output stage power. The THS6212 holds a relatively constant quiescent current versus supply voltage—giving a power contribution that is simply the quiescent current times the supply voltage used (the supply voltage is greater than the solution given in Equation 15). The total output stage power can be computed with reference to Figure 7-8.

Figure 7-8 Output

Stage Power Model

Figure 7-8 Output

Stage Power ModelThe two output stages used to drive the load of Figure 7-5 are shown as an H-Bridge in Figure 7-8. The average current drawn from the supply into this H-Bridge and load is the peak current in the load given by Equation 13 divided by the crest factor (CF) for the signal modulation. This total power from the supply is then reduced by the power in RT, leaving the power dissipated internal to the drivers in the four output-stage transistors. That power is simply the target line power used in Equation 8 plus the power lost in the matching elements (RM). In the following examples, a perfect match is targeted giving the same power in the matching elements as in the load. The output stage power is then set by Equation 17.

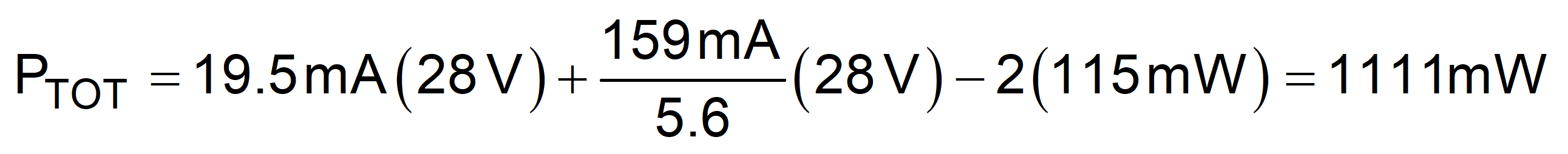

The total amplifier power is then given by Equation 18:

For the example given by Figure 7-4, the peak current is 159 mA for a signal that requires a crest factor of 5.6 with a target line power of 20.5 dBm into a 100-Ω load (115 mW).

With a typical quiescent current of 19.5mA and a nominal supply voltage of ±14V, the total internal power dissipation for the solution of Figure 7-4 is given by Equation 19: