JAJSJO7E December 2002 – August 2020 THS7530

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- PWP|14

サーマルパッド・メカニカル・データ

- PWP|14

発注情報

11.1 Layout Guidelines

The THS7530 device is available in a thermally-enhanced PowerPAD™ package. Figure 11-1 shows the recommended number of vias and thermal land size recommended for best performance. Thermal vias connect the thermal land to internal or external copper planes and should have a drill diameter sufficiently small so that the via hole is effectively plugged when the barrel of the via is plated with copper. This plug is needed to prevent wicking the solder away from the interface between the package body and the thermal land on the surface of the board during solder reflow. The experiments conducted jointly with Solectron Texas indicate that a via drill diameter of 0.33 mm (13 mils, or .013 in) or smaller works well when 1-ounce copper is plated at the surface of the board and simultaneously plating the barrel of the via. If the thermal vias are not plugged when the copper plating is performed, then a solder mask material should be used to cap the vias with a dimension equal to the via diameter + 0.1 mm minimum. This prevents the solder from being wicked through the thermal via and potentially creating a solder void in the region between the package bottom and the thermal land on the surface of the PCB.

Figure 11-1 Recommended Thermal Land Size and Thermal Via Patterns (Dimensions in mm)

Figure 11-1 Recommended Thermal Land Size and Thermal Via Patterns (Dimensions in mm)See TI's Technical Brief titled, PowerPAD™ Thermally Enhanced Package (SLMA002) for a detailed discussion of the PowerPAD™ package, its dimensions, and recommended use.

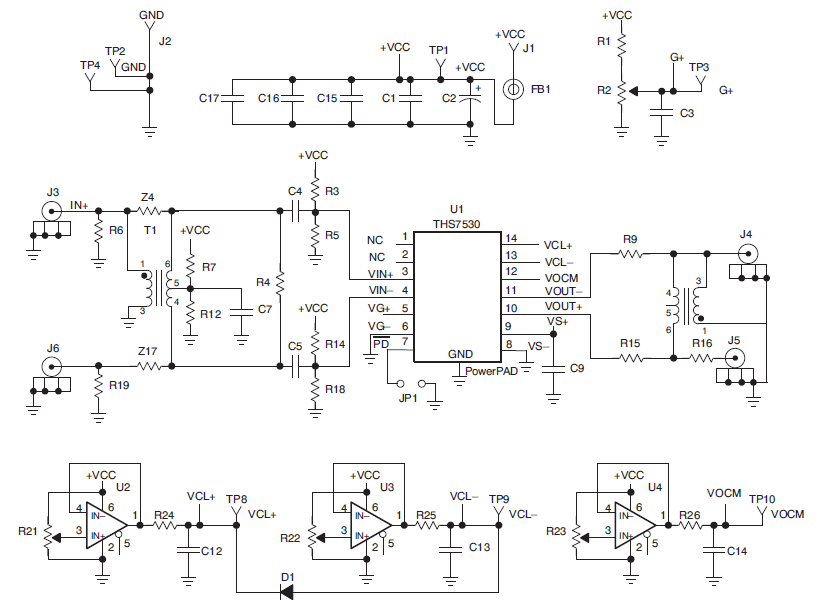

Figure 11-2 EVM Schematic

Figure 11-2 EVM Schematic