JAJSGH6B November 2018 – August 2024 TLV1704-SEP

PRODUCTION DATA

6.3.1 Comparator Inputs

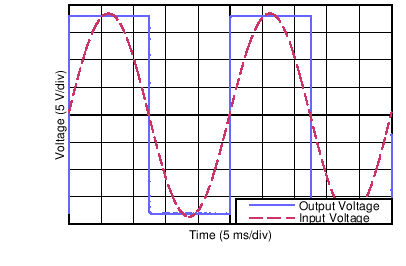

The TLV1704-SEP device is a rail-to-rail input comparator, with an input common-mode range that includes the supply rails. The TLV1704-SEP device is designed to prevent phase inversion when the input pins exceed the supply voltage. Figure 6-1 shows the TLV1704-SEP device response when input voltages exceed the supply, resulting in no phase inversion.

Figure 6-1 No Phase Inversion: Comparator Response to Input Voltage (Propagation Delay Included)

Figure 6-1 No Phase Inversion: Comparator Response to Input Voltage (Propagation Delay Included)