JAJSEY2Z July 1996 – June 2024 TLV431 , TLV431A , TLV431B

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Parameter Measurement Information

- 7 Detailed Description

- 8 Applications and Implementation

- 9 Device and Documentation Support

- 10Revision History

- 11Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- D|8

- DBZ|3

- DBV|5

- PK|3

- LP|3

サーマルパッド・メカニカル・データ

- PK|3

発注情報

5.7 Electrical Characteristics for TLV431B

at 25°C free-air temperature (unless otherwise

noted)

| PARAMETER | TEST CONDITIONS | TLV431B | UNIT | |||||

|---|---|---|---|---|---|---|---|---|

| MIN | TYP | MAX | ||||||

| VREF | Reference voltage | VKA = VREF, IK=10mA | TA = 25°C | 1.234 | 1.24 | 1.246 | V | |

| TA = full range (1) (see Figure 6-1) | TLV431BC | 1.227 | 1.253 | |||||

| TLV431BI | 1.224 | 1.259 | ||||||

| TLV431BQ | 1.221 | 1.265 | ||||||

| VREF(dev) | VREF deviation over full temperature range (2) | VKA = VREF , IK = 10mA (1) (see Figure 6-1) | TLV431BC | 4 | 12 | mV | ||

| TLV431BI | 6 | 20 | ||||||

| TLV431BQ | 11 | 31 | ||||||

|

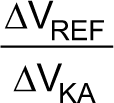

Ratio of VREF change in cathode voltage change | VKA = VREF to 6V, IK = 10mA (see Figure 6-2) | -1.5 | -2.7 | mV/V | |||

| Iref | Reference terminal current | IK = 10mA, R1 = 10kΩ, R2 = open (see Figure 6-2) | 0.1 | 0.5 | µA | |||

| Iref(dev) | Iref deviation over full temperature range (2) | IK = 10mA, R1 =10kΩ, R2 = open (3) (see Figure 6-2) | TLV431BC | 0.05 | 0.3 | µA | ||

| TLV431BI | 0.1 | 0.4 | ||||||

| TLV431BQ | 0.15 | 0.5 | ||||||

| IK(min) | Minimum cathode current for regulation | VKA = VREF (see Figure 6-1) | 55 | 100 | µA | |||

| IK(off) | Off-state cathode current | VREF = 0, VKA = 6V (see Figure 6-3) | 0.001 | 0.1 | µA | |||

| |zKA| | Dynamic impedance (4) | VKA = VREF, f ≤ 1kHz, IK = 0.1mA to 15mA (see Figure 6-1) | 0.25 | 0.4 | Ω | |||

(1) Full temperature ranges are

–40°C to 125°C for TLV431Q, –40°C to 85°C for TLV431I, and 0°C to 70°C for

TLV431C.

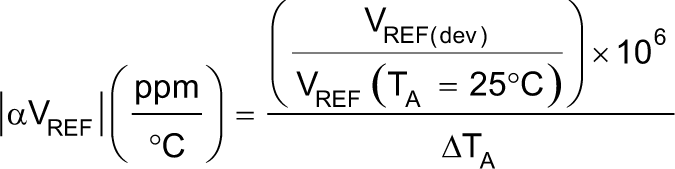

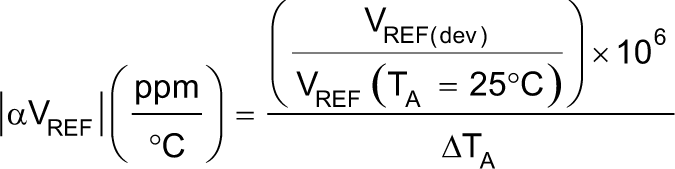

(2) The deviation parameters

VREF(dev) and Iref(dev) are defined as the differences between the maximum and

minimum values obtained over the rated temperature range. The average full-range

temperature coefficient of the reference input voltage, αVREF, is

defined as:

where ΔTA is the rated operating free-air temperature range of

the device. αVREF can be positive or negative, depending on whether

minimum VREF or maximum VREF, respectively, occurs at the

lower temperature.

where ΔTA is the rated operating free-air temperature range of

the device. αVREF can be positive or negative, depending on whether

minimum VREF or maximum VREF, respectively, occurs at the

lower temperature.

(3) Full temperature ranges are

–40°C to 125°C for TLV431Q, –40°C to 85°C for TLV431I, and 0°C to 70°C for

TLV431C.

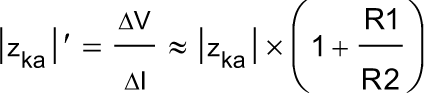

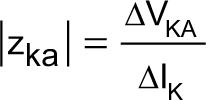

(4) dynamic impedance is defined

as  . When

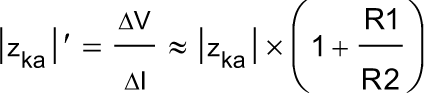

the device is operating with two external resistors (see Figure 6-2), the total dynamic impedance of the circuit is defined as:

. When

the device is operating with two external resistors (see Figure 6-2), the total dynamic impedance of the circuit is defined as:

. When

the device is operating with two external resistors (see Figure 6-2), the total dynamic impedance of the circuit is defined as:

. When

the device is operating with two external resistors (see Figure 6-2), the total dynamic impedance of the circuit is defined as: