SLVSBI7C July 2012 – April 2015 TPS22908

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Options

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

- 9 Detailed Description

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

12 Layout

12.1 Layout Guidelines

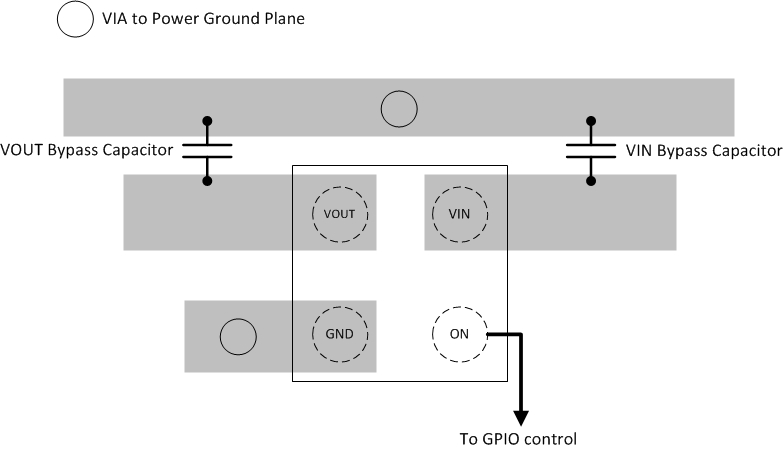

For best performance, VIN, VOUT, and GND traces should be as short and wide as possible to help minimize the parasitic electrical effects. To be most effective, the input and output capacitors should be placed close to the device to minimize the effects that parasitic trace inductances may have on normal operation.

12.3 Thermal Considerations

For higher reliability, the maximum IC junction temperature, TJ(max), should be restricted to 125˚C under normal operating conditions. Junction temperature is directly proportional to power dissipation in the device and the two are related by:

Equation 5. TJ = TA + RθJA × PD

where

- TJ = Junction temperature of the device

- TA = Ambient temperature

- PD = Power dissipation inside the device

- RθJA = Junction to ambient thermal resistance. See Thermal Information for more information. This parameter is highly dependent on board layout.