SLVSCZ3 March 2015 TPS24770 , TPS24771 , TPS24772

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Simplified Schematic

- 5 Revision History

- 6 Device Comparison Table

- 7 Pin Configuration and Functions

- 8 Specifications

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3

Feature Description

- 9.3.1 Enable and Over-voltage Protection

- 9.3.2 Current Limit and Power Limit during Start-up

- 9.3.3 Two Level Protection During Regular Operation

- 9.3.4 Dual Timer (TFLT and TINR)

- 9.3.5 3 Options for Response to a Fast Trip

- 9.3.6 Using Soft Start - IHGATE and TINR Considerations

- 9.3.7 Analog Current Monitor

- 9.3.8 Power Good Flag

- 9.3.9 Fault Reporting

- 9.4 Device Functional Modes

-

10Application and Implementation

- 10.1 Application Information

- 10.2

Typical Application

- 10.2.1 12 V, 100 A, 5,500 µF Analog Hot Swap Design

- 10.2.2 Design Requirements

- 10.2.3

Detailed Design Procedure

- 10.2.3.1 Select RSNS and VSNS,CL Setting

- 10.2.3.2 Selecting the Fast Trip Threshold and Filtering

- 10.2.3.3 Selecting the Hot Swap FET(s)

- 10.2.3.4 Select Power Limit

- 10.2.3.5 Set Fault Timer

- 10.2.3.6 Check MOSFET SOA

- 10.2.3.7 Choose Under Voltage and Over Voltage Settings

- 10.2.3.8 Selecting C1 and COUT

- 10.2.3.9 Adding CENHS

- 10.2.3.10 Selecting D1 and D2

- 10.2.3.11 Checking Stability

- 10.2.3.12 Compute Tolerances

- 10.2.4 Application Curves

- 10.2.5

240 VA Application Using CSD16415Q5B

- 10.2.5.1 Design Requirements

- 10.2.5.2 Theory of Operations

- 10.2.5.3

Design Procedure

- 10.2.5.3.1

Select VSNS,CL, RSNS, and RSET Setting

- 10.2.5.3.1.1 Select RPOW and RIMON

- 10.2.5.3.1.2 Selecting the Hot Swap FET(s)

- 10.2.5.3.1.3 Keeping MOSFET within SOA During Normal Start-up

- 10.2.5.3.1.4 Choose Fault Timer

- 10.2.5.3.1.5 Choose Under Voltage and Over Voltage Settings

- 10.2.5.3.1.6 Selecting CIN and COUT

- 10.2.5.3.1.7 Selecting D1 and D2

- 10.2.5.3.1.8 Adding CENHS

- 10.2.5.3.1.9 Stability Considerations

- 10.2.5.3.1

Select VSNS,CL, RSNS, and RSET Setting

- 10.2.5.4 Application Curves

- 10.2.6 240 VA Application Using CSD17573Q5B

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- RGE|24

サーマルパッド・メカニカル・データ

- RGE|24

発注情報

1 Features

- 2.5V to 18V Bus Operation (30V abs max)

- Programmable Protection Settings:

- Current Limit: ±5% at 10mV

- Fast Trip: ±10% at 20mV

- Programmable FET SOA Protection

- Programable Response Time for Fast Trip

- Dual Timer (Inrush/Fault)

- Analog Current Monitor (1% at 25mV)

- Programmable UV and OV

- Status Flags for Faults and Power Good

- 4mm × 4mm 24-pin QFN

- 70 = Latch, 71 = Retry, 72 = Fast Latch Off

2 Applications

- Enterprise Storage

- Enterprise Server

- Networking Cards

- 240 VA Applications

3 Description

The TPS2477x is a high performance analog Hot Swap Controller for 2.5 V to 18 V systems. The precise and highly programmable protection settings of the TPS2477x aid the design of high power high availability systems where isolating faults is critical.

Programmable current limit, fast shut down, and fault timer protect the load and supply during fault conditions such as a hot - short. The fast shutdown threshold and response time can be tuned to ensure a fast response to real faults, while avoiding nuisance trips. Programmable Safe Operating Area (SOA) protection and the inrush timer keep the MOSFET safe under all conditions. After asserting power good, TPS2477x acts as a circuit breaker and runs the fault timer during over current events, but doesn’t current limit. It shuts down after the fault timer expires. Two independent timers (inrush/fault) allow the user to customize protection based on system requirements.

Finally, the flexibility of the TPS2477x aid Hot Swap design for the 240 VA requirement and a design example is shown in the datasheet.

Device Information(1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|---|---|---|

| TPS24770 TPS24771 TPS24772 |

RGE (24) | 4.00 mm x 4.00 mm |

- For all available packages, see the orderable addendum at the end of the data sheet.

4 Simplified Schematic

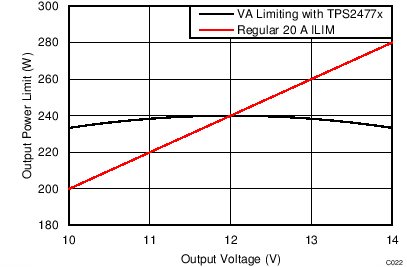

Limiting Output Power to 240VA,

20 A ILIM vs TPS2477x Implementation