SLVSEZ5A July 2020 – December 2020 TPS25814

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Recommended Capacitance

- 6.5 Thermal Information

- 6.6 Power Supply Characteristics

- 6.7 Power Consumption

- 6.8 PP_5V Power Switch Characteristics

- 6.9 Power Path Supervisory

- 6.10 CC Cable Detection Parameters

- 6.11 CC VCONN Parameters

- 6.12 Thermal Shutdown Characteristics

- 6.13 Input/Output (I/O) Characteristics

- 6.14 BC1.2 Characteristics

- 6.15 I2C Requirements and Characteristics

- 6.16 Typical Characteristics

- 7 Parameter Measurement Information

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3 Feature Description

- 8.4 Device Functional Modes

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- RSM|32

サーマルパッド・メカニカル・データ

- RSM|32

発注情報

11.4 Routing and View Placement

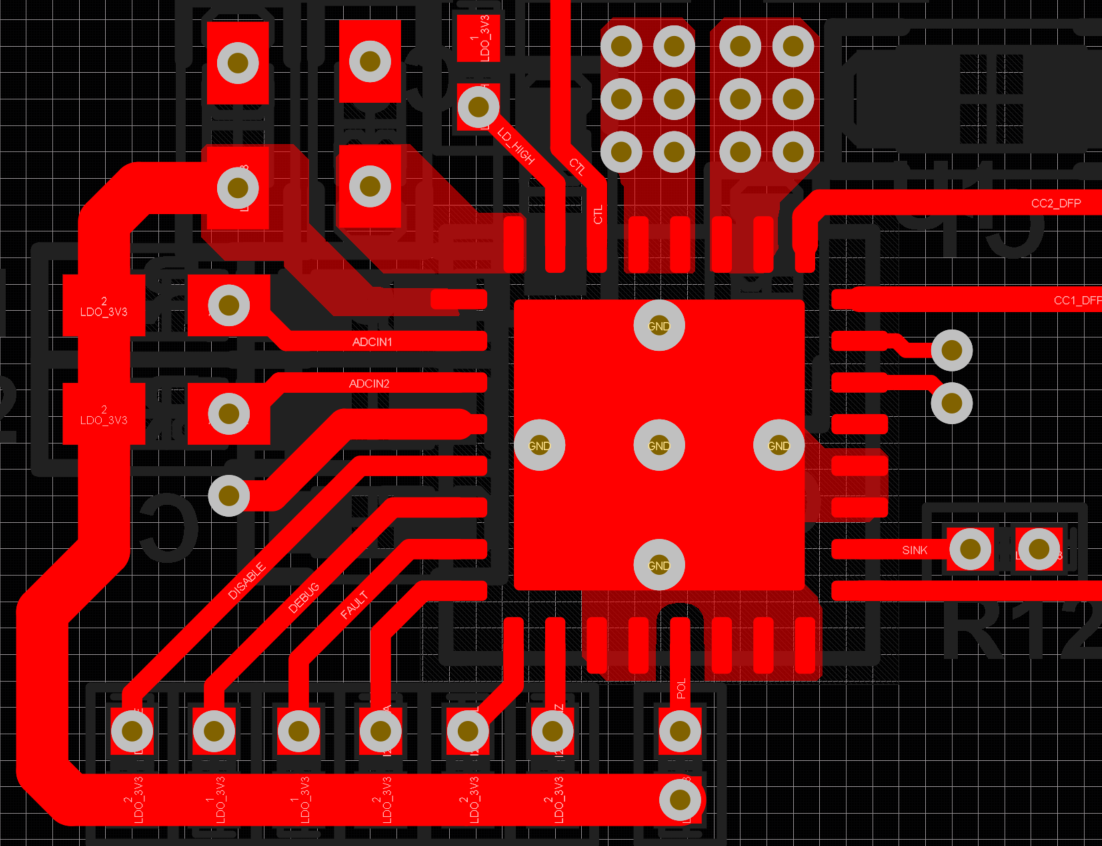

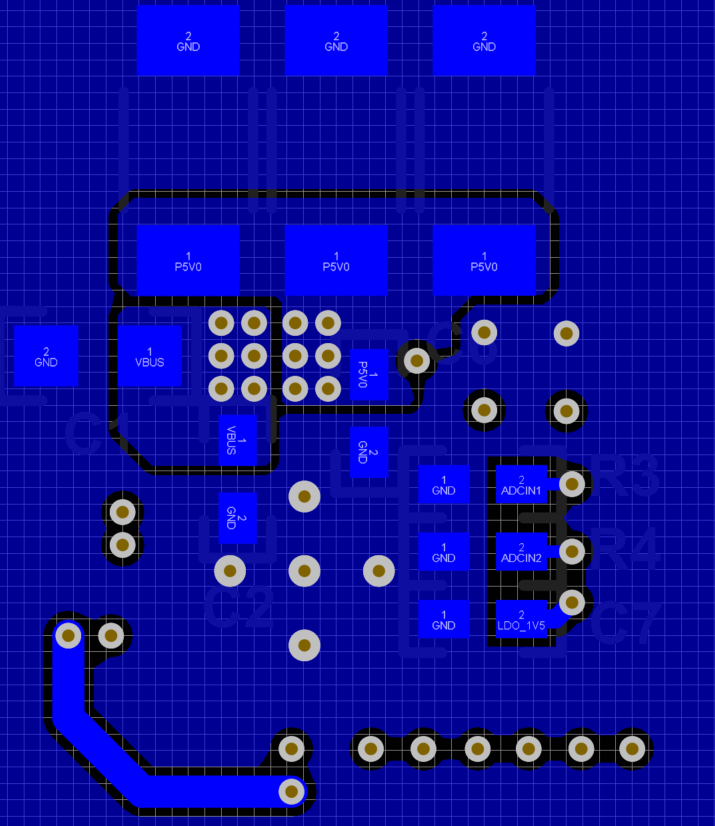

On the top side, create pours for PP5V and VBUS. Connect PP5V and VBUS from the top layer to the bottom layer using at least 6, 8-mil hole and 16-mil diameter vias. See Figure 11-6 for the recommended via sizing. The via placement and copper pours are highlighted in Figure 11-7.

Figure 11-6 Recommended Minimum Via

Sizing

Figure 11-6 Recommended Minimum Via

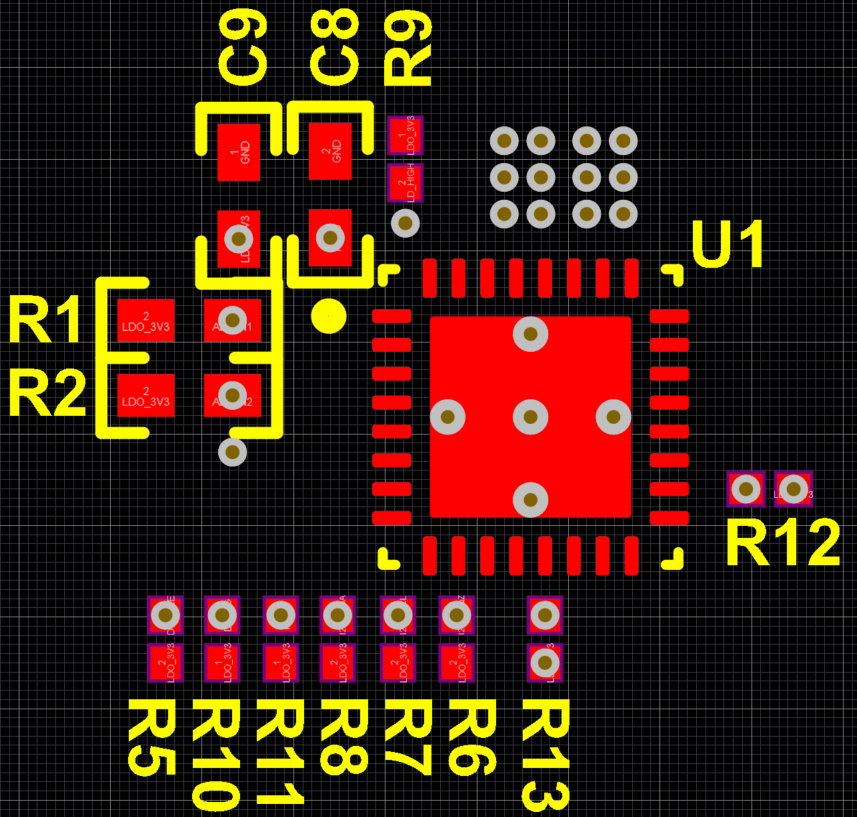

Sizing Figure 11-7 Via Placement - Top

Layer

Figure 11-7 Via Placement - Top

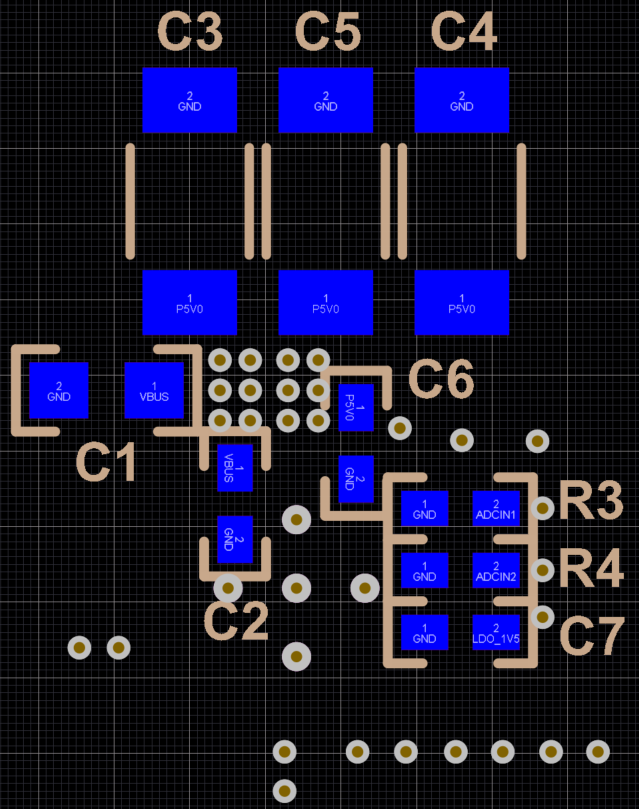

Layer Figure 11-8 Via Placement - Bottom

Layer

Figure 11-8 Via Placement - Bottom

Layer Figure 11-9 Routing - Top

Layer

Figure 11-9 Routing - Top

Layer Figure 11-10 Routing - Bottom

Layer

Figure 11-10 Routing - Bottom

Layer