JAJSDE0A June 2017 – February 2024 TPS549B22

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Pin Configuration and Functions

- 5 Specifications

-

6 Detailed Description

- 6.1 Overview

- 6.2 Functional Block Diagram

- 6.3 Feature Description

- 6.4 Device Functional Modes

- 6.5 Programming

-

7 Register Maps

- 7.1 OPERATION Register (address = 1h)

- 7.2 ON_OFF_CONFIG Register (address = 2h)

- 7.3 CLEAR FAULTS (address = 3h)

- 7.4 WRITE PROTECT (address = 10h)

- 7.5 STORE_DEFAULT_ALL (address = 11h)

- 7.6 RESTORE_DEFAULT_ALL (address = 12h)

- 7.7 CAPABILITY (address = 19h)

- 7.8 VOUT_MODE (address = 20h)

- 7.9 VOUT_COMMAND (address = 21h)

- 7.10 VOUT_MARGIN_HIGH (address = 25h) ®

- 7.11 VOUT_MARGIN_LOW (address = 26h)

- 7.12 STATUS_BYTE (address = 78h)

- 7.13 STATUS_WORD (High Byte) (address = 79h)

- 7.14 STATUS_VOUT (address = 7Ah)

- 7.15 STATUS_IOUT (address = 7Bh)

- 7.16 STATUS_CML (address = 7Eh)

- 7.17 MFR_SPECIFIC_00 (address = D0h)

- 7.18 MFR_SPECIFIC_01 (address = D1h)

- 7.19 MFR_SPECIFIC_02 (address = D2h)

- 7.20 MFR_SPECIFIC_03 (address = D3h)

- 7.21 MFR_SPECIFIC_04 (address = D4h)

- 7.22 MFR_SPECIFIC_06 (address = D6h)

- 7.23 MFR_SPECIFIC_07 (address = D7h)

- 7.24 MFR_SPECIFIC_44 (address = FCh)

-

8 Application and Implementation

- 8.1 Application Information

- 8.2

Typical Applications

- 8.2.1 TPS549B22 1.5-V to 18-V Input, 1-V Output, 25-A Converter

- 8.2.2 Design Requirements

- 8.2.3

Detailed Design Procedure

- 8.2.3.1 Custom Design With WEBENCH® Tools

- 8.2.3.2 Switching Frequency Selection

- 8.2.3.3 Inductor Selection

- 8.2.3.4 Output Capacitor Selection

- 8.2.3.5 Input Capacitor Selection

- 8.2.3.6 Bootstrap Capacitor Selection

- 8.2.3.7 BP Pin

- 8.2.3.8 R-C Snubber and VIN Pin High-Frequency Bypass

- 8.2.3.9 Optimize Reference Voltage (VSEL)

- 8.2.3.10 MODE Pin Selection

- 8.2.3.11 ADDR Pin Selection

- 8.2.3.12 Overcurrent Limit Design

- 8.2.4 Application Curves

- 8.3 Power Supply Recommendations

- 8.4 Layout

- 9 Device and Documentation Support

- 10Revision History

- 11Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- RVF|40

サーマルパッド・メカニカル・データ

- RVF|40

発注情報

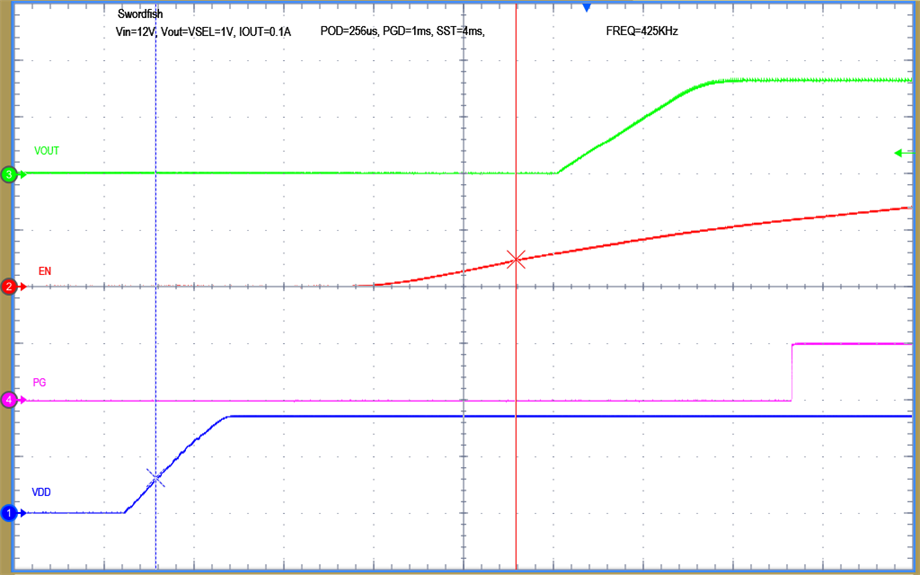

6.5.1.4 Application Workaround to Support 4-ms and 8-ms SS Settings

To properly design for 4 ms and 8 ms SS settings, additional application consideration is needed. The recommended application workaround to support the 4-ms and 8-ms soft-start settings is to ensure sufficient time delay between the VDD and EN_UVLO signals. The minimum delay between the rising maximum VDD UVLO level and the minimum turn on threshold of EN_UVLO is at least TDELAY_MIN.

where

- K = 9 ms/V for SS setting of 4 ms

- K = 18 ms/V for SS setting of 8 ms

- VREF is the internal reference voltage programmed by VSEL pin strap

For example, if SS setting is 4 ms and VREF = 1 V, program the minimum delay at least 9 ms; if SS setting is 8 ms, the minimum delay must be programmed at least 18 ms. See Figure 6-5 and Figure 6-6 for detailed timing requirement. Because TPS549B22 is a PMBus device, the end user has the option of programming power-on delay (POD) as another workaround. Be sure to follow the same calculation to determine the needed POD (see Section 7.18 and Table 7-17 for detailed information).

Figure 6-5 Proper Sequencing of VDD and EN_UVLO to Support the use of 4-ms SS Setting

Figure 6-5 Proper Sequencing of VDD and EN_UVLO to Support the use of 4-ms SS Setting Figure 6-6 Minimum Delay Between VDD and EN_UVLO to Support the use of 4-ms and 8-ms SS settings

Figure 6-6 Minimum Delay Between VDD and EN_UVLO to Support the use of 4-ms and 8-ms SS settingsThe workaround/consideration described previously is not required for SS settings of 1 ms and 2 ms.