JAJSJW7D September 2019 – June 2024 TPS54J060

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Pin Configuration and Functions

- 5 Specifications

-

6 Detailed Description

- 6.1 Overview

- 6.2 Functional Block Diagram

- 6.3

Feature Description

- 6.3.1 Enable and Internal LDO

- 6.3.2 Split Rail and External LDO

- 6.3.3 Output Voltage Setting

- 6.3.4 Soft Start and Output-Voltage Tracking

- 6.3.5 Frequency and Operation Mode Selection

- 6.3.6 D-CAP3™ Control Mode

- 6.3.7 Current Sense and Positive Overcurrent Protection

- 6.3.8 Low-side FET Negative Current Limit

- 6.3.9 Power Good

- 6.3.10 Overvoltage and Undervoltage Protection

- 6.3.11 Out-Of-Bounds Operation (OOB)

- 6.3.12 Output Voltage Discharge

- 6.3.13 UVLO Protection

- 6.3.14 Thermal Shutdown

- 6.4 Device Functional Modes

-

7 Application and Implementation

- 7.1 Application Information

- 7.2

Typical Application

- 7.2.1 Design Requirements

- 7.2.2

Detailed Design Procedure

- 7.2.2.1 Choose the Switching Frequency and Operation Mode (MODE Pin)

- 7.2.2.2 Choose the Output Inductor (L)

- 7.2.2.3 Set the Current Limit (TRIP)

- 7.2.2.4 Choose the Output Capacitors (COUT)

- 7.2.2.5 Choose the Input Capacitors (CIN)

- 7.2.2.6 Feedback Network (FB Pin)

- 7.2.2.7 Soft Start Capacitor (SS/REFIN Pin)

- 7.2.2.8 EN Pin Resistor Divider

- 7.2.2.9 VCC Bypass Capacitor

- 7.2.2.10 BOOT Capacitor

- 7.2.2.11 Series BOOT Resistor and RC Snubber

- 7.2.2.12 PGOOD Pullup Resistor

- 7.2.3 Application Curves

- 7.3 Power Supply Recommendations

- 7.4 Layout

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Ordering Information

3 概要

TPS54J060 デバイスは、適応型オン時間 D-CAP3 制御モードを搭載した、高効率、小型の同期整流式降圧コンバータです。スペースに制約のある電源システムで使いやすく、外部部品数が少なくて済みます。

このデバイスは、高性能の内蔵 MOSFET、高精度 (±1%) の 900mV 基準電圧、–40℃~+125℃の接合部温度範囲を特長としています。競争力のある機能として、非常に少ない外付け部品点数、高速な負荷過渡応答、精密な負荷レギュレーションとライン レギュレーション、自動スキップまたは FCCM モード動作、可変ソフト スタート制御、外部補償を使わない全セラミック コンデンサ設計のサポートが挙げられます。

TPS54J060 は、14 ピンの QFN パッケージで供給されます。

(1) 詳細については、セクション 10 を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

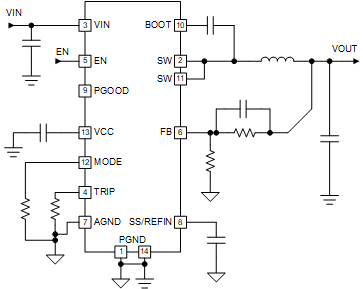

概略回路図

概略回路図 代表的な効率 (VOUT = 1.8V、fSW = 600kHz)

代表的な効率 (VOUT = 1.8V、fSW = 600kHz)