-

TPS56x210A、4.5V~17V入力、2A、3A同期整流降圧型レギュレータ 8ピンSOT-23パッケージ JAJSCP3 November 2016 TPS562210A , TPS563210A

PRODUCTION DATA.

-

TPS56x210A、4.5V~17V入力、2A、3A同期整流降圧型レギュレータ 8ピンSOT-23パッケージ

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11デバイスおよびドキュメントのサポート

- 12メカニカル、パッケージ、および注文情報

- 重要なお知らせ

TPS56x210A、4.5V~17V入力、2A、3A同期整流降圧型レギュレータ 8ピンSOT-23パッケージ

1 特長

- TPS562210A: 133mΩおよび80mΩ FET内蔵2Aコンバータ

- TPS563210A: 68mΩおよび39mΩ FET内蔵3Aコンバータ

- D-CAP2™モード制御による高速過渡応答

- 高度な Eco-mode™パルス・スキップ

- 入力電圧範囲: 4.5V~17V

- 出力電圧範囲: 0.76V~7V

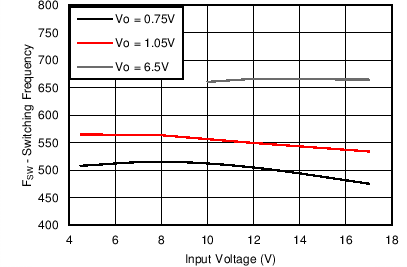

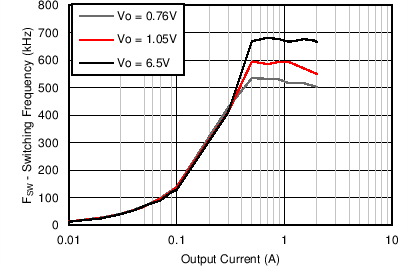

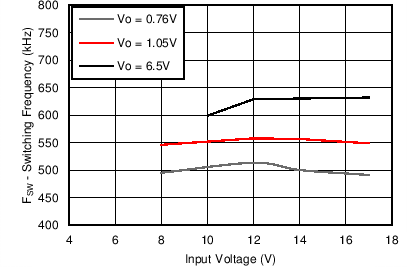

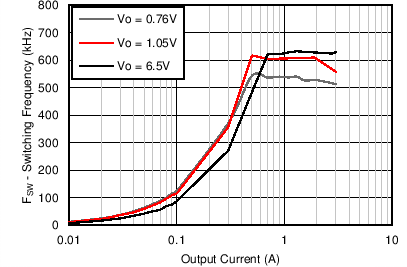

- 650kHzのスイッチング周波数

- 低いシャットダウン電流:10µA未満

- 帰還電圧精度: 1%(25℃)

- プリバイアス出力電圧からのスタートアップ

- サイクルごとの過電流制限

- ヒカップ・モード低電圧保護

- 非ラッチ型のOVP、UVLO、およびTSD保護

- 調整可能なソフト・スタート

- パワー・グッド出力

2 アプリケーション

- デジタル・テレビ用電源

- 高精細 Blu-ray Disc™プレーヤー

- ネットワーク・ホーム・ターミナル

- デジタル・セットトップ・ボックス(STB)

3 概要

TPS562210AおよびTPS563210Aは、シンプルで使いやすい2A、3A同期整流降圧型コンバータで、8ピンSOT-23パッケージで供給されます。

最小の外部部品数で動作し、スタンバイ電流が小さくなるよう最適化されています。

これらのスイッチ・モード電源(SMPS)デバイスは、D-CAP2™モード制御を採用し、高速の過渡応答を実現します。また、特殊ポリマーなどの低ESR(等価直列抵抗)出力コンデンサと超低ESRセラミック・コンデンサの両方を外部補償部品なしでサポートします。

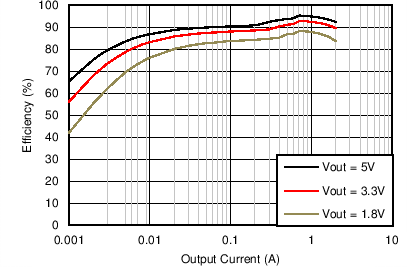

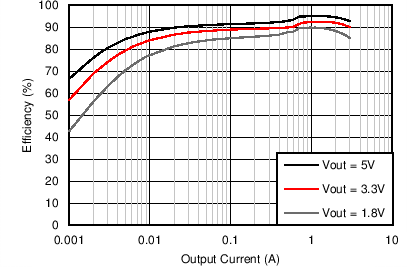

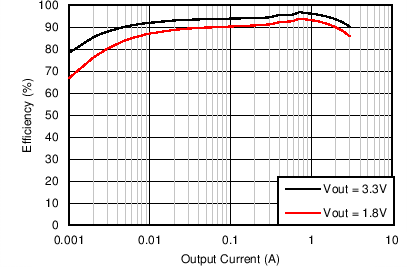

高度なEco-mode™を搭載し、軽負荷動作中も高い効率を維持します。TPS562210AおよびTPS563210Aは、8ピン1.6 × 2.9 (mm) SOT (DDF)パッケージで供給され、–40℃~85℃の周囲温度範囲で仕様が規定されています。

製品情報(1)

| 発注型番 | パッケージ | 本体サイズ(公称) |

|---|---|---|

| TPS562210A | DDF(8) | 1.60mm×2.90mm |

| TPS563210A |

- 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

Spacer

Spacer

概略回路図

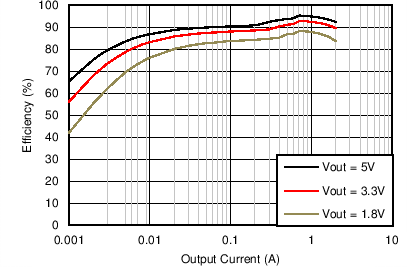

効率

4 改訂履歴

| 日付 | 改訂内容 | 注 |

|---|---|---|

| 2016年11月 | * | 初版 |

5 Pin Configuration and Functions

Pin Functions

| PIN | DESCRIPTION | |

|---|---|---|

| NAME | NO. | |

| GND | 1 | Ground pin Source terminal of low-side power NFET as well as the ground terminal for controller circuit. Connect sensitive VFB to this GND at a single point. |

| SW | 2 | Switch node connection between high-side NFET and low-side NFET. |

| VIN | 3 | Input voltage supply pin. The drain terminal of high-side power NFET. |

| PG | 4 | Power good open drain output |

| SS | 5 | Soft-start control. An external capacitor should be connected to GND. |

| VFB | 6 | Converter feedback input. Connect to output voltage with feedback resistor divider. |

| EN | 7 | Enable input control. Active high and must be pulled up to enable the device. |

| VBST | 8 | Supply input for the high-side NFET gate drive circuit. Connect 0.1 µF capacitor between VBST and SW pins. |

6 Specifications

6.1 Absolute Maximum Ratings

TJ = -40°C to 150°C (unless otherwise noted) (1)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| Input voltage range | VIN, EN | –0.3 | 19 | V |

| VBST | –0.3 | 25 | V | |

| VBST (10 ns transient) | –0.3 | 27.5 | V | |

| VBST (vs SW) | –0.3 | 6.5 | V | |

| VFB, PG | –0.3 | 6.5 | V | |

| SS | –0.3 | 5.5 | V | |

| SW | –2 | 19 | V | |

| SW (10 ns transient) | –3.5 | 21 | V | |

| Operating junction temperature, TJ | –40 | 150 | °C | |

| Storage temperature, Tstg | –55 | 150 | °C | |

6.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±2000 | V |

| Charged device model (CDM), per JEDEC specification JESD22-C101(2) | ±500 | V | ||

6.3 Recommended Operating Conditions

TJ = –40°C to 150°C (unless otherwise noted)| MIN | MAX | UNIT | |||

|---|---|---|---|---|---|

| VIN | Supply input voltage range | 4.5 | 17 | V | |

| VI | Input voltage range | VBST | –0.1 | 23 | V |

| VBST (10 ns transient) | –0.1 | 26 | V | ||

| VBST(vs SW) | –0.1 | 6 | V | ||

| EN | –0.1 | 17 | V | ||

| VFB, pg | –0.1 | 5.5 | V | ||

| SS | –0.1 | 5 | V | ||

| SW | –1.8 | 17 | V | ||

| SW (10 ns transient) | –3.5 | 20 | V | ||

| TA | Operating free-air temperature | –40 | 85 | °C | |

6.4 Thermal Information

| THERMAL METRIC(1) | TPS562210A | TPS563210A | UNIT | |

|---|---|---|---|---|

| DDF (8 PINS) | ||||

| RθJA | Junction-to-ambient thermal resistance | 106.1 | 87.0 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 49.1 | 41.6 | °C/W |

| RθJB | Junction-to-board thermal resistance | 10.9 | 14.6 | °C/W |

| ψJT | Junction-to-top characterization parameter | 8.6 | 4.7 | °C/W |

| ψJB | Junction-to-board characterization parameter | 10.8 | 14.6 | °C/W |

6.5 Electrical Characteristics

over operating free-air temperature range, VIN = 12 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| SUPPLY CURRENT | ||||||

| IVIN | Operating – non-switching supply current | VIN current, TA = 25°C, EN = 5V, VFB = 0.8 V | 190 | 290 | µA | |

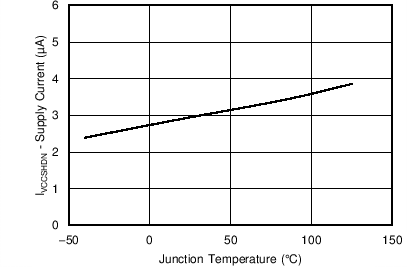

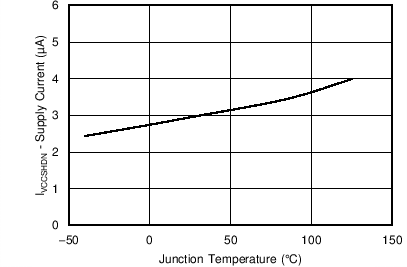

| IVINSDN | Shutdown supply current | VIN current, TA = 25°C, EN = 0 V | 3.0 | 10 | µA | |

| LOGIC THRESHOLD | ||||||

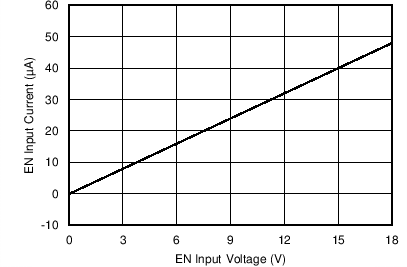

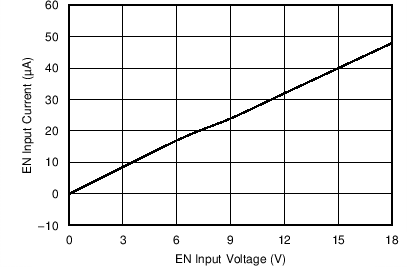

| VENH | EN high-level input voltage | EN | 1.6 | V | ||

| VENL | EN low-level input voltage | EN | 0.6 | V | ||

| REN | EN pin resistance to GND | VEN = 12 V | 225 | 450 | 900 | kΩ |

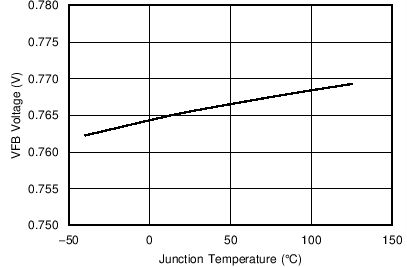

| VFB VOLTAGE AND DISCHARGE RESISTANCE | ||||||

| VFBTH | VFB threshold voltage TPS562210A | TA = 25°C, VO = 1.05 V, IO = 10 mA, Eco-mode™ operation | 772 | mV | ||

| VFB threshold voltage TPS562210A and TPS563210A | TA = 25°C, VO = 1.05 V | 758 | 765 | 772 | mV | |

| TA = 0°C to 85°C, VO = 1.05 V(1) | 753 | 777 | ||||

| TA = -40°C to 85°C, VO = 1.05 V(1) | 751 | 779 | ||||

| IVFB | VFB input current | VFB = 0.8 V, TA = 25°C | 0 | ±0.1 | µA | |

| MOSFET | ||||||

| RDS(on)h | High side switch resistance | TA = 25°C, VBST – SW = 5.5 V, TPS562210A | 133 | mΩ | ||

| TA = 25°C, VBST – SW = 5.5 V, TPS563210A | 68 | |||||

| RDS(on)l | Low side switch resistance | TA = 25°C, TPS562210A | 80 | mΩ | ||

| TA = 25°C, TPS563210A | 39 | |||||

| CURRENT LIMIT | ||||||

| IOCL | Current limit(1) | DC current, VOUT = 1.05 V , L1 = 2.2 µH, TPS562210A | 2.5 | 3.2 | 4.3 | A |

| DC current, VOUT = 1.05 V , L1 = 1.5 µH, TPS563210A | 3.5 | 4.2 | 5.3 | |||

| THERMAL SHUTDOWN | ||||||

| TSDN | Thermal shutdown threshold(1) | Shutdown temperature | 155 | °C | ||

| Hysteresis | 35 | |||||

| SOFT START | ||||||

| ISS | SS charge current | VSS = 1.2 V | 4.2 | 6 | 7.8 | µA |

| POWER GOOD | ||||||

| VTHPG | PG threshold | VFB rising (Good) | 85% | 90% | 95% | |

| VFB falling (Fault) | 85% | |||||

| IPG | PG sink current | PG = 0.5 V | 0.5 | 1 | mA | |

| OUTPUT UNDERVOLTAGE AND OVERVOLTAGE PROTECTION | ||||||

| VOVP | Output OVP threshold | OVP Detect | 125%xVfbth | |||

| VUVP | Output UVP threshold | Hiccup detect | 65%x Vfbth |

|||

| tHiccupOn | Hiccup Power On Time | Relative to soft start time | 1 | cycle | ||

| tHiccupOff | Hiccup Power Off Time | Relative to soft start time | 7 | cycles | ||

| UVLO | ||||||

| UVLO | UVLO threshold | Wake up VIN voltage | 3.45 | 3.75 | 4.05 | V |

| Hysteresis VIN voltage | 0.13 | 0.32 | 0.55 | |||

6.6 Timing Requirements

| MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| ON-TIME TIMER CONTROL | ||||||

| tON | On time | VIN = 12 V, VO = 1.05 V | 150 | ns | ||

| tOFF(MIN) | Minimum off time | TA = 25°C, VFB = 0.5 V | 260 | 310 | ns | |

6.7 Typical Characteristics

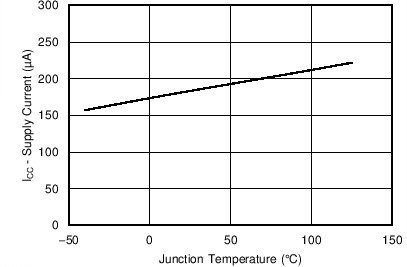

6.7.1 TPS562210A Characteristics

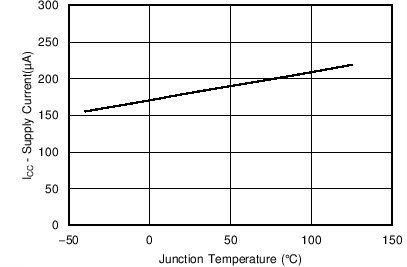

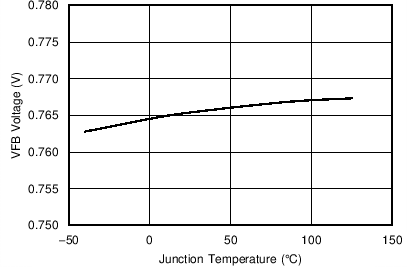

VIN = 12 V (unless otherwise noted)

| VI = 5 V |

6.7.2 TPS563210A Characteristics

VIN = 12V (unless otherwise noted)

| VI = 5 V |

7 Detailed Description

7.1 Overview

The TPS562210A and TPS563210A are 2-A, 3-A synchronous step-down converters. The proprietary D-CAP2™ mode control supports low ESR output capacitors such as specialty polymer capacitors and multi-layer ceramic capacitors without complex external compensation circuits. The fast transient response of D-CAP2™ mode control can reduce the output capacitance required to meet a specific level of performance.

7.2 Functional Block Diagram

7.3 Feature Description

7.3.1 The Adaptive On-Time Control and PWM Operation

The main control loop of the TPS562210A and TPS563210A are adaptive on-time pulse width modulation (PWM) controller that supports a proprietary D-CAP2™ mode control. The D-CAP2™ mode control combines adaptive on-time control with an internal compensation circuit for pseudo-fixed frequency and low external component count configuration with both low ESR and ceramic output capacitors. It is stable even with virtually no ripple at the output.

At the beginning of each cycle, the high-side MOSFET is turned on. This MOSFET is turned off after internal one shot timer expires. This one shot duration is set proportional to the converter input voltage, VIN, and inversely proportional to the output voltage, VO, to maintain a pseudo-fixed frequency over the input voltage range, hence it is called adaptive on-time control. The one-shot timer is reset and the high-side MOSFET is turned on again when the feedback voltage falls below the reference voltage. An internal ramp is added to reference voltage to simulate output ripple, eliminating the need for ESR induced output ripple from D-CAP2™ mode control.

7.3.2 Soft Start and Pre-Biased Soft Start

The TPS562210A and TPS563210A have adjustable soft-start. When the EN pin becomes high, the SS charge current (ISS) begins charging the capacitor which is connected from the SS pin to GND (CSS). Smooth control of the output voltage is maintained during start up. The equation for the soft start time, Tss is shown in Equation 1.

where VFBTH is 0.765 V and Iss is 6 µA.

If the output capacitor is pre-biased at startup, the devices initiate switching and start ramping up only after the internal reference voltage becomes greater than the feedback voltage VFB. This scheme ensures that the converters ramp up smoothly into regulation point.

7.3.3 Power Good

The power good output, PG is an open drain output. The power good function becomes active after 1.7 times soft-start time. When the output voltage becomes within –10% of the target value, internal comparators detect power good state and the power good signal becomes high. If the feedback voltage goes under 15% of the target value, the power good signal becomes low.

7.3.4 Current Protection

The output over-current limit (OCL) is implemented using a cycle-by-cycle valley detect control circuit. The switch current is monitored during the OFF state by measuring the low-side FET drain to source voltage. This voltage is proportional to the switch current. To improve accuracy, the voltage sensing is temperature compensated.

During the on time of the high-side FET switch, the switch current increases at a linear rate determined by VIN, VOUT, the on-time and the output inductor value. During the on time of the low-side FET switch, this current decreases linearly. The average value of the switch current is the load current IOUT. If the monitored current is above the OCL level, the converter maintains low-side FET on and delays the creation of a new set pulse, even the voltage feedback loop requires one, until the current level becomes OCL level or lower. In subsequent switching cycles, the on-time is set to a fixed value and the current is monitored in the same manner. If the over current condition exists consecutive switching cycles, the internal OCL threshold is set to a lower level, reducing the available output current. When a switching cycle occurs where the switch current is not above the lower OCL threshold, the counter is reset and the OCL threshold is returned to the higher value.

There are some important considerations for this type of over-current protection. The load current is higher than the over-current threshold by one half of the peak-to-peak inductor ripple current. Also, when the current is being limited, the output voltage tends to fall as the demanded load current may be higher than the current available from the converter. This may cause the output voltage to fall. When the VFB voltage falls below the UVP threshold voltage, the UVP comparator detects it. And then, the device will shut down after the UVP delay time (typically 14 µs) and re-start after the hiccup time.

When the over current condition is removed, the output voltage returns to the regulated value.

7.3.5 Over Voltage Protection

TPS562210A and TPS563210A detect over voltage condition by monitoring the feedback voltage (VFB). When the feedback voltage becomes higher than 125% of the target voltage, the OVP comparator output goes high and the high-side MOSFET is turns off. This function is non-latch operation.

7.3.6 UVLO Protection

Under voltage lock out protection (UVLO) monitors the internal regulator voltage. When the voltage is lower than UVLO threshold voltage, the device is shut off. This protection is non-latching.

7.3.7 Thermal Shutdown

The device monitors the temperature of itself. If the temperature exceeds the threshold value (typically 155°C), the device is shut off. This is a non-latch protection.

7.4 Device Functional Modes

7.4.1 Advanced Eco-Mode™ Control

The TPS562210A and TPS563210A are designed with Advanced Eco-mode™ to maintain high light load efficiency. As the output current decreases from heavy load condition, the inductor current is also reduced and eventually comes to point that its rippled valley touches zero level, which is the boundary between continuous conduction and discontinuous conduction modes. The rectifying MOSFET is turned off when the zero inductor current is detected. As the load current further decreases the converter runs into discontinuous conduction mode. The on-time is kept almost the same as it was in the continuous conduction mode so that it takes longer time to discharge the output capacitor with smaller load current to the level of the reference voltage. This makes the switching frequency lower, proportional to the load current, and keeps the light load efficiency high. The transition point to the light load operation IOUT(LL) current can be calculated in Equation 2.