JAJSJM8B August 2020 – June 2022 TPS628510 , TPS628511 , TPS628512 , TPS628513

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 説明

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3 Feature Description

- 9.4

Device Functional Modes

- 9.4.1 Pulse Width Modulation (PWM) Operation

- 9.4.2 Power Save Mode Operation (PWM/PFM)

- 9.4.3 100% Duty-Cycle Operation

- 9.4.4 Current Limit and Short Circuit Protection

- 9.4.5 Foldback Current Limit and Short Circuit Protection

- 9.4.6 Output Discharge

- 9.4.7 Soft Start / Tracking (SS/TR)

- 9.4.8 Input Overvoltage Protection

- 10Application and Implementation

- 11Power Supply Recommendations

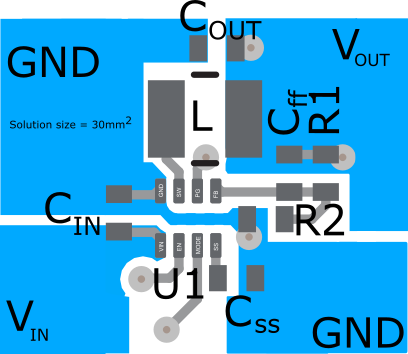

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

12.2 Layout Example

Figure 12-1 Example

Layout

Figure 12-1 Example

Layout