JAJSHI2E June 2014 – May 2019 TPS65283 , TPS65283-1

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 代表的な回路図

- 5 改訂履歴

- 6 概要(続き)

- 7 Pin Configuration and Functions

- 8 Specifications

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3

Feature Description

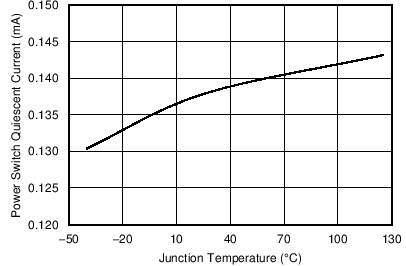

- 9.3.1 Power Switch Detailed Description

- 9.3.2

Buck DC-DC Converter Detailed Description

- 9.3.2.1 Output Voltage

- 9.3.2.2 Adjustable Switching Frequency

- 9.3.2.3 Synchronization

- 9.3.2.4 Error Amplifier

- 9.3.2.5 Slope Compensation

- 9.3.2.6 Enable and Adjusting UVLO

- 9.3.2.7 Internal V7V Regulator

- 9.3.2.8 Short Circuit Protection

- 9.3.2.9 Bootstrap Voltage (BST) and Low Dropout Operation

- 9.3.2.10 Output Overvoltage Protection (OVP)

- 9.3.2.11 Power Good

- 9.3.2.12 Power-Up Sequencing

- 9.3.2.13 Thermal Performance

- 9.4 Device Functional Modes

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13デバイスおよびドキュメントのサポート

- 14メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- RGE|24

サーマルパッド・メカニカル・データ

- RGE|24

発注情報

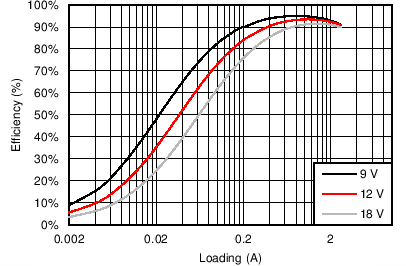

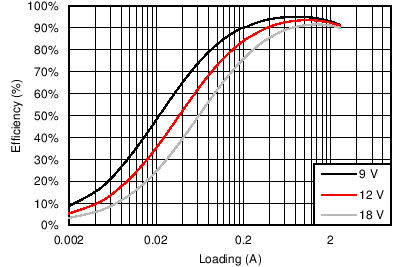

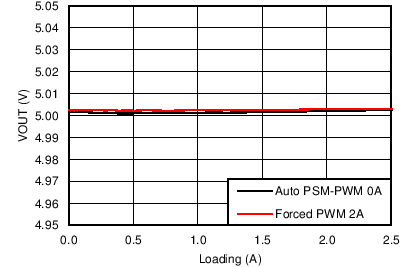

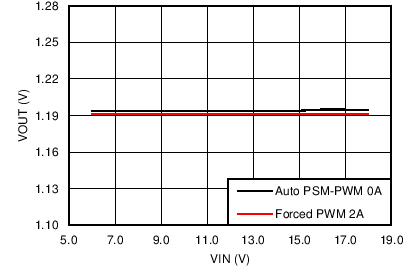

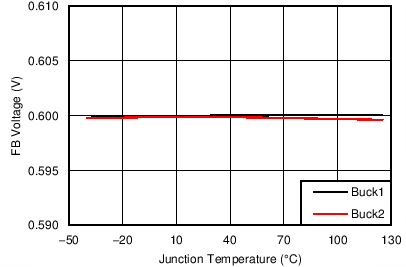

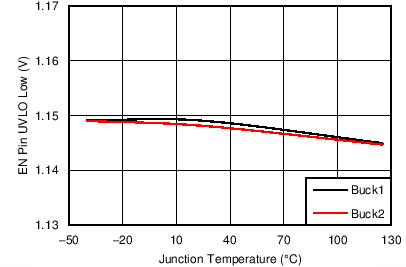

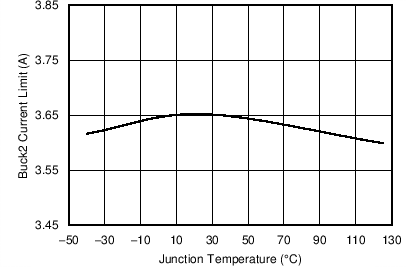

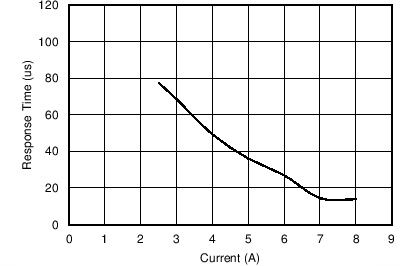

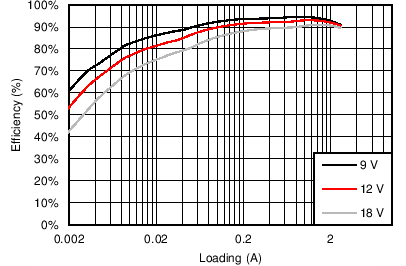

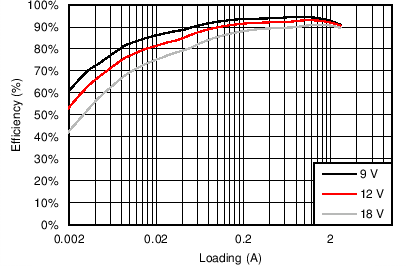

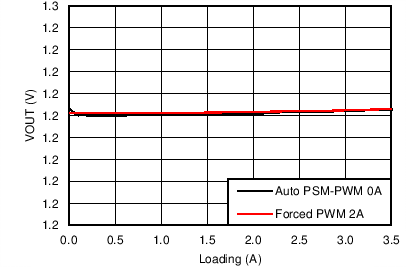

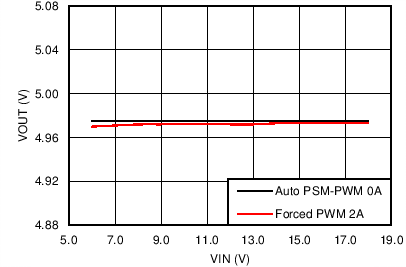

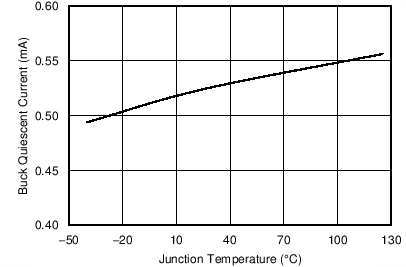

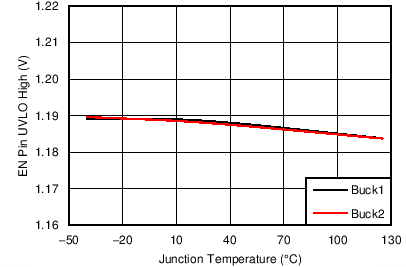

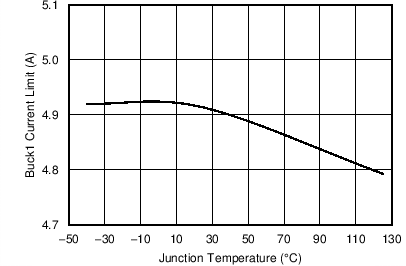

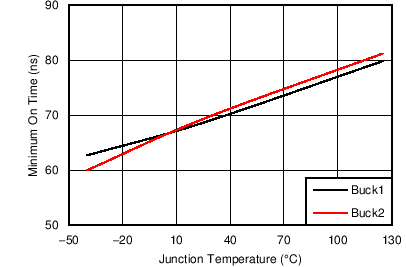

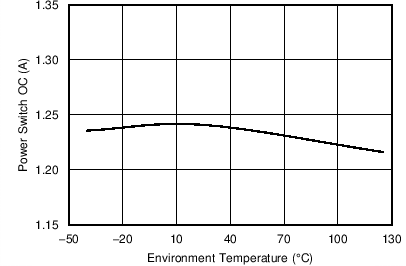

8.6 Typical Characteristics

TJ = 25°C, Vin = 12 V, Vout1 = 1.2 V, Vout2 = 5 V, ƒSW = 500 kHz, RnFAULT1 = RnFAULT2 = 100 kΩ (unless otherwise noted)

(Rset = 20 kΩ)