at TJ = 25°C, VIN =

VOUT(nom) + 0.3 V, VBIAS = 5 V, VEN =

VIN, CIN = 10 μF, CBIAS = 1 μF, and

COUT = 10 μF (unless otherwise noted)

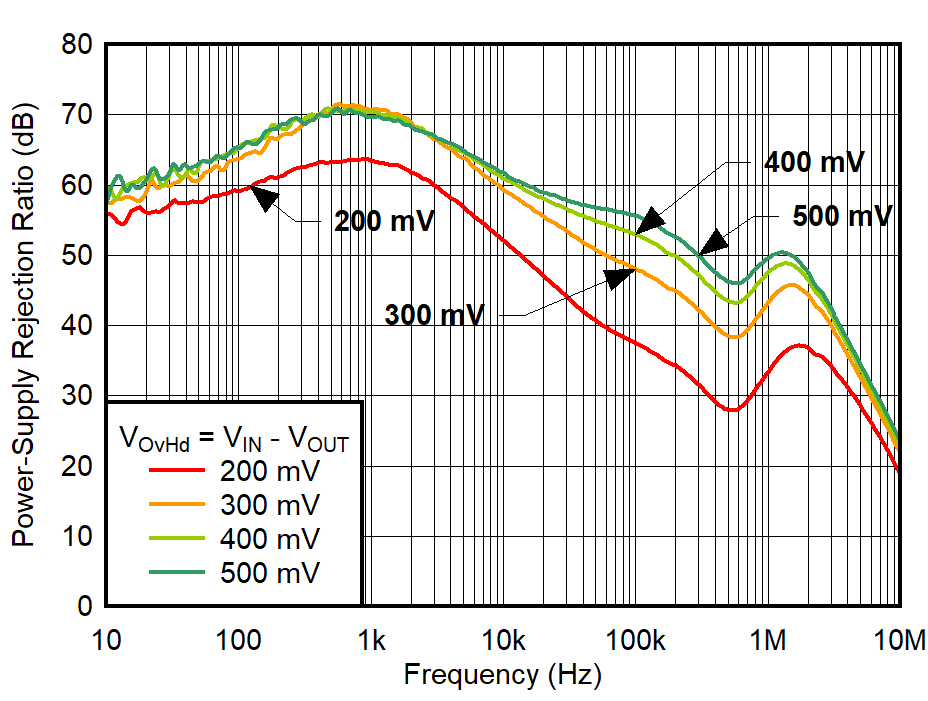

| CIN = COUT = 10 μF,

CBIAS = 1 μF |

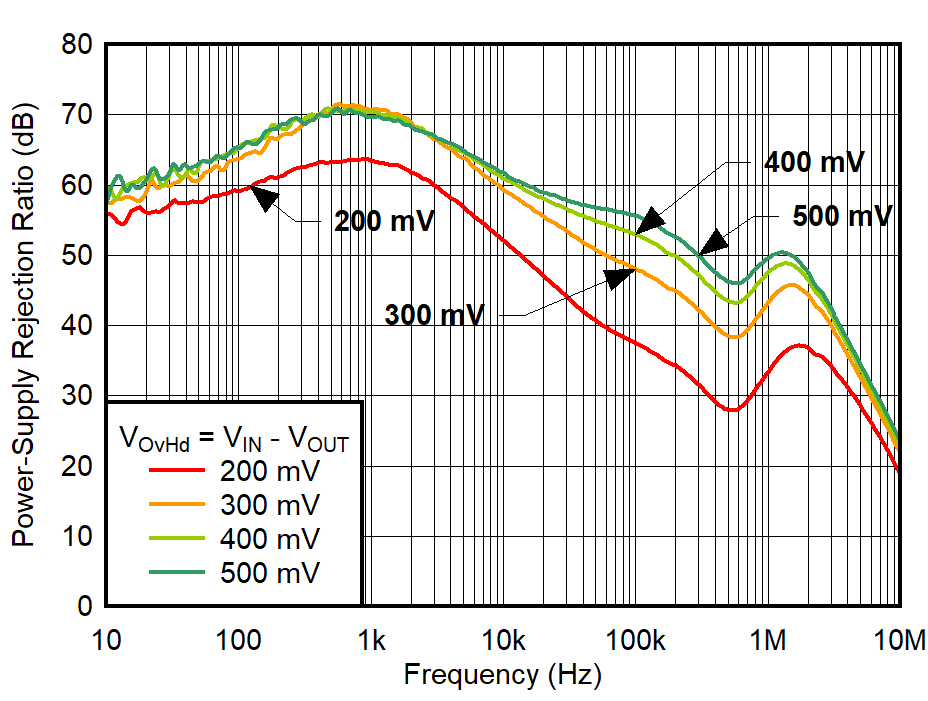

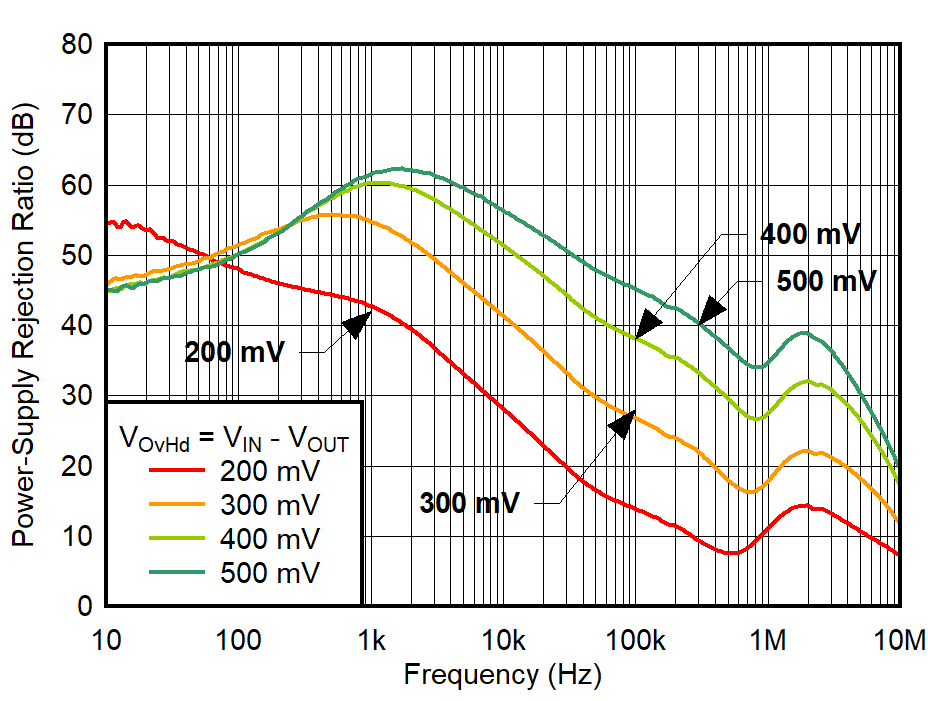

Figure 6-1 PSRR

vs Frequency and Overhead (OvHd) Voltage for IOUT = 400 mA,

VOUT = 1.8 V

| CIN = COUT = 10 μF,

CBIAS = 1 μF |

Figure 6-3 PSRR

vs Frequency and Overhead (OvHd) Voltage for IOUT = 1.1 A,

VOUT = 1.8 V

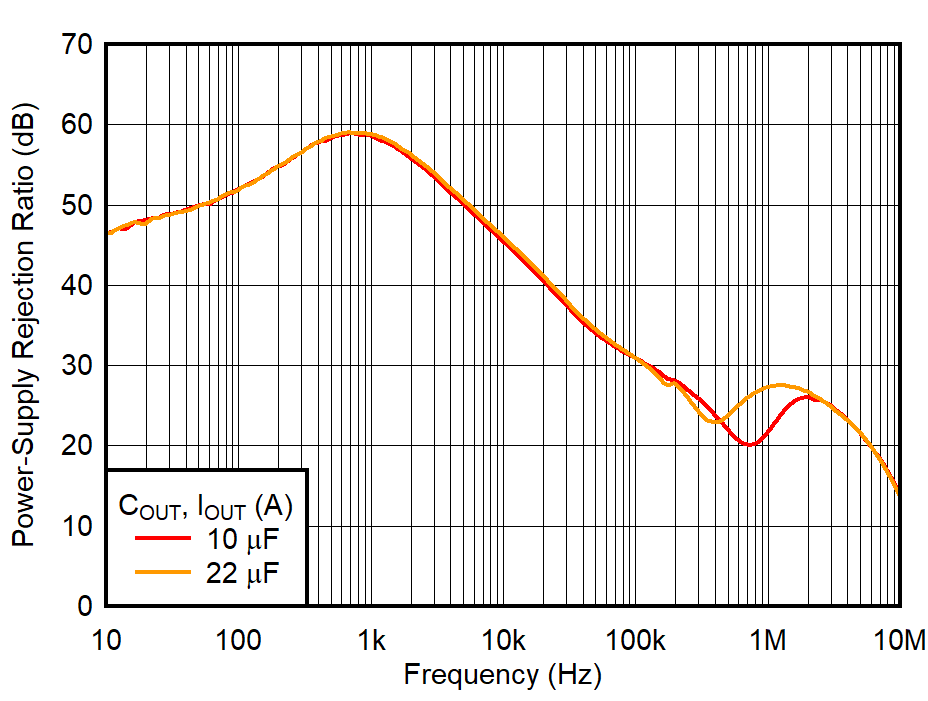

| CIN = COUT = 10 μF,

CBIAS = 1 μF, IOUT = 1.5

A |

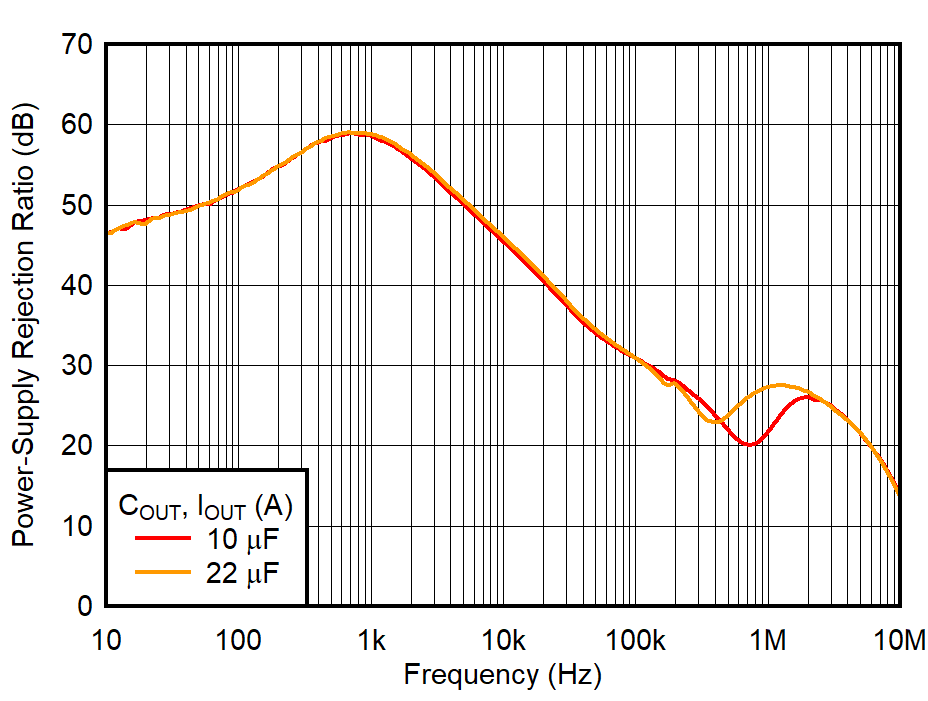

Figure 6-5 PSRR

vs Frequency and COUT for VOUT = 1.8 V

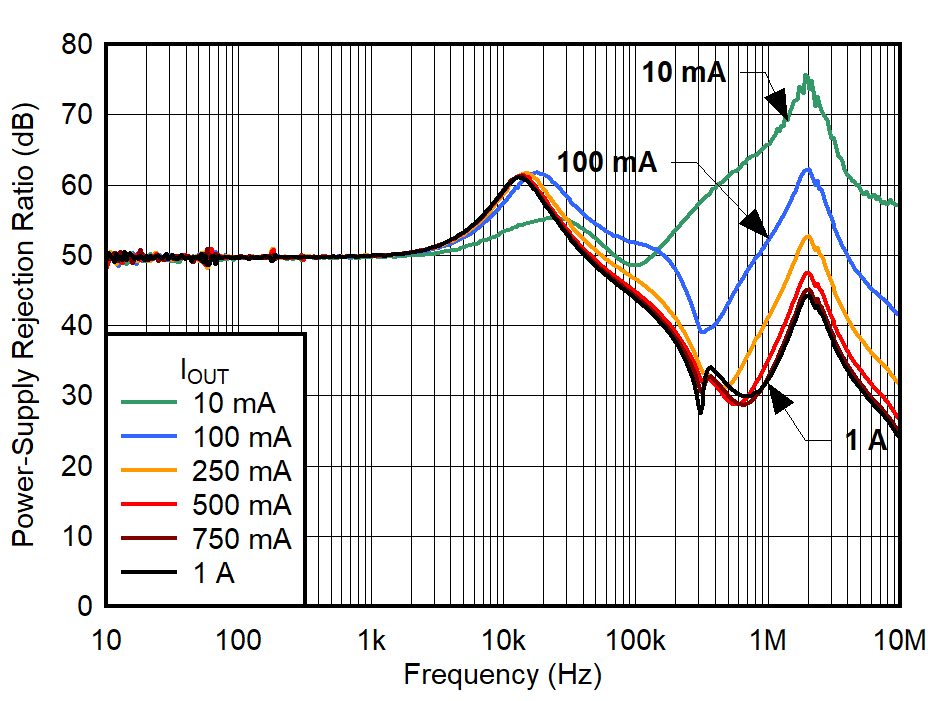

| VIN = VOUT + 0.3 V,

CIN = COUT = 10 μF,

CBIAS = 1 μF |

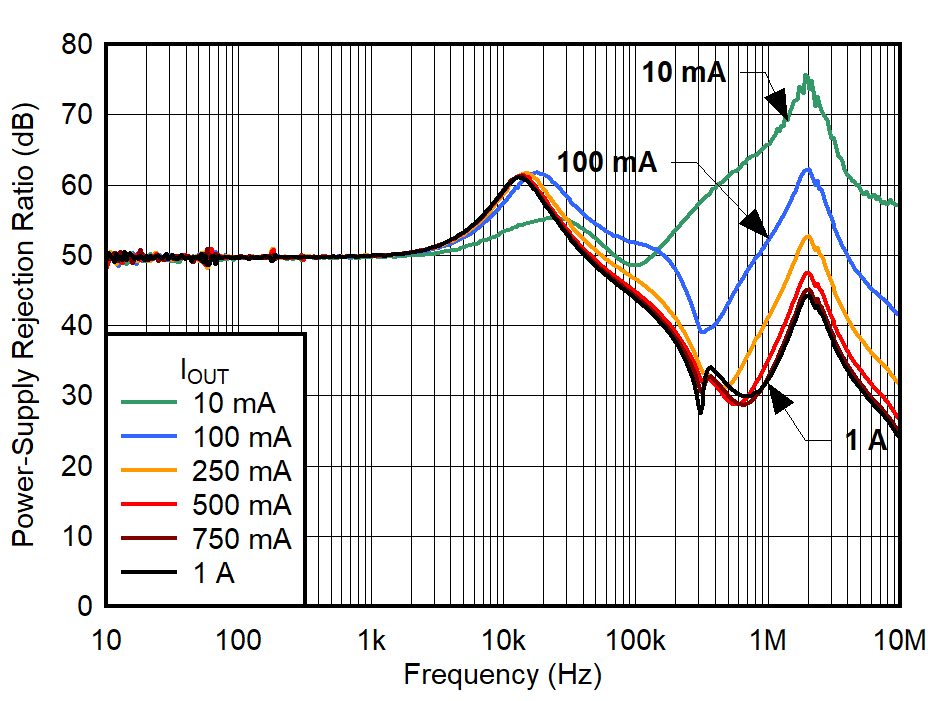

Figure 6-7 Bias

Rail PSRR vs Frequency and IOUT

| CIN = COUT = 10 μF,

CBIAS = 1 μF |

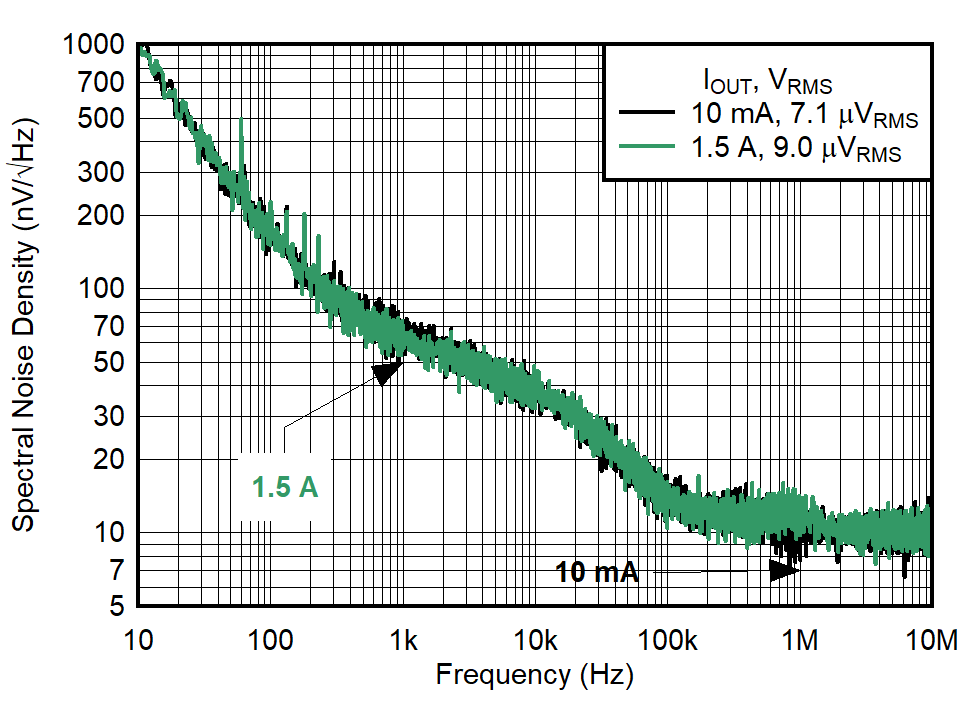

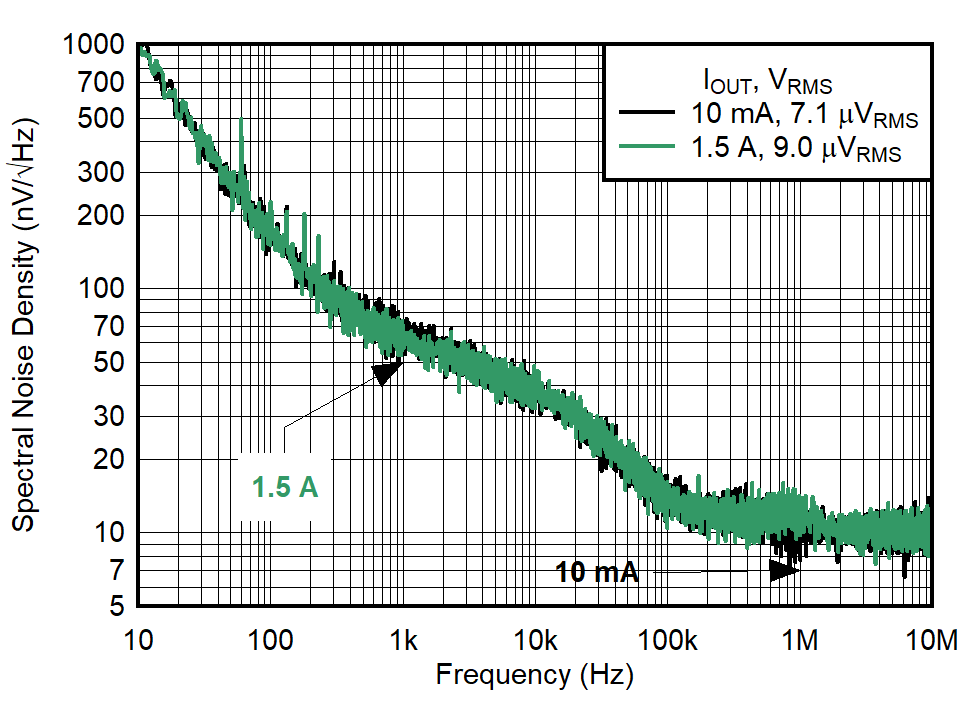

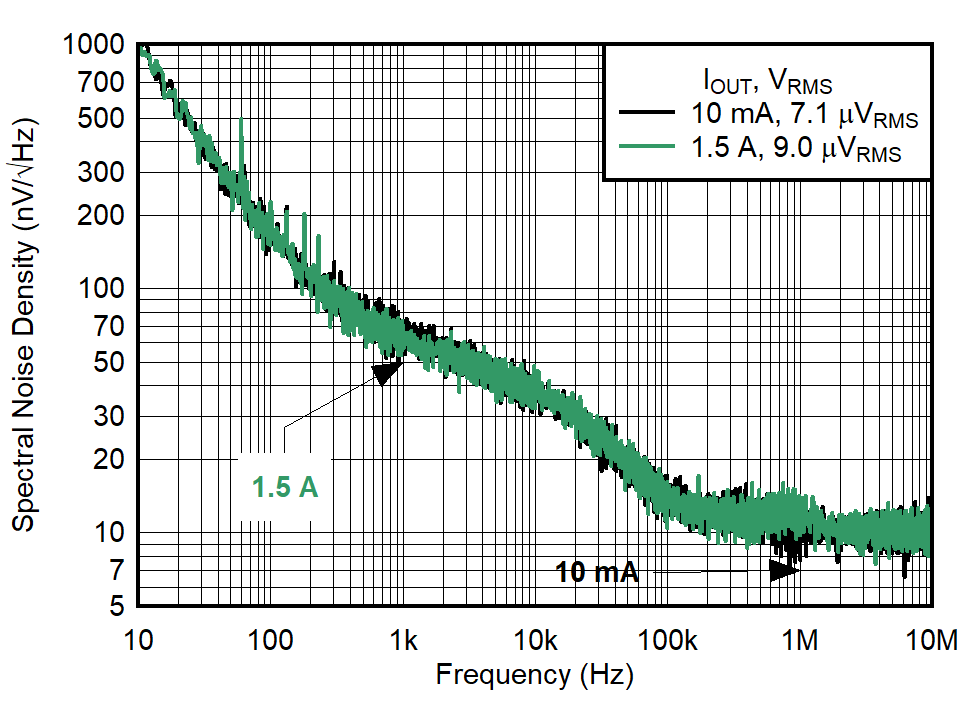

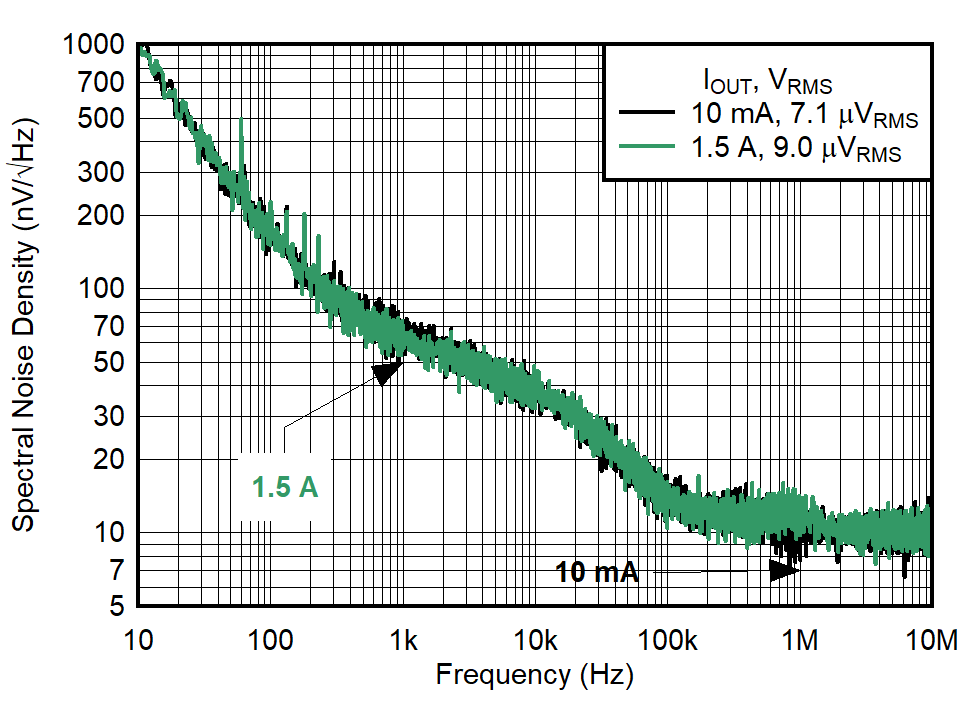

Figure 6-9 Noise

vs Frequency and IOUT for VOUT = 3.3 V

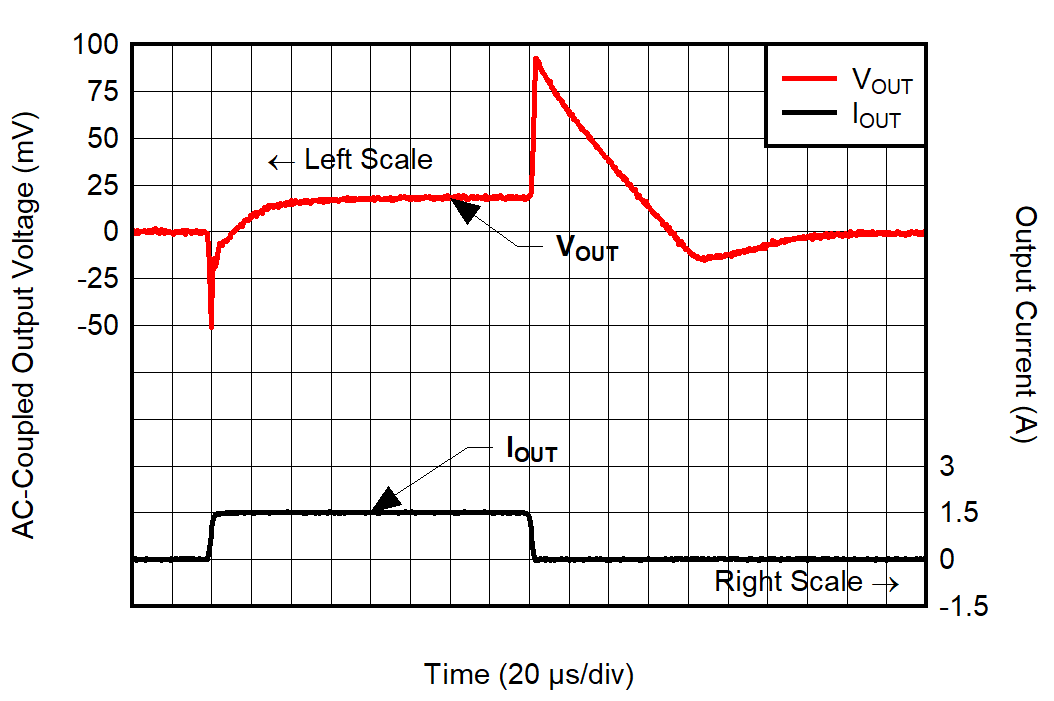

| CIN = COUT = 10 μF,

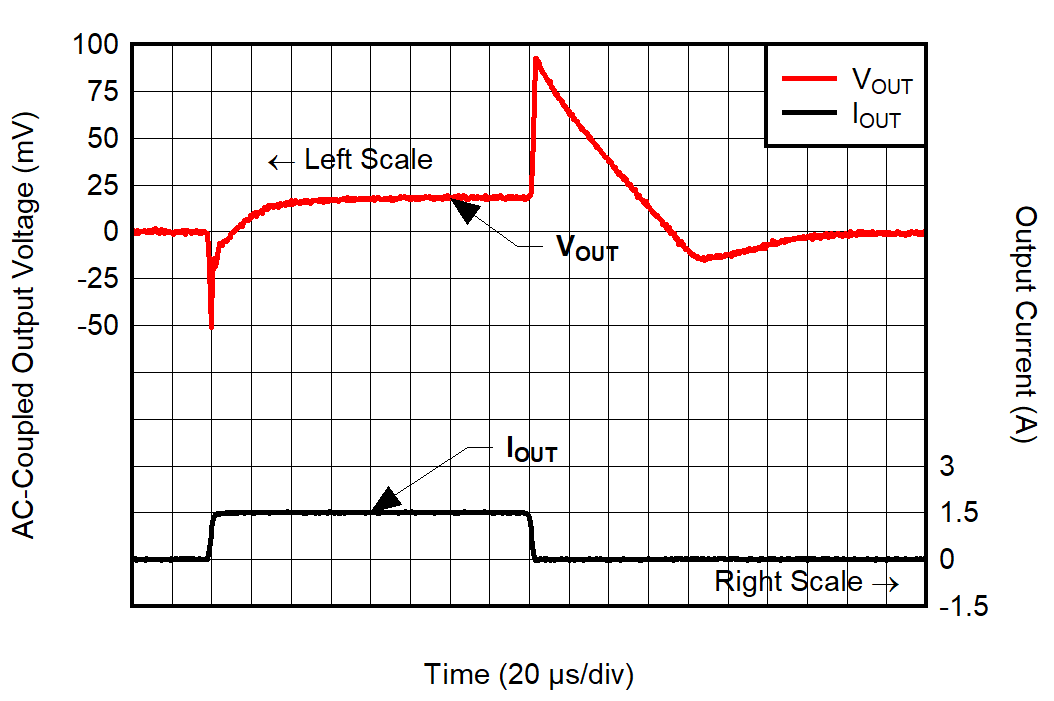

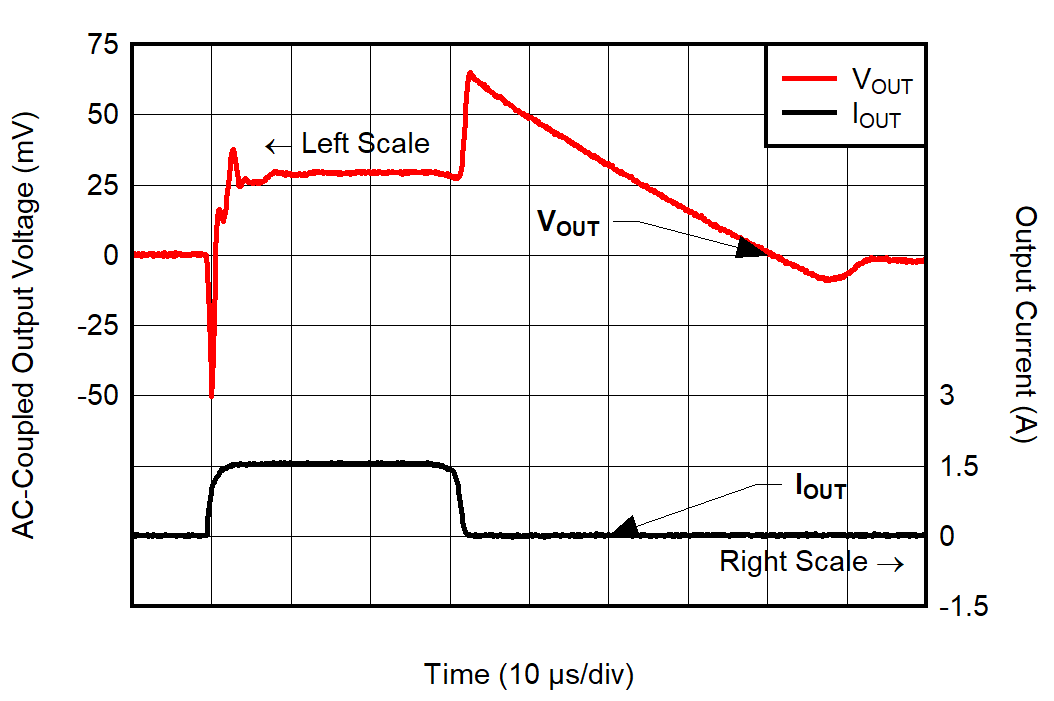

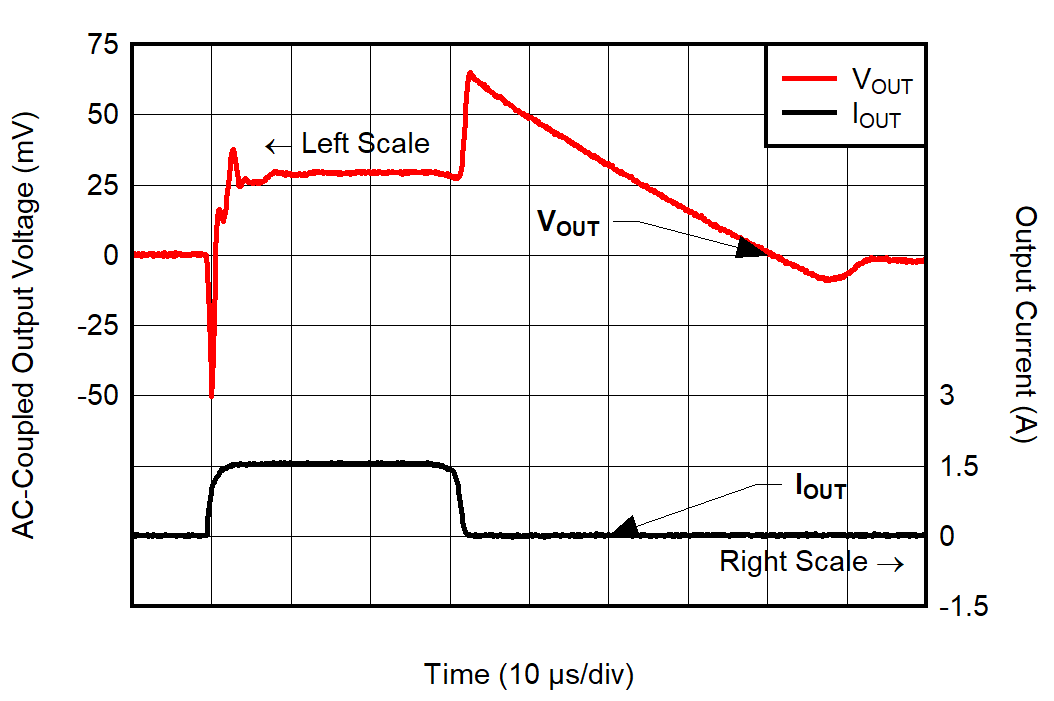

CBIAS = 1 μF, IOUT = 10 mA to

1.5 A to 10 mA |

Figure 6-11 Load Transient for VOUT = 3.3 V

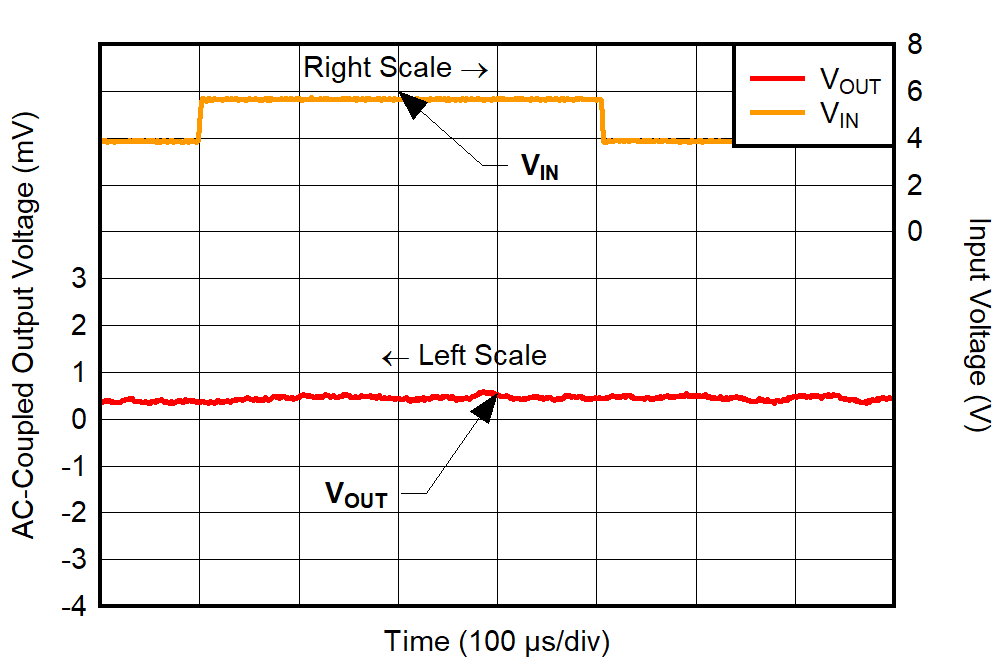

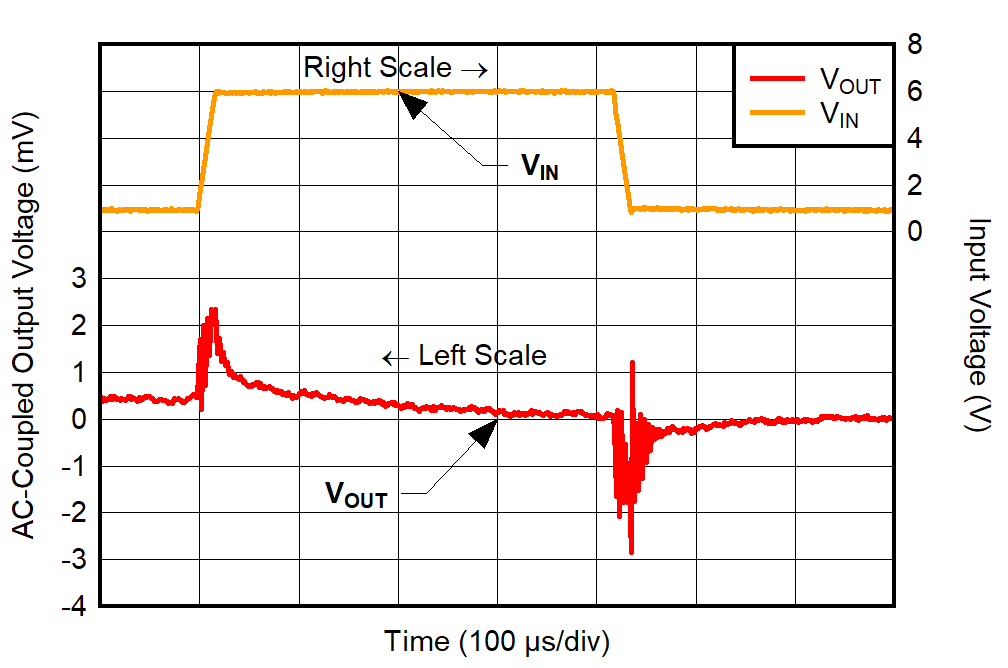

| CIN = COUT = 10 μF,

CBIAS = 1 μF, IOUT = 1.5 A,

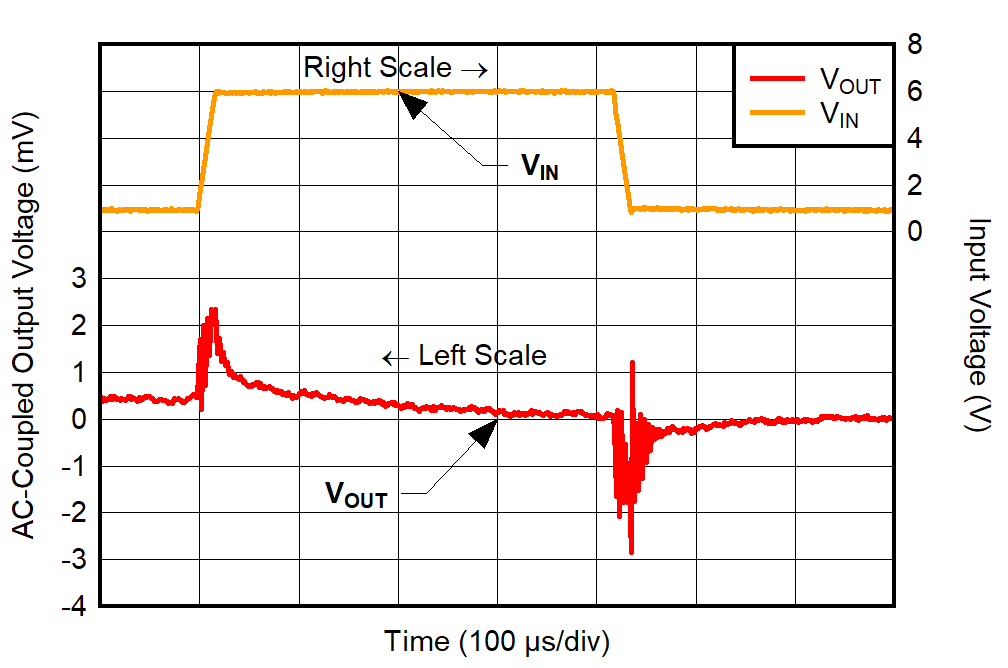

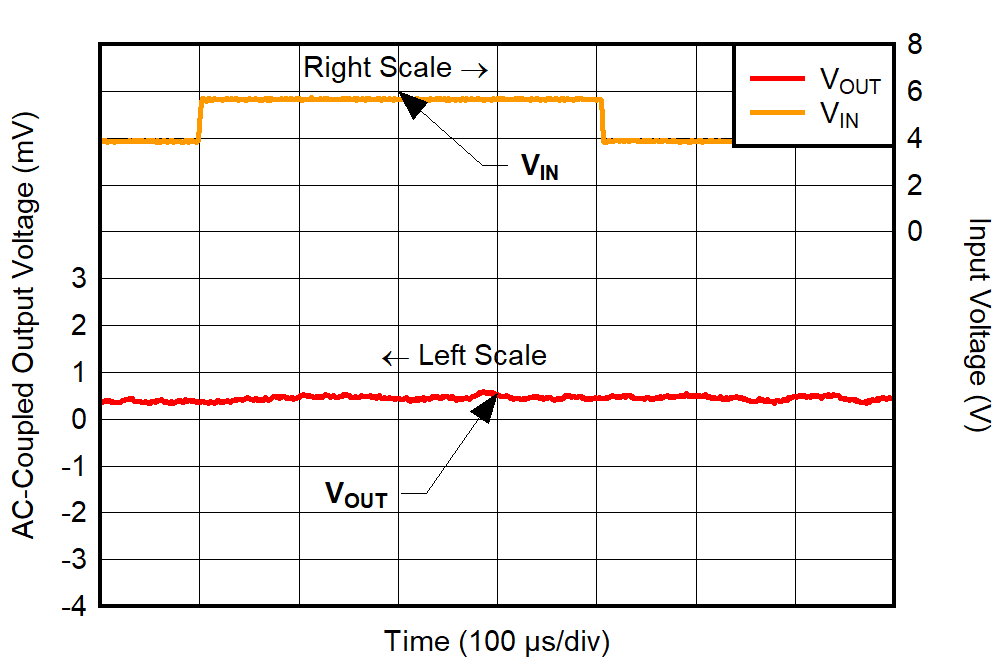

VIN = 3.9 V to 5.8 V to 3.9 V |

Figure 6-13 Line Transient for VOUT = 3.3 V

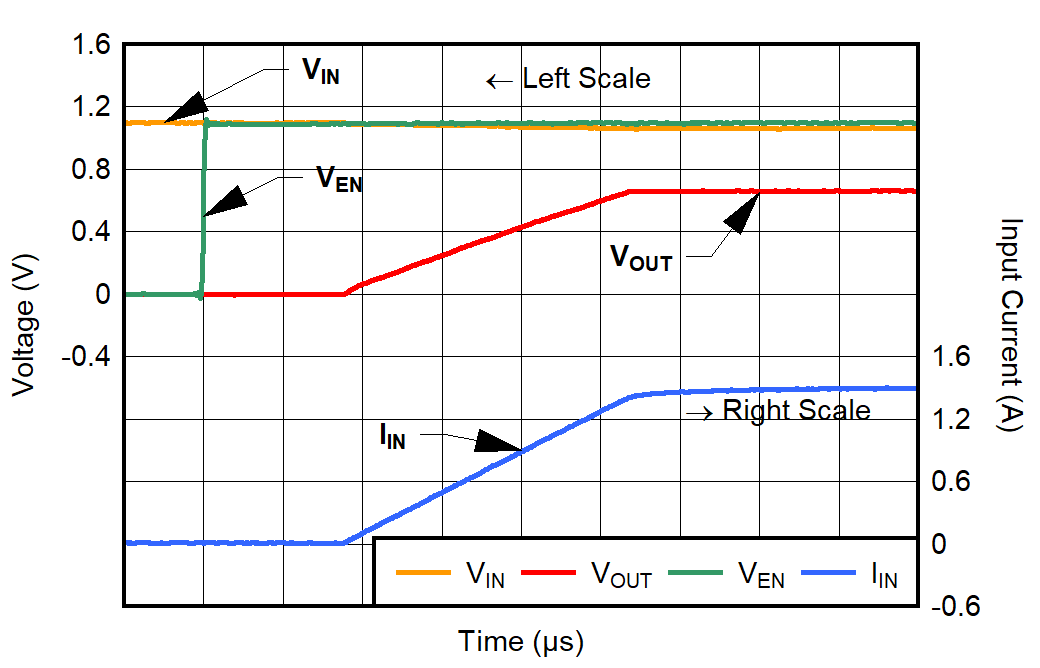

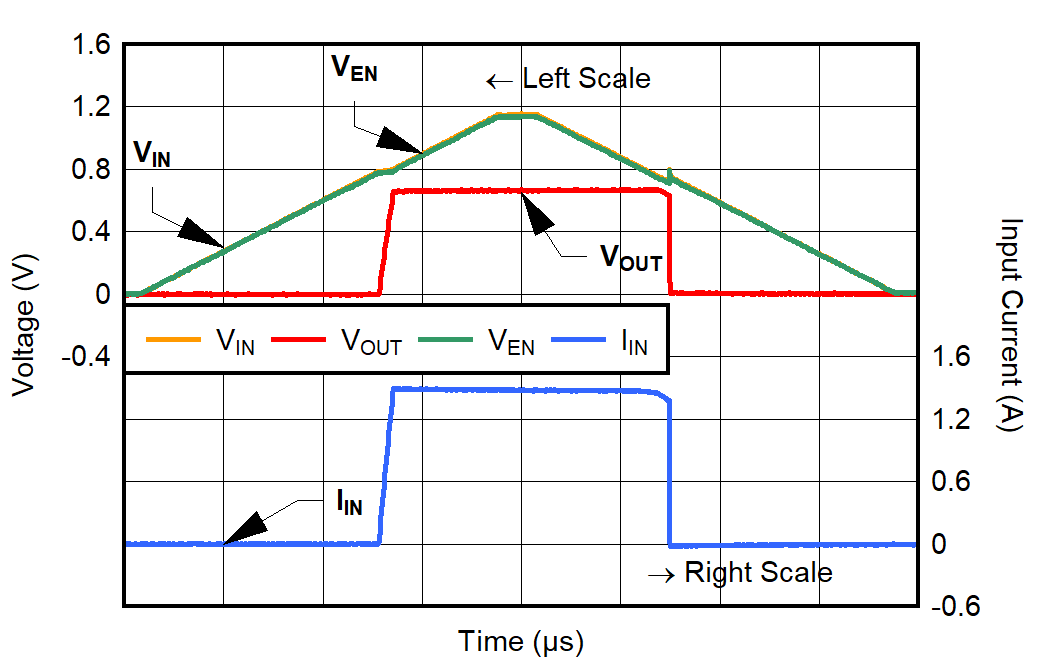

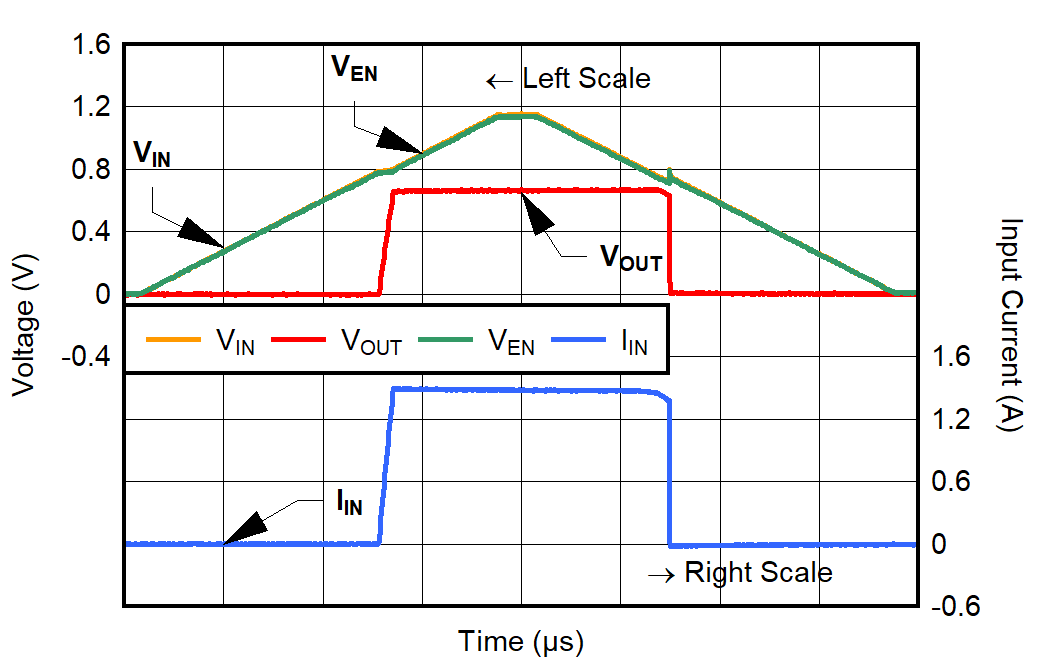

| CIN = COUT = 10 μF,

CBIAS = 1 μF, IOUT = 1.5 A,

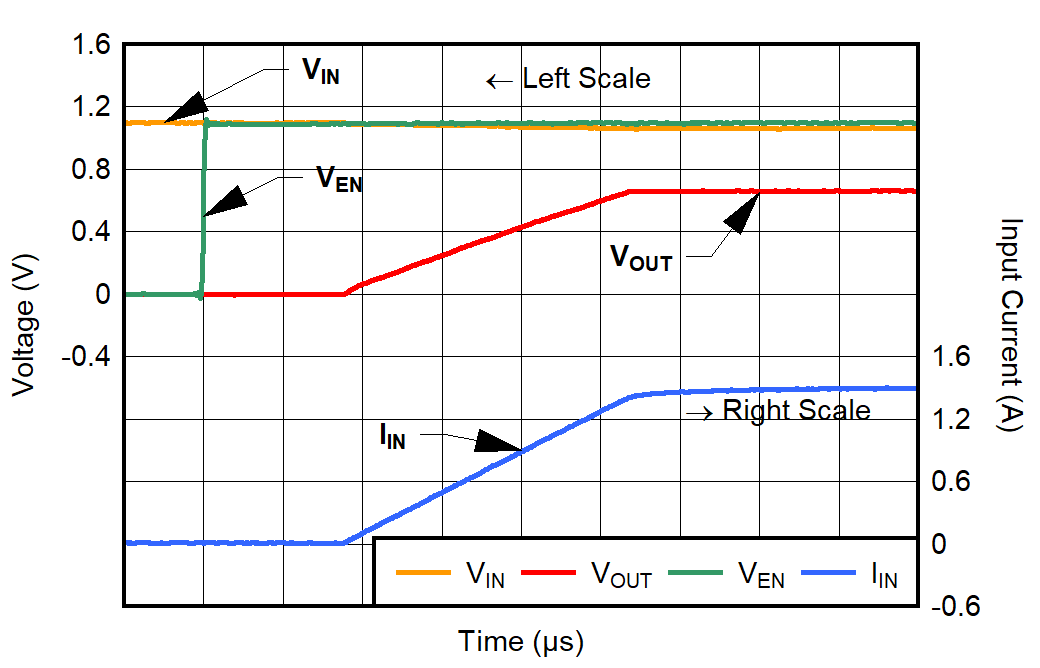

VIN = 1.1 V, VBIAS = 5

V |

Figure 6-15 Input

Ramp With Fast Soft-Start

| CIN = COUT = 10 μF,

CBIAS = 1 μF |

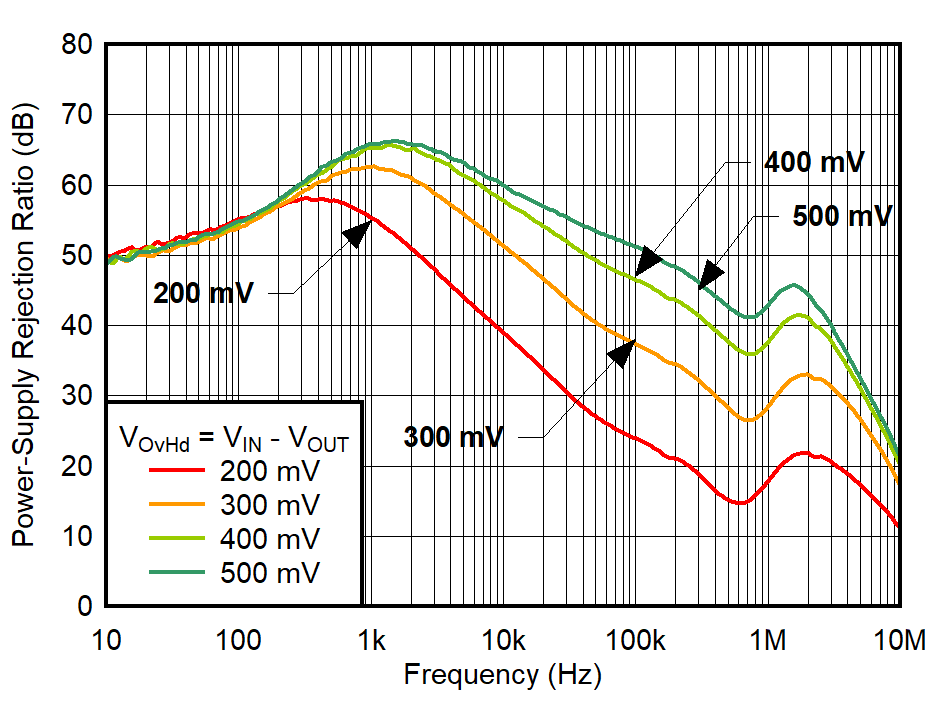

Figure 6-2 PSRR

vs Frequency and Overhead (OvHd) Voltage for IOUT = 750 mA,

VOUT = 1.8 V

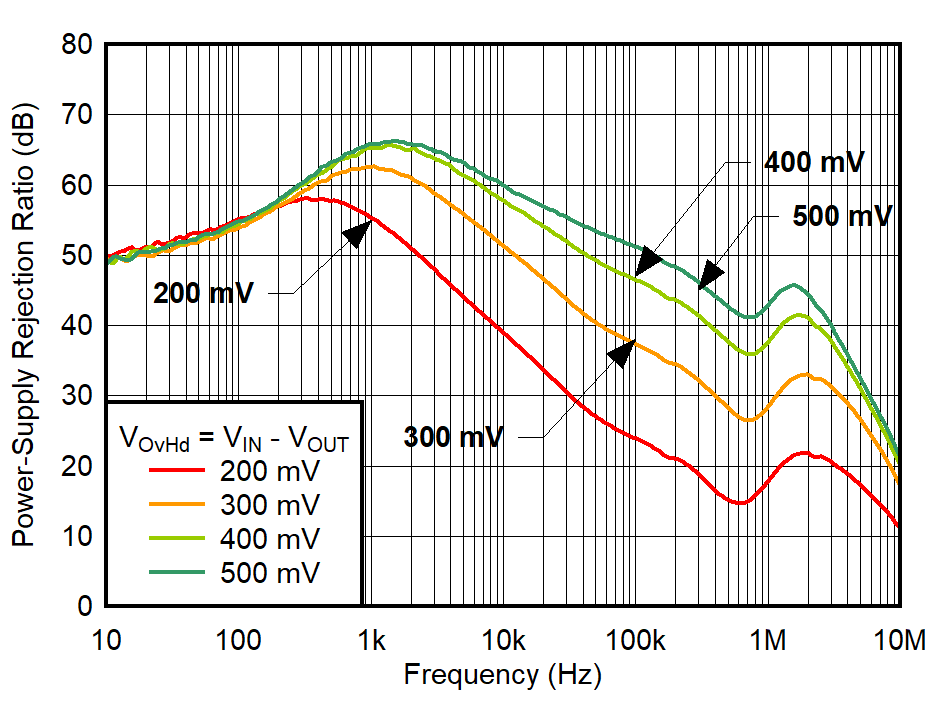

| CIN = COUT = 10 μF,

CBIAS = 1 μF |

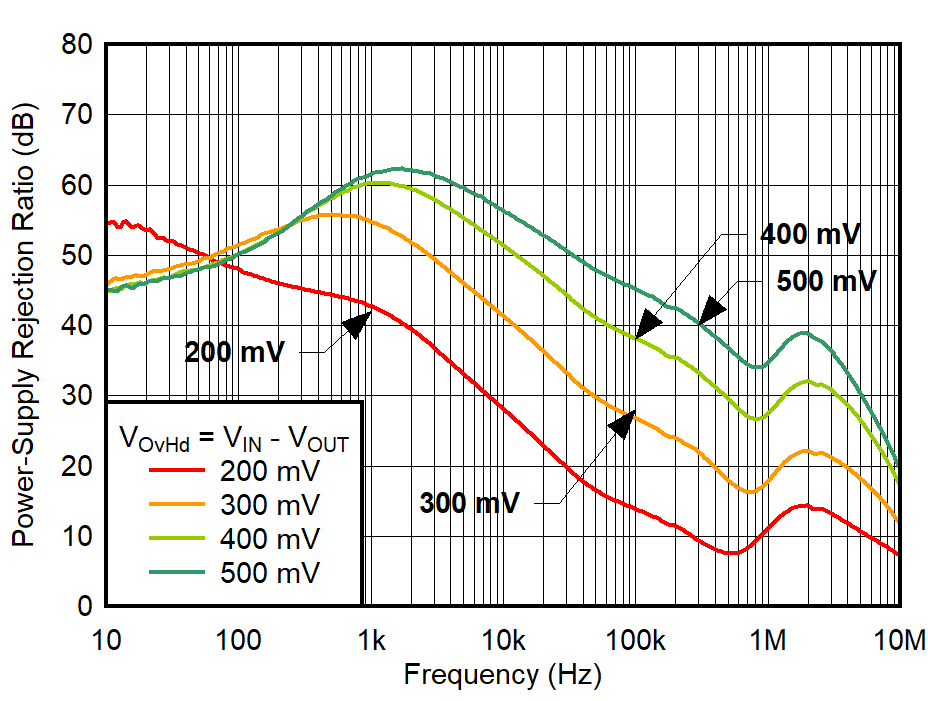

Figure 6-4 PSRR

vs Frequency and Overhead (OvHd) Voltage for IOUT = 1.5 A,

VOUT = 1.8 V

| CIN = COUT = 10 μF,

CBIAS = 1 μF |

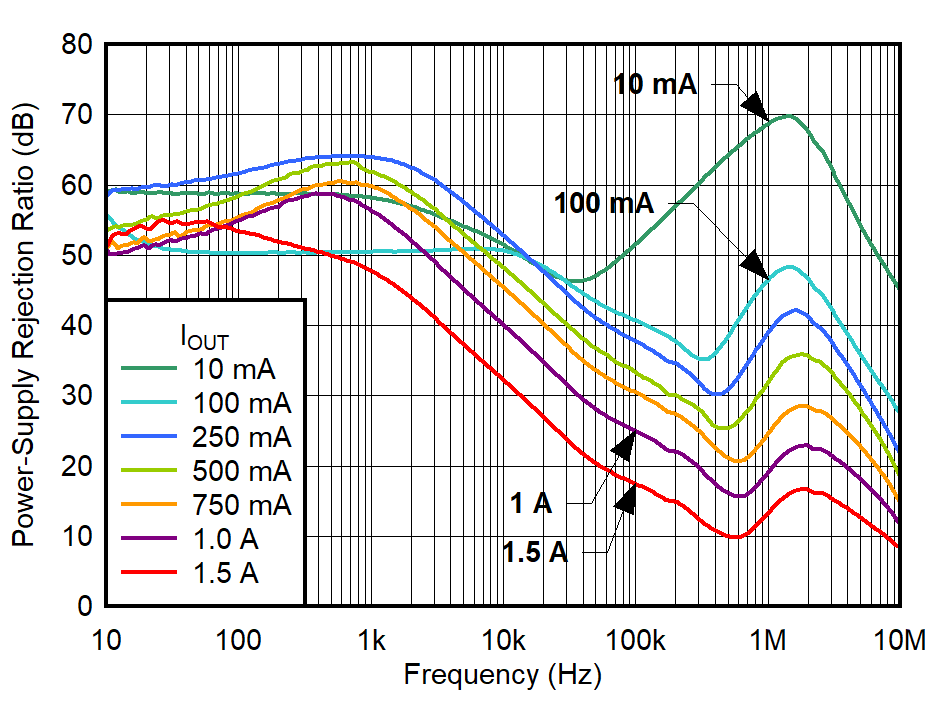

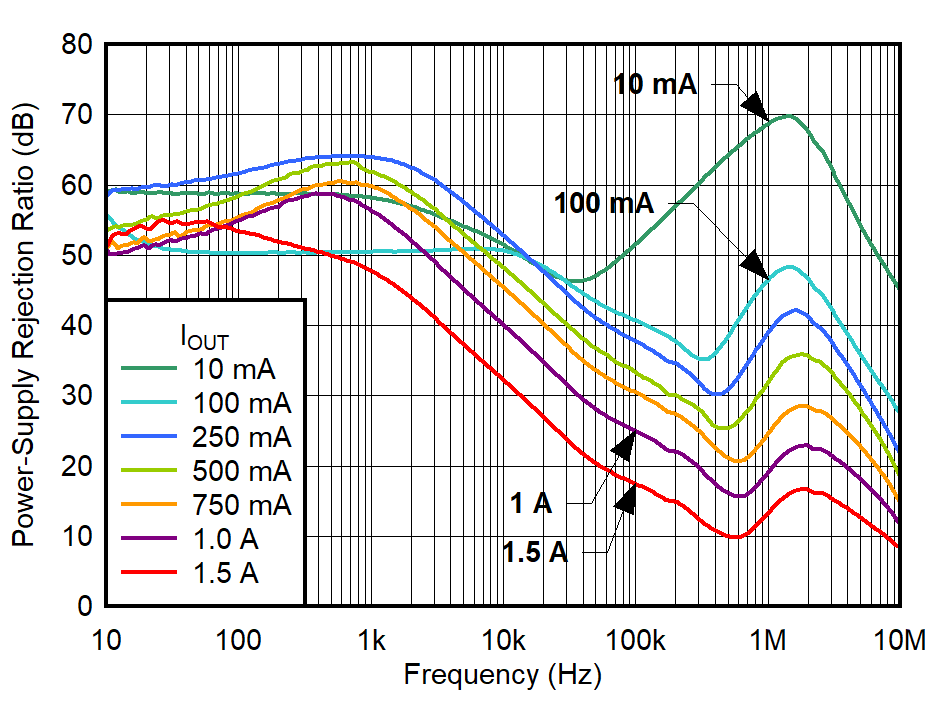

Figure 6-6 PSRR

vs Frequency and IOUT for VOvHd = 200 mV

| CIN = COUT = 10 μF,

CBIAS = 1 μF |

Figure 6-8 Noise

vs Frequency and IOUT for VOUT = 0.65 V

| CIN = COUT = 10 μF,

CBIAS = 1 μF, IOUT = 10 mA to

1.5 A to 10 mA |

Figure 6-10 Load Transient for VOUT = 0.65 V

| CIN = COUT = 10 μF,

CBIAS = 1 μF, IOUT = 1.5 A,

VIN = 0.95 V to 6 V to 0.95 V |

Figure 6-12 Line Transient for VOUT = 0.65 V

| CIN = COUT = 10 μF,

CBIAS = 1 μF, IOUT = 1.5 A,

VBIAS = 5 V |

Figure 6-14 Input

Ramp-Up and Ramp-Down