JAJSM31 May 2022 TPS7A74

ADVANCE INFORMATION

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

3 概要

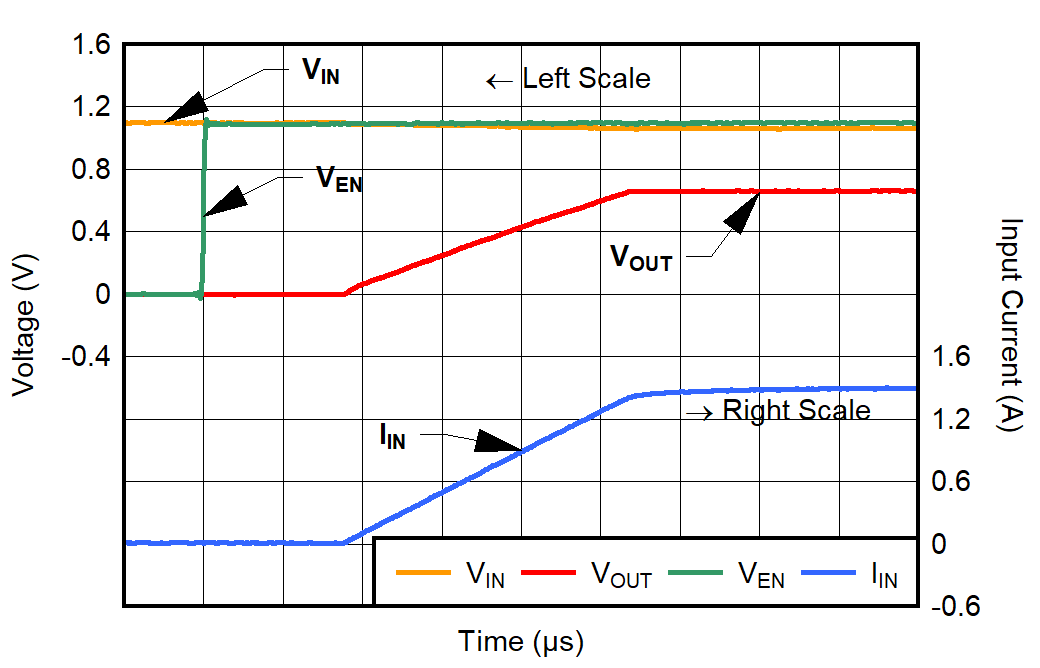

TPS7A74 低ドロップアウト (LDO) リニア・レギュレータは、広範なアプリケーション向けの使いやすく堅牢な電力管理ソリューションです。ソフトスタートをユーザーがプログラム可能なため、スタートアップ時の容量性負荷電流を低減して、入力電源のストレスを最小限に抑えることができます。ソフトスタートは単調性で、多くの種類のプロセッサおよび特定用途向け IC (ASIC) の電源に適しています。イネーブル入力とパワー・グッド出力により、外部レギュレータとの間でシーケンシングを簡単に実行できます。このような高い柔軟性により、FPGA や DSP、その他の特殊なスタートアップ条件を持つアプリケーションのシーケンス制御条件を満たすソリューションを構成できます。

高精度の基準電圧およびエラー・アンプは、負荷、ライン、温度、プロセスの範囲全体にわたって 2% の精度を維持します。本デバイスは 10μF 以上の任意のタイプのコンデンサで安定に動作し、TJ = -40℃~+125℃で仕様規定されています。TPS7A74 は小型の 3mm × 3mm WSON-8 パッケージで供給されるため、非常に小さいトータル・ソリューション・サイズを実現できます。

製品情報 (1)

| 部品番号 | パッケージ | 本体サイズ (公称) |

|---|---|---|

| TPS7A74 | WSON (8) | 3.00mm × 3.00mm |

(1) 利用可能なパッケージについては、このデータシートの末尾にある注文情報を参照してください。

代表的なアプリケーション回路 (可変)

代表的なアプリケーション回路 (可変) 負荷を接続した状態でのスタートアップ

負荷を接続した状態でのスタートアップ