JAJSMY4C September 2021 – December 2022 UCC14240-Q1

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Power Ratings

- 6.6 Insulation Specifications

- 6.7 Safety-Related Certifications

- 6.8 Electrical Characteristics

- 6.9 Safety Limiting Values

- 6.10 Insulation Characteristics

- 6.11 Typical Characteristics

- 7 Detailed Description

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Mechanical, Packaging, and Orderable Information

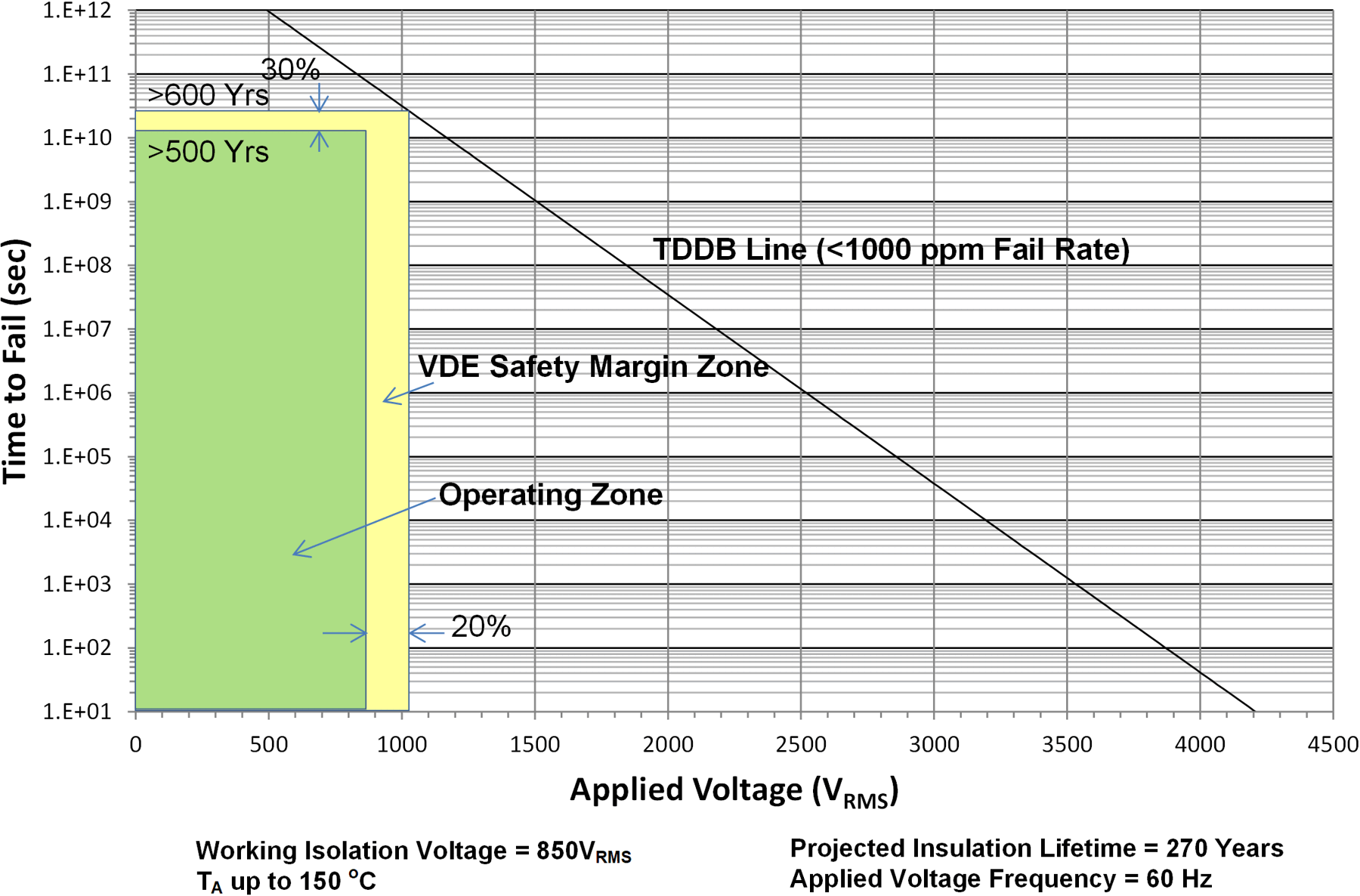

6.10 Insulation Characteristics

Figure 6-1 TDDB: Insulation Lifetime Projection for 850 Vrms Working Voltage.

Figure 6-1 TDDB: Insulation Lifetime Projection for 850 Vrms Working Voltage.