JAJSGJ4F August 2018 – September 2024 UCC21530-Q1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 ピン構成および機能

- 5 仕様

- 6 パラメータ測定情報

- 7 詳細説明

- 8 アプリケーションと実装

- 9 電源に関する推奨事項

- 10レイアウト

- 11デバイスおよびドキュメントのサポート

- 12改訂履歴

- 13メカニカル、パッケージ、および注文情報

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- DWK|14

サーマルパッド・メカニカル・データ

発注情報

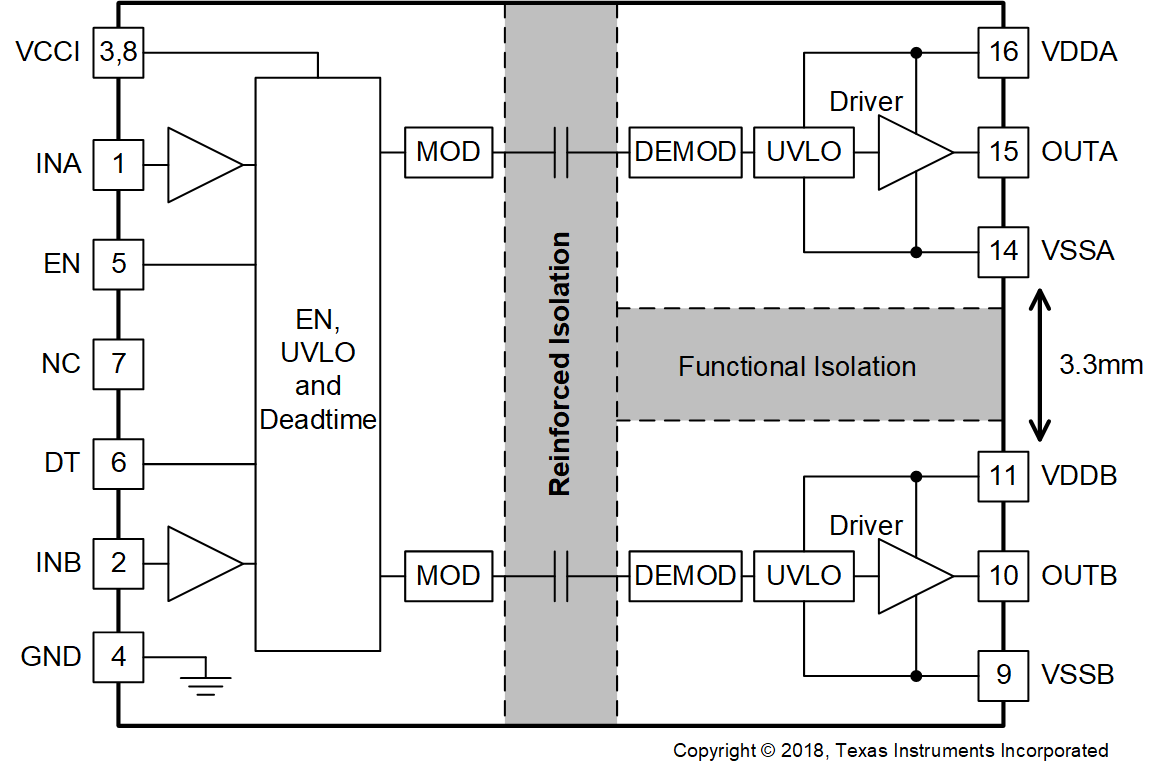

3 概要

UCC21530-Q1 は絶縁されたデュアル チャネルのゲート ドライバで、ピーク電流はソース 4A、シンク 6A です。IGBT、Si MOSFET、SiC MOSFET を最大 5MHz で駆動するように設計されています。

入力側は、5.7kVRMS の強化絶縁バリアによって 2 つの出力ドライバと分離されており、同相過渡耐性 (CMTI) は 125V/ns 以上です。2 つの 2 次側ドライバ間は、内部的に機能絶縁されているため、1850V までの電圧で動作します。

このデバイスは 2 つのローサイド ドライバ、2 つのハイサイド ドライバ、またはデッド タイム (DT) をプログラム可能な 1 つのハーフブリッジ ドライバとして構成可能です。EN ピンが Low になると、両方の出力が同時にシャットダウンされ、オープンまたは High のときは通常動作します。フェイルセーフ手法として、1 次側のロジック障害が発生すると、両方の出力が強制的に Low になります。

このデバイスは、最大 25V の VDD 電源電圧に対応できます。VCCI 入力範囲が 3V~18V と広いため、このドライバはアナログとデジタル両方のコントローラとの接続に適しています。すべての電源電圧ピンには、低電圧誤動作防止 (UVLO) 保護機能が搭載されています。

製品情報

| 部品番号 | パッケージ (1) | 本体サイズ (公称) |

|---|---|---|

| UCC21530-Q1 | DWK (SOIC 14) | 10.30mm × 7.50mm |

| UCC21530B-Q1 | DWK (SOIC 14) | 10.30mm × 7.50mm |

| UCC21530D-Q1 | DWK (SOIC 14) | 10.30mm × 7.50mm |

(1) 供給されているすべてのパッケージについては、セクション 13 を参照してください。

機能ブロック図

機能ブロック図