JAJSOG3 December 2023 UCC28750

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Device Comparison

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Revision History

- 11Mechanical, Packaging, and Orderable Information

8.2.4.1 Startup

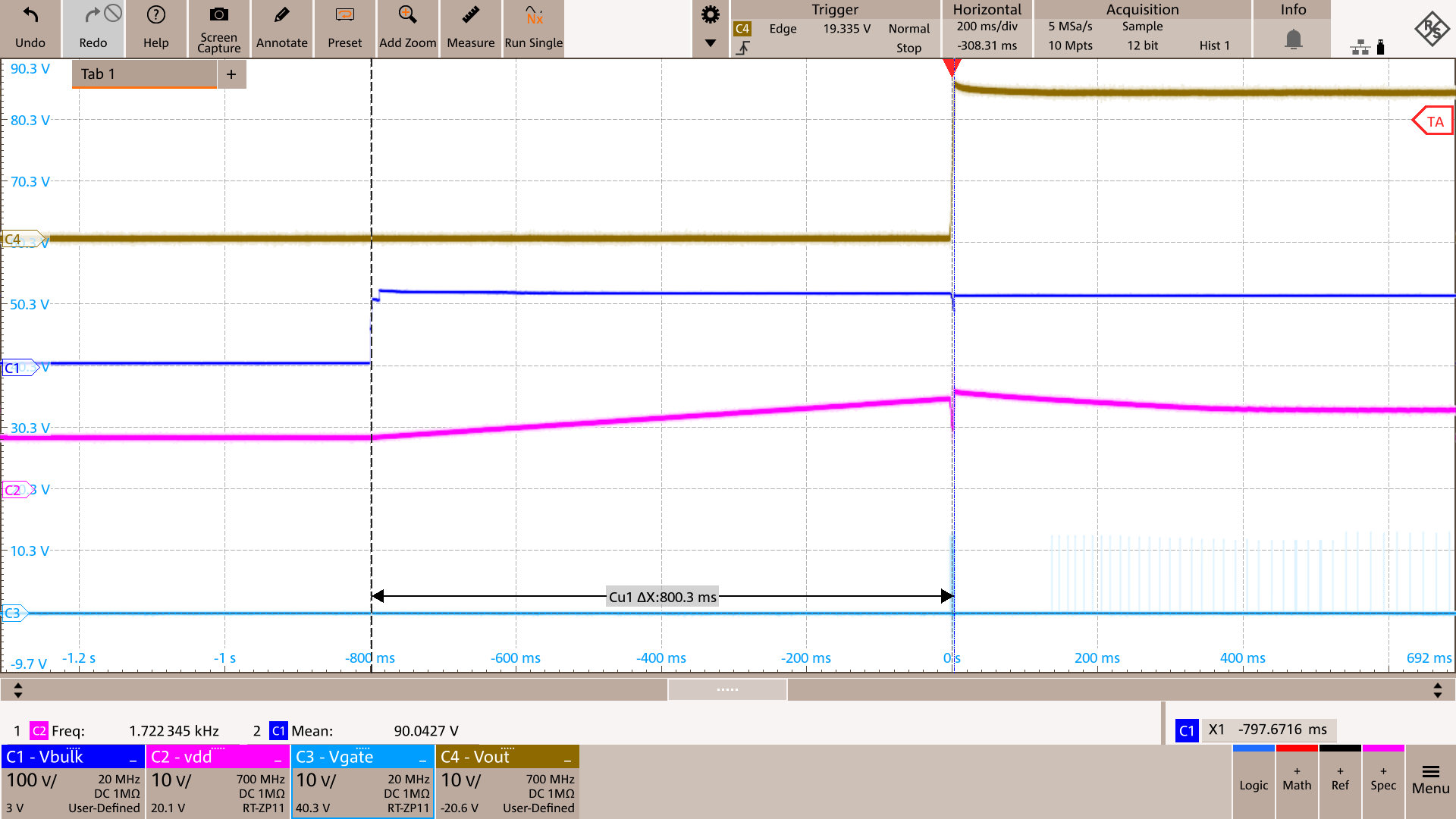

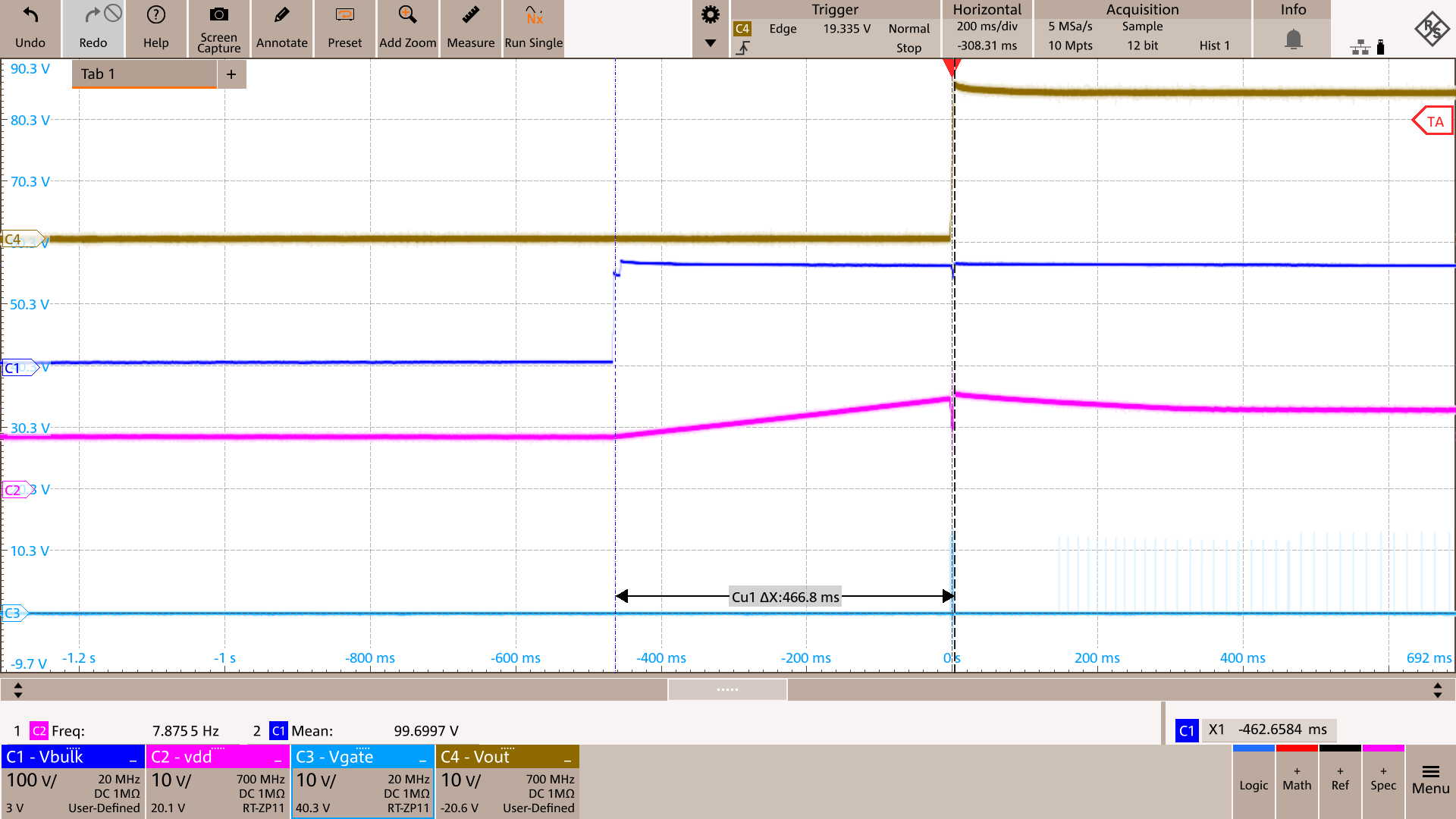

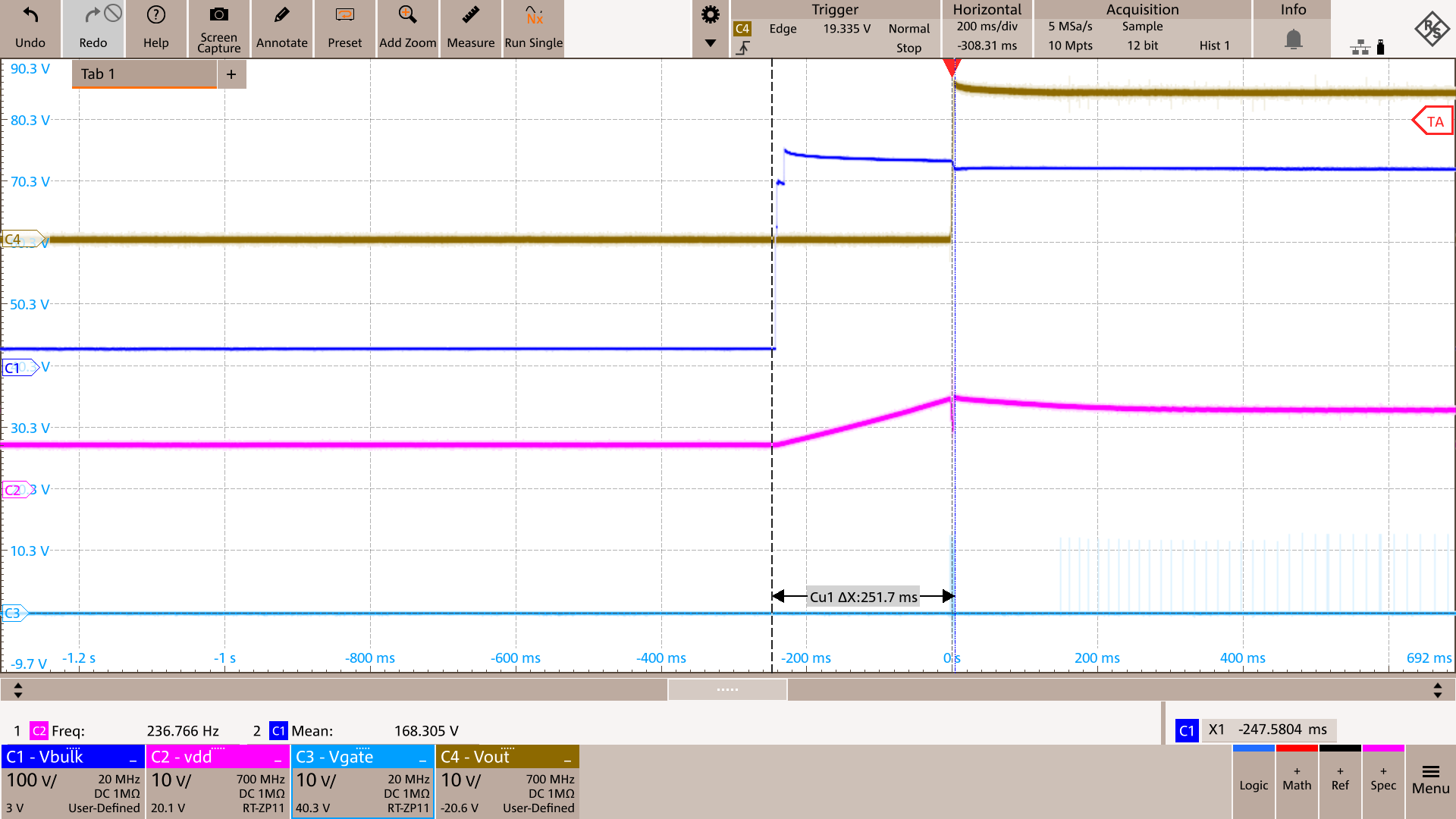

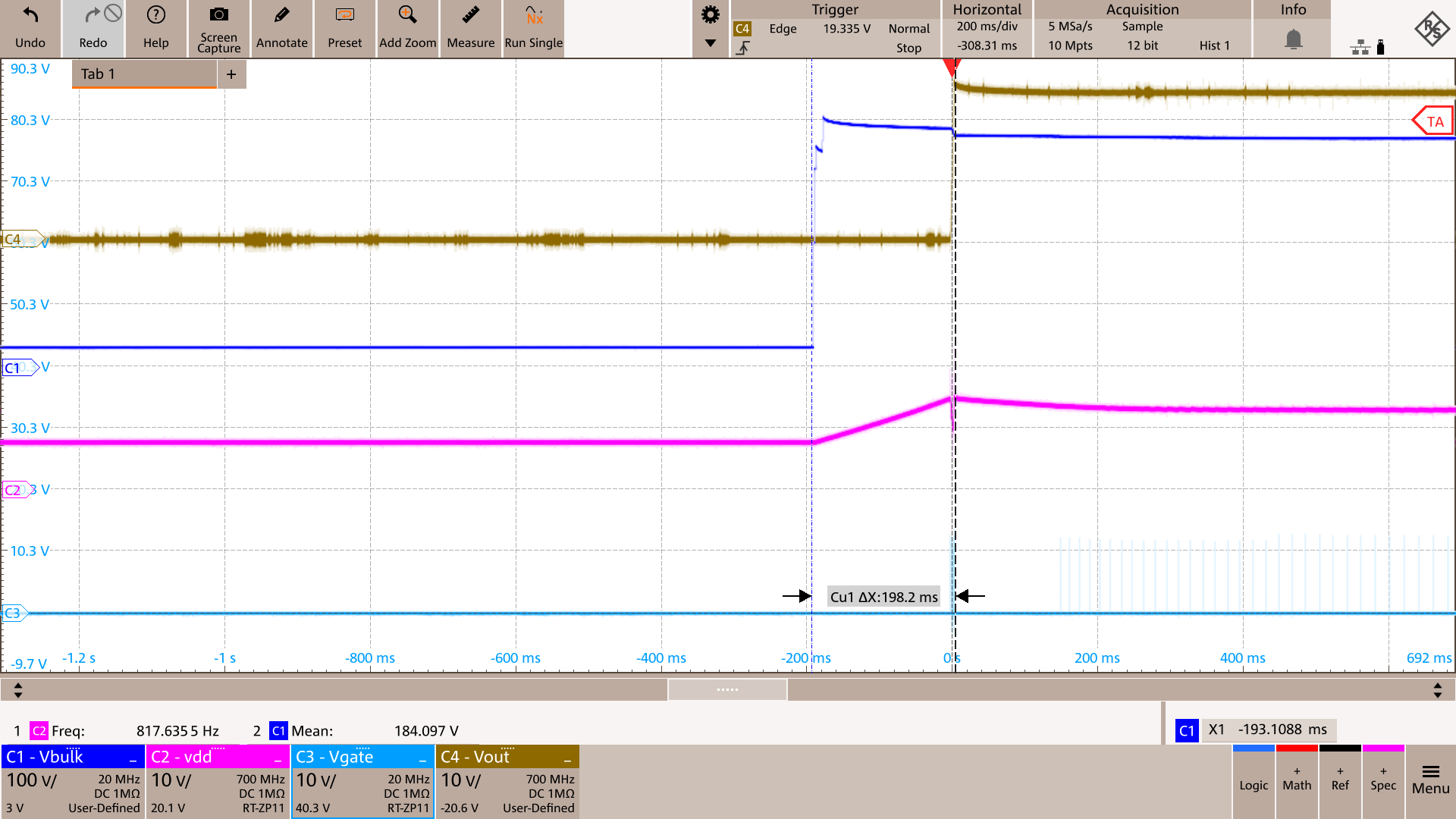

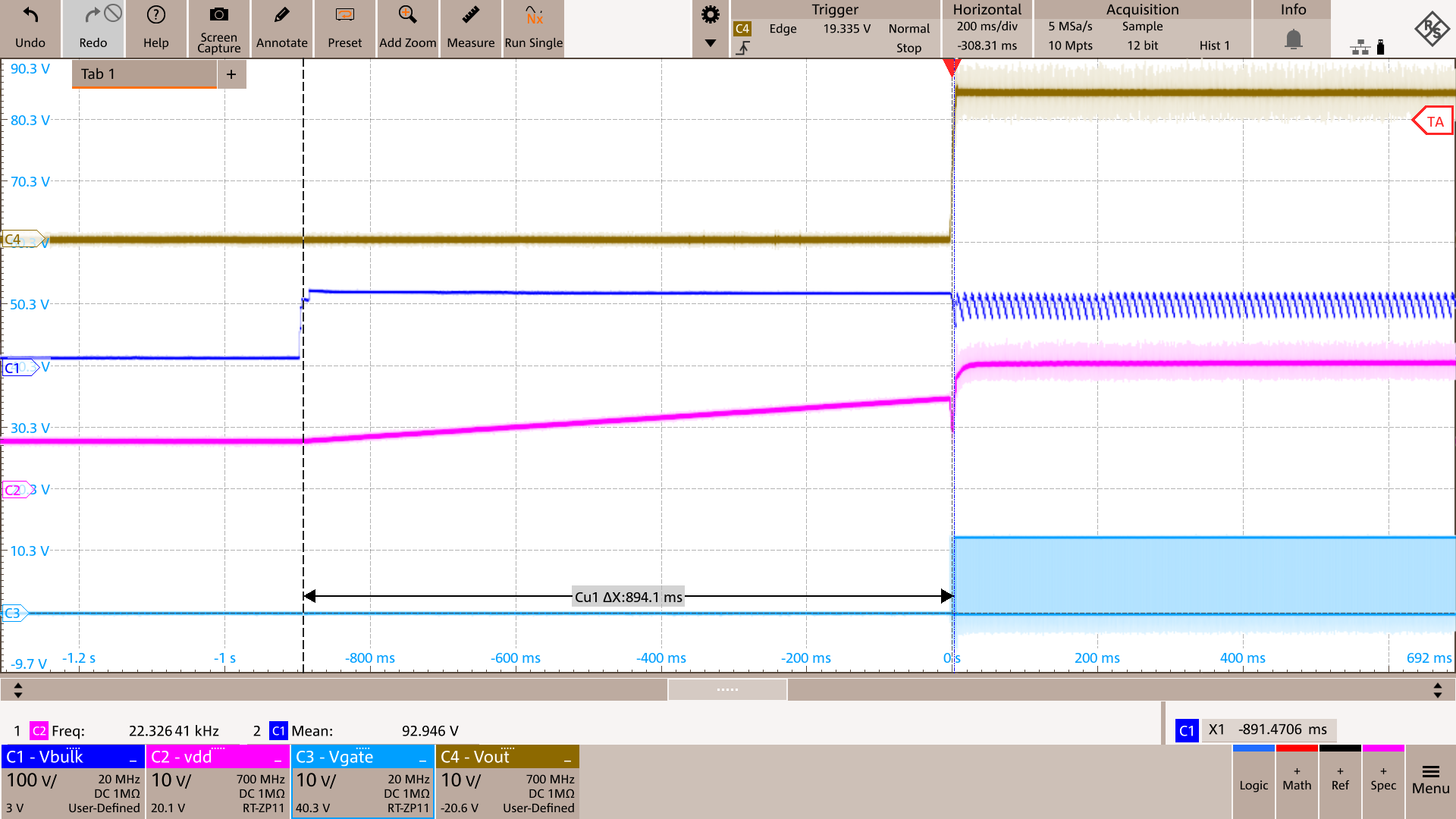

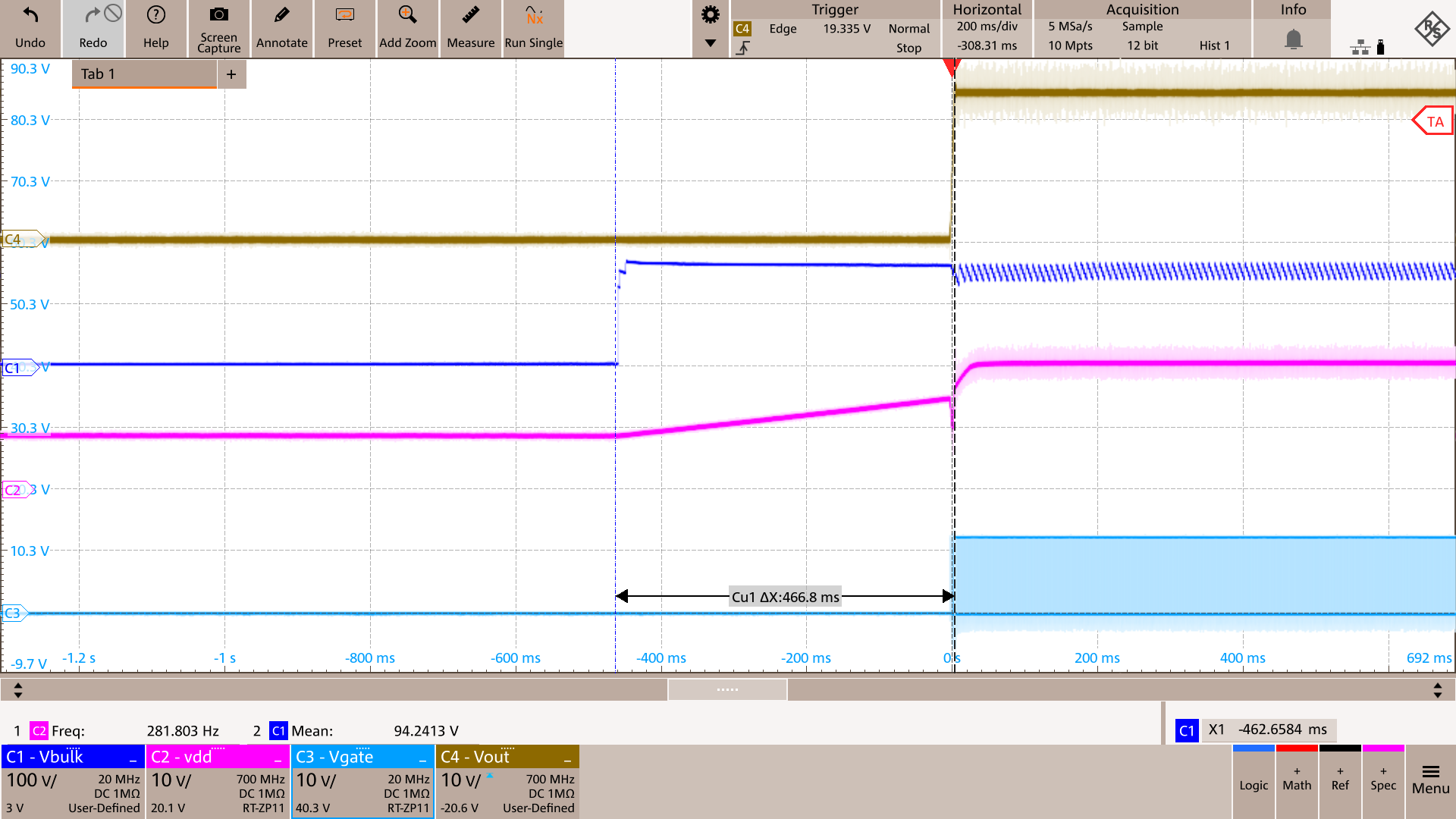

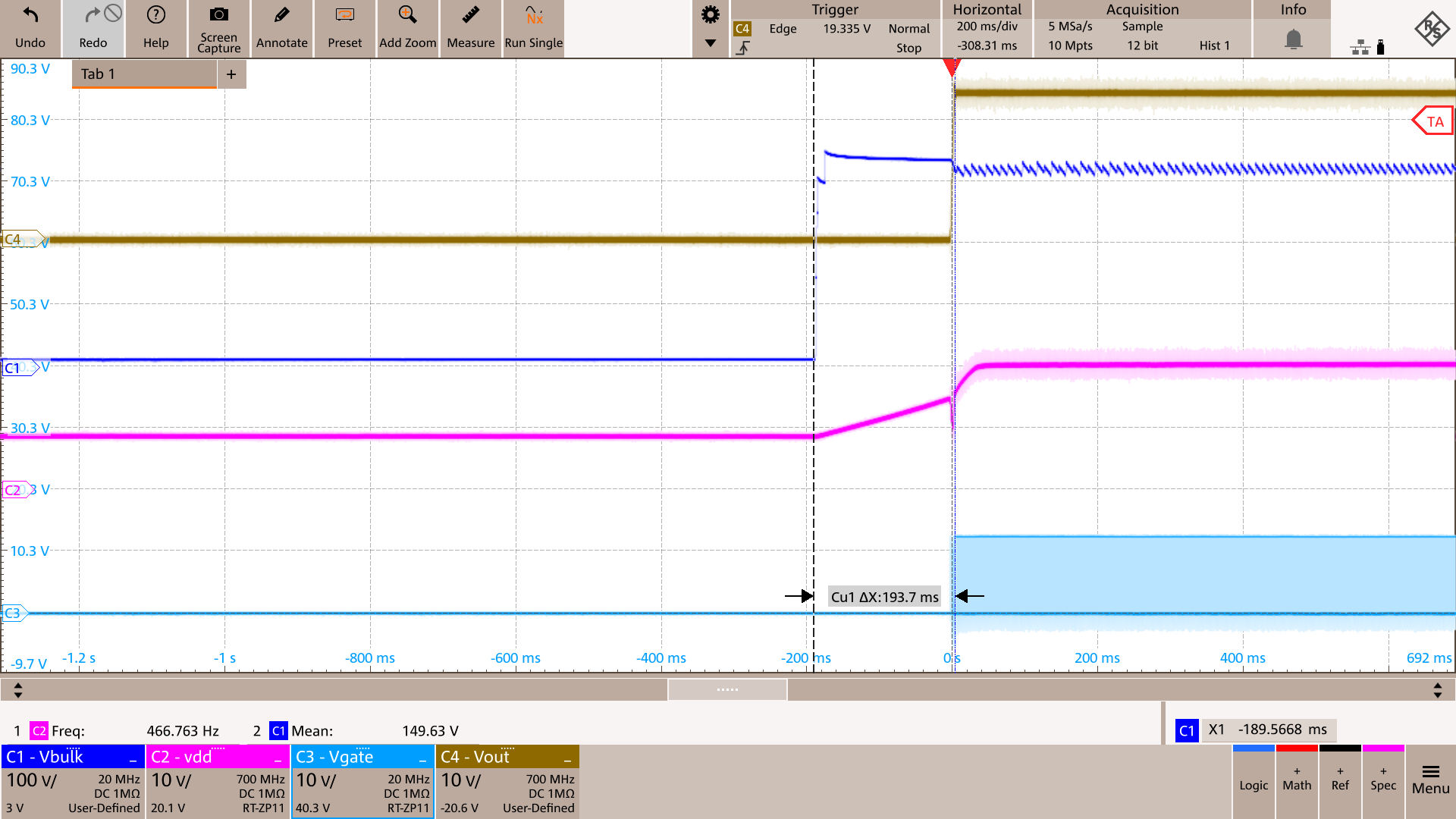

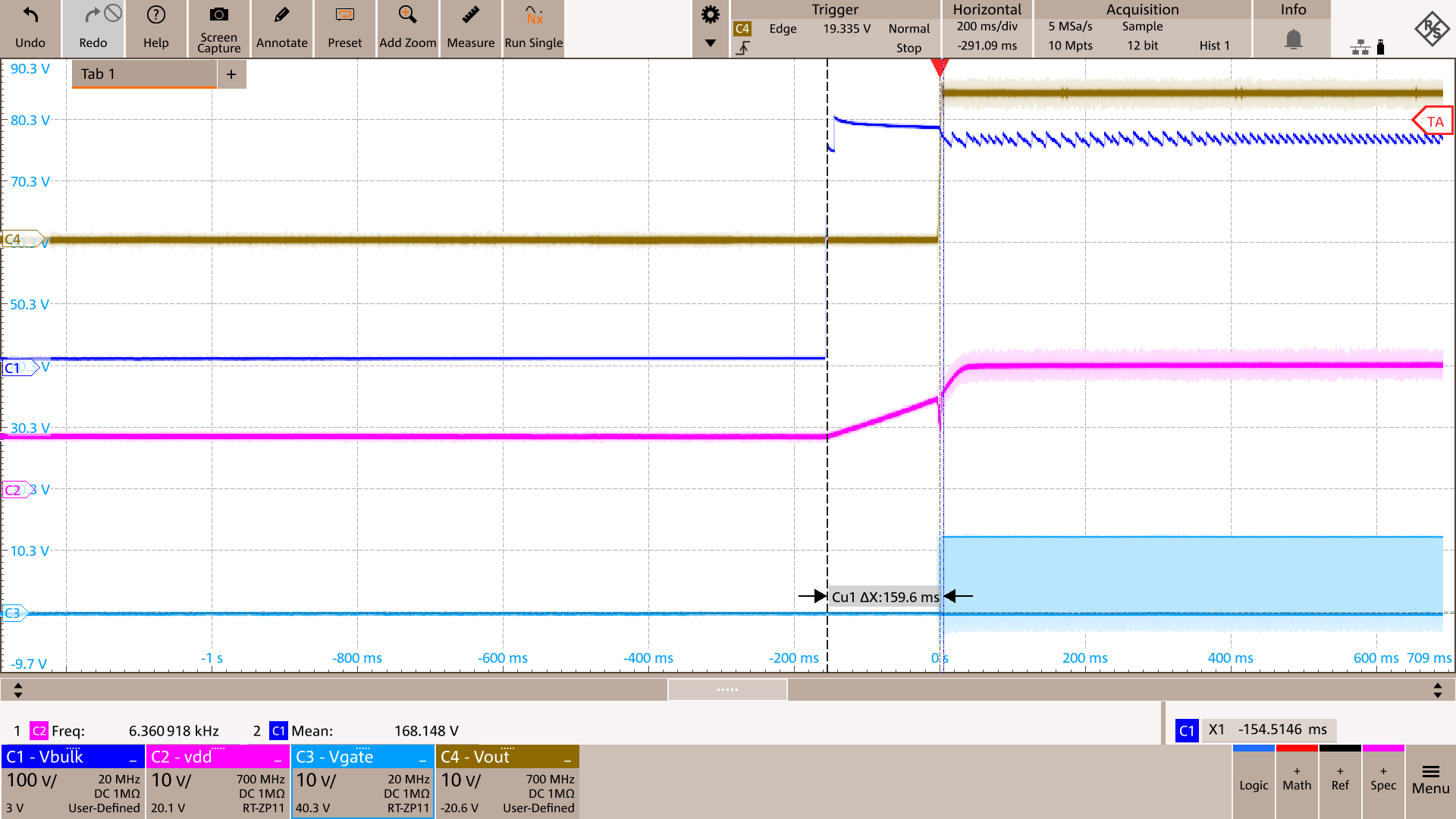

CH1 =VBULK , CH2 = VCC, CH3 = VGATE, CH4 = VOUT

Figure 8-4 Start-Up Waveforms at 85Vac and No Load

Figure 8-4 Start-Up Waveforms at 85Vac and No Load Figure 8-6 Start-Up Waveforms at 115Vac and No Load

Figure 8-6 Start-Up Waveforms at 115Vac and No Load Figure 8-8 Start-Up Waveforms at 230Vac and No Load

Figure 8-8 Start-Up Waveforms at 230Vac and No Load Figure 8-10 Start-Up Waveforms at 265Vac and No Load

Figure 8-10 Start-Up Waveforms at 265Vac and No Load Figure 8-5 Start-Up Waveforms at 85Vac and Full Load

Figure 8-5 Start-Up Waveforms at 85Vac and Full Load Figure 8-7 Start-Up Waveforms at 115Vac and Full Load

Figure 8-7 Start-Up Waveforms at 115Vac and Full Load Figure 8-9 Start-Up Waveforms at 230Vac and Full Load

Figure 8-9 Start-Up Waveforms at 230Vac and Full Load Figure 8-11 Start-Up Waveforms at 265Vac and Full Load

Figure 8-11 Start-Up Waveforms at 265Vac and Full Load