JAJSKM1C october 2019 – september 2021 UCC5870-Q1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Power Supplies

- 7.3.2 Driver Stage

- 7.3.3 Integrated ADC for Front-End Analog (FEA) Signal Processing

- 7.3.4 Fault and Warning Classification

- 7.3.5

Diagnostic Features

- 7.3.5.1 Undervoltage Lockout (UVLO) and Overvoltage Lockout (OVLO)

- 7.3.5.2 CLAMP, OUTH, and OUTL Clamping Circuits

- 7.3.5.3 Active Miller Clamp

- 7.3.5.4 DESAT based Short Circuit Protection (DESAT)

- 7.3.5.5 Shunt Resistor based Overcurrent Protection (OCP) and Short Circuit Protection (SCP)

- 7.3.5.6 Temperature Monitoring and Protection for the Power Transistors

- 7.3.5.7 Active High Voltage Clamping (VCECLP)

- 7.3.5.8 Two-Level Turn-Off

- 7.3.5.9 Soft Turn-Off (STO)

- 7.3.5.10 Thermal Shutdown (TSD) and Temperature Warning (TWN) of Driver IC

- 7.3.5.11 Active Short Circuit Support (ASC)

- 7.3.5.12 Shoot-Through Protection (STP)

- 7.3.5.13 Gate Voltage Monitoring and Status Feedback

- 7.3.5.14 VGTH Monitor

- 7.3.5.15 Cyclic Redundancy Check (CRC)

- 7.3.5.16 Configuration Data CRC

- 7.3.5.17 SPI Transfer Write/Read CRC

- 7.3.5.18 TRIM CRC Check

- 7.4 Device Functional Modes

- 7.5 Programming

- 7.6 Register Maps

- 8 Applications and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

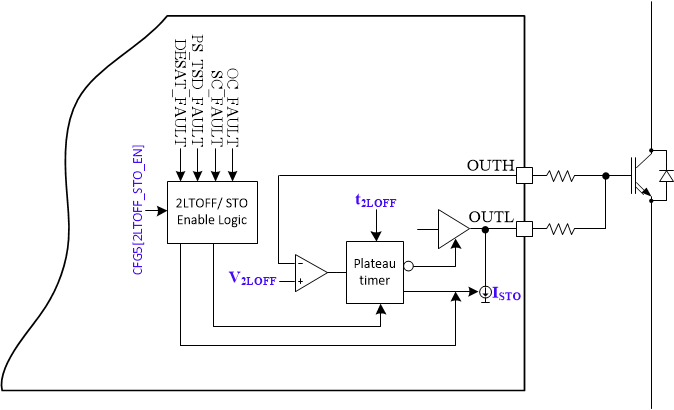

7.3.5.8 Two-Level Turn-Off

The two-level turn-off (2LTOFF) function limits the transistor current during shutoff during certain fault conditions. The 2LTOFF function is enabled for PS_OC, PS_SC, PS_TSD, and/or DESAT faults using the CF5[2LTOFF_STO_EN] bits (CFG5). When 2LTOFF is triggered, the gate of the power transistor is controlled to operate the transistor in the linear region where the channel current is controlled by the voltage level on the gate terminal. The power transistor current is reduced by controlling the gate voltage to a intermediate voltage, or plateau voltage, (V2LOFF) for t2LOFF, and then ramping the gate down to turn the power transistor off. While 2LTOFF is active, OUTL sinks current to discharge the gate capacitor of the power switch to the plateau voltage. The gate discharge current is programmable using the CFG8[GD_2LOFF_CURR] bits (CFG8). The plateau voltage level and duration are configured using the CFG8[GD_2LOFF_VOLT] and CFG8[GD_2LOFF_TIME] bits (CFG8), respectively. After holding the plateau voltage for the programmed time, the gate is discharged fully using the soft turn-off current or pulled low as normal with the OUTL driver. Enable the soft turn off current using the CFG8[GD_2LOFF_STO_EN] bit (CFG8). The implementation diagram and timing scheme are presented in Figure 7-24 and Figure 7-25, respectively.

Figure 7-24 Block diagram of implementation of

two-level turn-off function

Figure 7-24 Block diagram of implementation of

two-level turn-off function Figure 7-25 Timing scheme of implementation of

two-level turn-off function

Figure 7-25 Timing scheme of implementation of

two-level turn-off function