-

DLPC4420 DLP ディスプレイ・コントローラ

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics

- 6.6 System Oscillators Timing Requirements

- 6.7 Test and Reset Timing Requirements

- 6.8 JTAG Interface: I/O Boundary Scan Application Timing Requirements

- 6.9 Port 1 Input Pixel Timing Requirements

- 6.10 Port 3 Input Pixel Interface (via GPIO) Timing Requirements

- 6.11 DMD LVDS Interface Timing Requirements

- 6.12 Synchronous Serial Port (SSP) Interface Timing Requirements

- 6.13 Programmable Output Clocks Switching Characteristics

- 6.14 Synchronous Serial Port Interface (SSP) Switching Characteristics

- 6.15 JTAG Interface: I/O Boundary Scan Application Switching Characteristics

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

- 重要なお知らせ

DATA SHEET

DLPC4420 DLP ディスプレイ・コントローラ

このリソースの元の言語は英語です。 翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

1 特長

- デジタル・マイクロミラー・デバイス (DMD) を使って最大 4K の超高精細 (UHD) 解像度ディスプレイに対応するデュアル DLP コントローラ:

- 60Hz で最大 4K

- 240Hz で最大 1080p

- 120Hz (3D) で最大 1080p

- シングル 30 ビットまたはデュアル 60 ビットの入力ピクセル・インターフェイスを提供:

- RGB データ・フォーマット

- カラーごとに 8、9、10 ビット

- 最大 600MHz のピクセル・クロック (デュアル・コントローラ、デュアル 30 ビット・モード時)

- 高速、低電圧差動信号 (LVDS) DMD インターフェイス

- 150MHz の ARM946™ マイクロプロセッサ

- マイクロプロセッサ・ペリフェラル

- プログラマブル・パルス幅変調 (PWM) およびキャプチャ・タイマ

- 3 つの I2C ポート、3 つの UART ポート、3 つの SSP ポート

- 1 つの USB 1.1 セカンダリ・ポート

- 画像処理

- 複数の画像処理アルゴリズム

- フレーム・レート変換

- 色座標調整

- プログラム可能な色空間の変換

- プログラム可能なデガンマおよびスプラッシュ

- 3D ディスプレイの統合サポート

- 1D 矩形補正

- クロック生成回路内蔵

- 単一の 20MHz クリスタルで動作

- スペクトラム拡散クロッキングを内蔵

- 外部メモリに対応

- マイクロプロセッサおよび PWM シーケンス用のパラレル・フラッシュ

- 516 ピンのプラスチック・ボール・グリッド・アレイ・パッケージ

- LED およびレーザー・ハイブリッド照明をサポート

2 アプリケーション

3 概要

DLPC4420 は、DLP® ディスプレイ・チップセット用のデジタル・ディスプレイ・コントローラです。このチップセットは、DLPC4420 ディスプレイ・コントローラ、DLP デジタル・マイクロミラー・デバイス (DMD)、DLPA100 コントローラ・パワー・マネージメント・デバイス、DLPA300 DMD マイクロミラー・ドライバで構成されます (DMD データシートを参照)。このソリューションは、簡素なシステムで高解像度と高輝度を必要とするディスプレイ・システムに最適です。信頼性の高い動作を保証するため、DLPC4420 ディスプレイ・コントローラは、DLP DMD および対応する DLP パワー・マネージメント・デバイスと常に一緒に使う必要があります。

デバイス情報

| 部品番号(1) | パッケージ | 本体サイズ (公称) |

|---|---|---|

| DLPC4420 | ZPC (516) | 27.00mm × 27.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

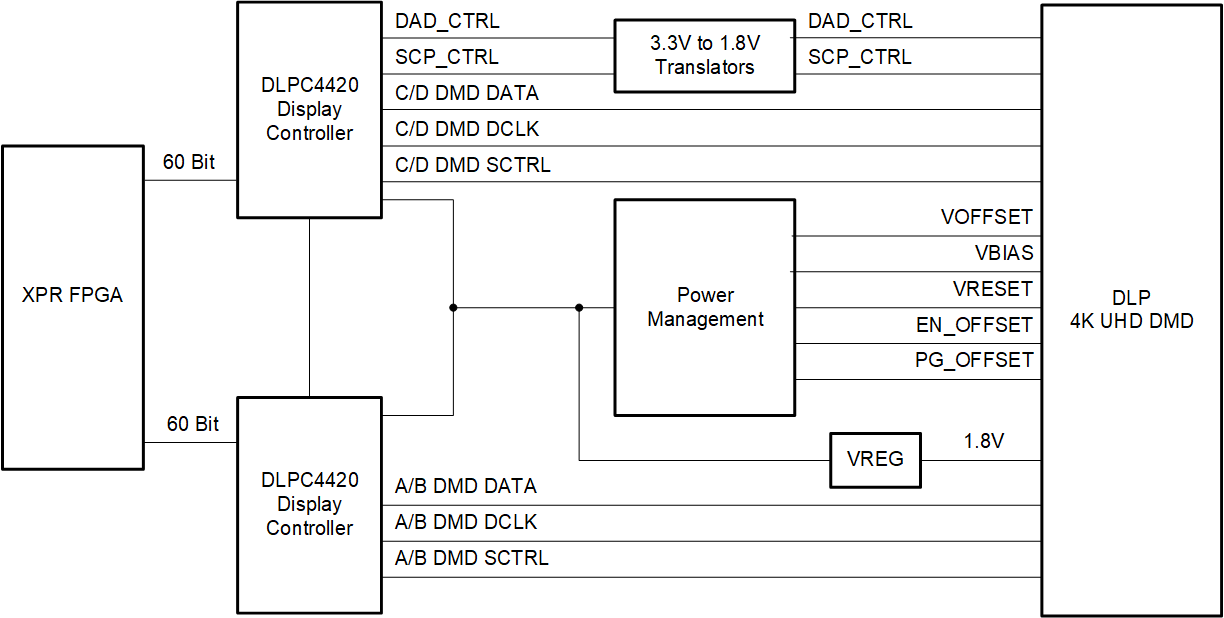

簡略回路図

簡略回路図