DLPU132A October 2023 – March 2024 DLPC964

- 1

- Description

- Get Started

- Features

- Applications

- 6

- 1Evaluation Module Overview

-

2Hardware

- 2.1 DLPLCRC964EVM Power Supply Requirements

- 2.2

DLPLCRC964EVM Connections

- 2.2.1 J1, J2 - HPC FMC Connector (Male)

- 2.2.2 J3 - Input Power

- 2.2.3 J4 - TestMux Connector

- 2.2.4 J6, J8 - I2C Address Selectors

- 2.2.5 J7 - JTAG Boundary Scan

- 2.2.6 J9 - Micro-B USB Connector

- 2.2.7 J10 - I2C Connector

- 2.2.8 J11 - 3.3V GPIO Connector

- 2.2.9 J12 - 1.8V GPIO Connector

- 2.2.10 J13, J14, J15, J16 - DMD EVM Board Flex Cable Connectors

- 2.2.11 J17 - DMD_DMux Connector

- 2.2.12 J18 - FanSink Connector

- 2.2.13 Switches

- 2.2.14 DLP LightCrafter DLPC964 LEDs

- 2.3 EVM Assembly

- 2.4 Quick Start

- 3Software

- 4Hardware Design Files

- 5Additional Information

- 6Related Documentation from Texas Instruments

- 7Revision History

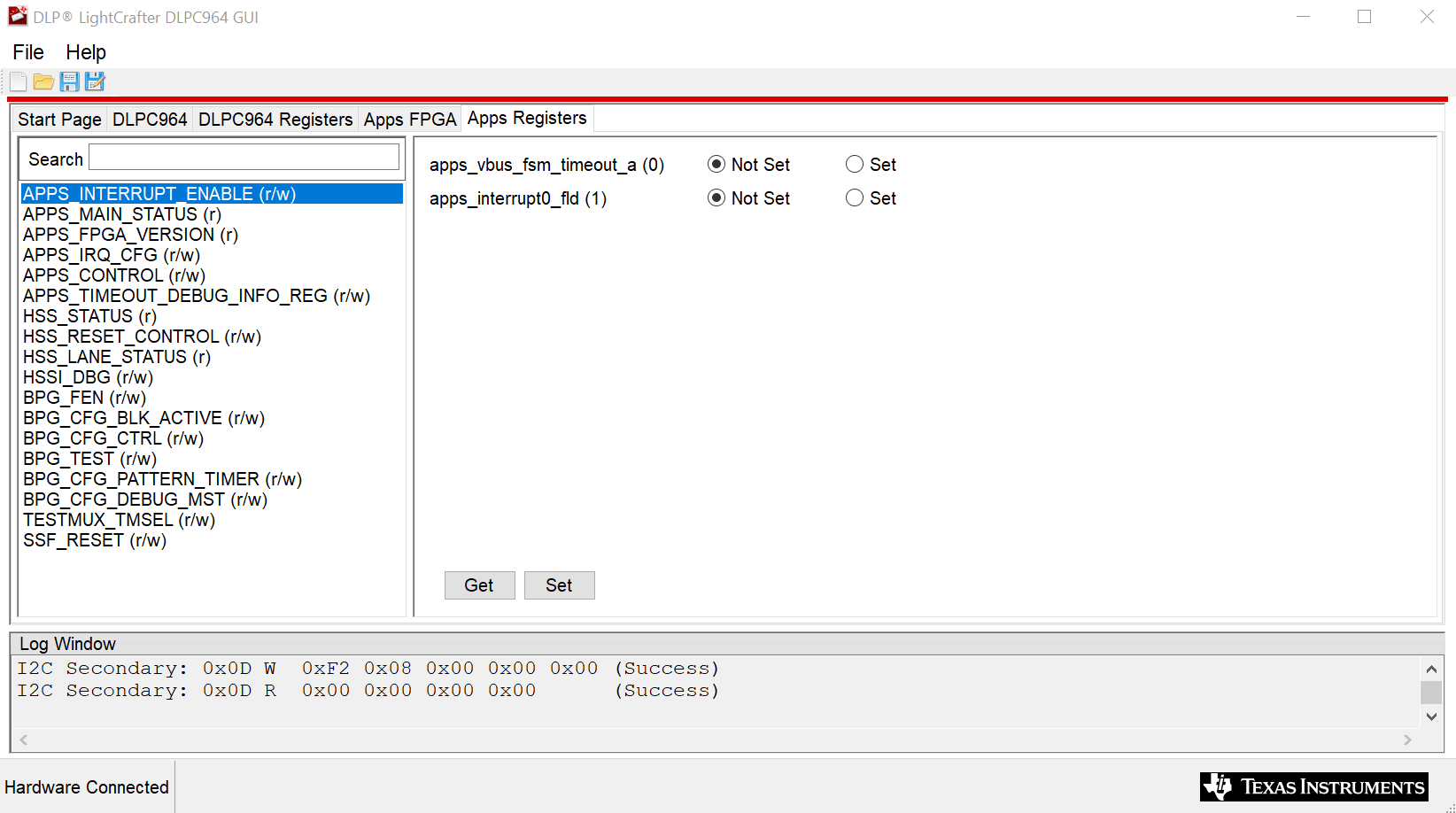

3.1.4.5 Apps FPGA Registers Tab

The Apps FPGA Registers tab uses the I2C Interface to communicate with the Apps FPGA registers. This tab shows the Apps FPGA register list and settings for each register which use Get/Set buttons to read/write to specific registers.

Note: Access to the Apps FPGA registers must not begin until

INIT_DONE has transitioned high (logic 1).

Figure 3-18 Apps FPGA Register

List

Figure 3-18 Apps FPGA Register

ListRegister Definitions

The following designations are used throughout this section of the document:

- R - designates read only

- W - designates write only

- R/W - designates read and write

- S - designates status of register

- I - designates interrupt only

- P - designates pulse only

Please visit the DLPC964 data sheet for detailed descriptions of each Apps FPGA register offered in the DLPC964 GUI.