設計目標

| 入力 | 出力 | 電源 | |

|---|---|---|---|

| シングル エンド | 差動 | Vcc | Vee |

| 0V~1V | 16Vpp | 10V | 0V |

| 出力同相 | 3dB 帯域幅 | AC ゲイン (Gac) |

|---|---|---|

| 5V | 3MHz | 16 V/V |

設計の説明

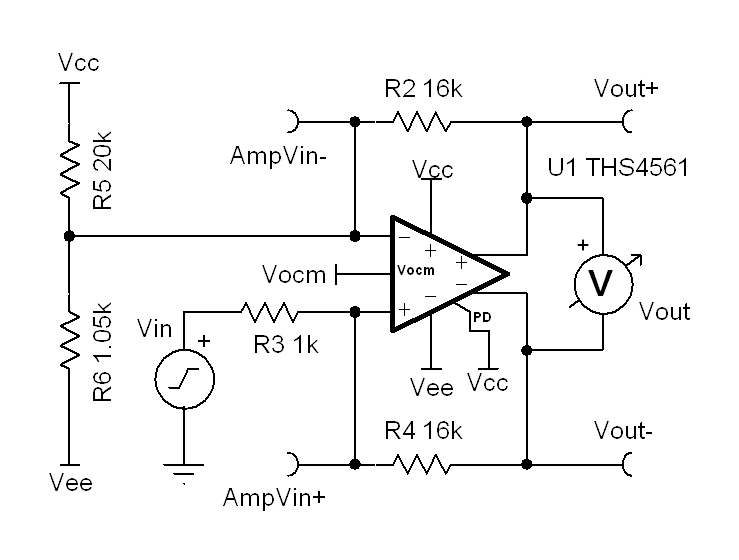

この設計は、完全差動アンプ (FDA) を、シングル エンド入力差動出力アンプとして使用します。

デザイン ノート

- 比 R4/R3 (= R2/(R5||R6)) はアンプのゲインを設定します。

- シングル エンド入力と差動入力の主な相違点は、シングル エンド入力は利用可能な入力スイングが差動入力の半分しかないことです。これは、入力電圧の片方が基準電圧に固定されているためです。

- この基準電圧は、測定される差動入力に極性反転が起こるよう、最小入力ではなく入力信号範囲の中間に設定することを推奨します。これにより、出力がクロスオーバーでき、FDA で可能な出力スイングが 2 倍になります。

- 基準電圧のインピーダンスは、信号入力抵抗と等しい必要があります。これは、正しい基準電圧とインピーダンスのテブナン等価回路を持つ抵抗分圧器を作成することで実現できます。

設計手順

- Vs = 10V から 0.5V、1kΩ の基準電圧を生成する分圧抵抗を求めます。

- 最低入力 0V、最高入力 1V で、Vocm = 5V について利用可能な 9.4V の範囲内の出力が得られることを確認します。

抵抗分圧器は 0.5V の基準電圧として機能するため、0V の VIN に対して測定される差動入力は次のようになります。

- 出力は次のようになります。

- 同様に、1V 入力については次のようになります。

基準電圧が 0V の場合、1V の入力に対する出力電圧は、アンプの最大出力範囲を超えます。

設計シミュレーション

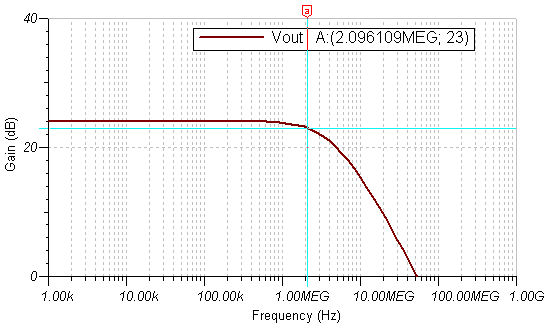

AC シミュレーション結果

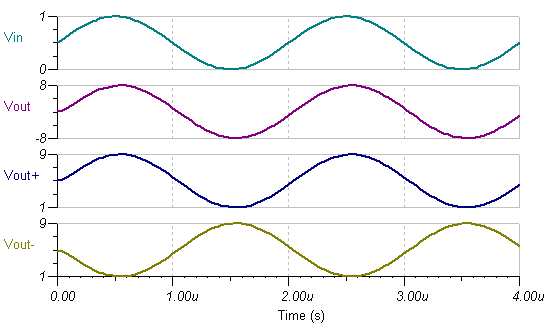

AC シミュレーション結果 過渡シミュレーション結果

過渡シミュレーション結果設計の参照資料

テキサス・インスツルメンツ、『差動 ADC を駆動するフロントエンドの設計』、プレシジョン ラボ ビデオ

設計に使用されているオペアンプ

| THS4561 | |

|---|---|

| Vss | 3V~13.5V |

| VinCM | Vee-0.1V~Vcc-1.1V |

| Vout | Vee+0.2V~Vcc-0.2 |

| Vos | 未定 |

| Iq | 未定 |

| Ib | 未定 |

| UGBW | 70 MHz |

| SR | 4.4V/µs |

| チャネル数 | 1 |

| THS4561 | |

設計の代替オペアンプ

| THS4131 | |

|---|---|

| Vss | 5V~33V |

| VinCM | Vee+1.3V~Vcc-0.1V |

| Vout | 条件によって変化 |

| Vos | 2 mV |

| Iq | 14mA |

| Ib | 2µA |

| UGBW | 80 MHz |

| SR | 52V/µs |

| チャネル数 | 1 |

| THS4131 | |

商標

All trademarks are the property of their respective owners.

重要なお知らせと免責事項

TI は、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションが適用される各種規格や、その他のあらゆる安全性、セキュリティ、またはその他の要件を満たしていることを確実にする責任を、お客様のみが単独で負うものとします。上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売条件(www.tij.co.jp/ja-jp/legal/termsofsale.html)、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用されるTI の保証または他の保証の放棄の拡大や変更を意味するものではありません。IMPORTANT NOTICE

Copyright © 2024, Texas Instruments Incorporated

日本語版 日本テキサス・インスツルメンツ株式会社