JAJA605A January 2019 – September 2024 THS4131 , THS4561

設計目標

| 入力 | 出力 | 電源 | |

|---|---|---|---|

| シングル エンド | 差動 | Vcc | Vee |

| 0V~1V | 16Vpp | 10V | 0V |

| 出力同相 | 3dB 帯域幅 | AC ゲイン (Gac) |

|---|---|---|

| 5V | 3MHz | 16 V/V |

設計の説明

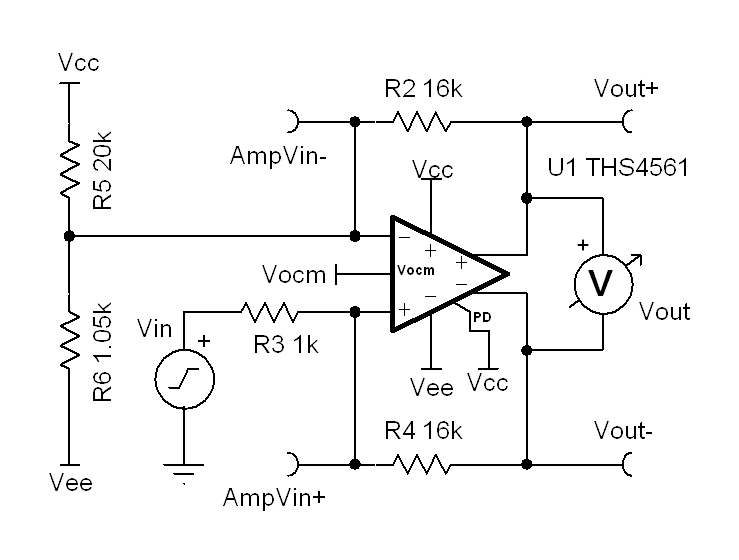

この設計は、完全差動アンプ (FDA) を、シングル エンド入力差動出力アンプとして使用します。

デザイン ノート

- 比 R4/R3 (= R2/(R5||R6)) はアンプのゲインを設定します。

- シングル エンド入力と差動入力の主な相違点は、シングル エンド入力は利用可能な入力スイングが差動入力の半分しかないことです。これは、入力電圧の片方が基準電圧に固定されているためです。

- この基準電圧は、測定される差動入力に極性反転が起こるよう、最小入力ではなく入力信号範囲の中間に設定することを推奨します。これにより、出力がクロスオーバーでき、FDA で可能な出力スイングが 2 倍になります。

- 基準電圧のインピーダンスは、信号入力抵抗と等しい必要があります。これは、正しい基準電圧とインピーダンスのテブナン等価回路を持つ抵抗分圧器を作成することで実現できます。

設計手順

- Vs = 10V から 0.5V、1kΩ の基準電圧を生成する分圧抵抗を求めます。

- 最低入力 0V、最高入力 1V で、Vocm = 5V について利用可能な 9.4V の範囲内の出力が得られることを確認します。

抵抗分圧器は 0.5V の基準電圧として機能するため、0V の VIN に対して測定される差動入力は次のようになります。

- 出力は次のようになります。

- 同様に、1V 入力については次のようになります。

注:

基準電圧が 0V の場合、1V の入力に対する出力電圧は、アンプの最大出力範囲を超えます。

設計シミュレーション

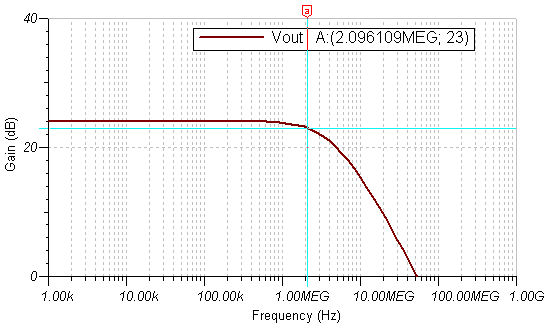

AC シミュレーション結果

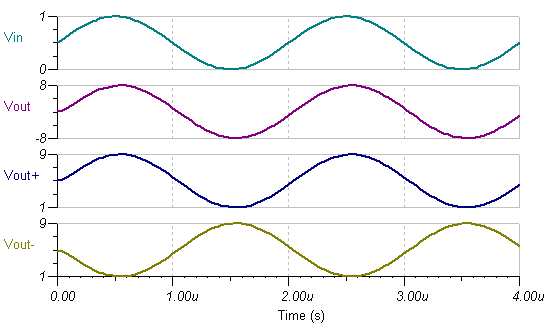

AC シミュレーション結果 過渡シミュレーション結果

過渡シミュレーション結果設計の参照資料

テキサス・インスツルメンツ、『差動 ADC を駆動するフロントエンドの設計』、プレシジョン ラボ ビデオ

設計に使用されているオペアンプ

| THS4561 | |

|---|---|

| Vss | 3V~13.5V |

| VinCM | Vee-0.1V~Vcc-1.1V |

| Vout | Vee+0.2V~Vcc-0.2 |

| Vos | 未定 |

| Iq | 未定 |

| Ib | 未定 |

| UGBW | 70 MHz |

| SR | 4.4V/µs |

| チャネル数 | 1 |

| THS4561 | |

設計の代替オペアンプ

| THS4131 | |

|---|---|

| Vss | 5V~33V |

| VinCM | Vee+1.3V~Vcc-0.1V |

| Vout | 条件によって変化 |

| Vos | 2 mV |

| Iq | 14mA |

| Ib | 2µA |

| UGBW | 80 MHz |

| SR | 52V/µs |

| チャネル数 | 1 |

| THS4131 | |