JAJA650A December 2018 – June 2024 ADS7142 , ISO224 , TLV9002

| ISO224 入力電圧 | ISO224 出力 (VOUTP – VOUTN) | ADS7142 入力 (擬似差動) | ADS7142デジタル出力 |

|---|---|---|---|

| 12V | 4V | 3.3V | FFFH |

| -12V | -4V | 0V | 000H |

| 電源および基準電圧 | |||

|---|---|---|---|

| VDD1 | VDD2 および Vcc | AVDD | GND |

| 4.5V~18V | 5V | 3.3V | 0V |

設計の説明

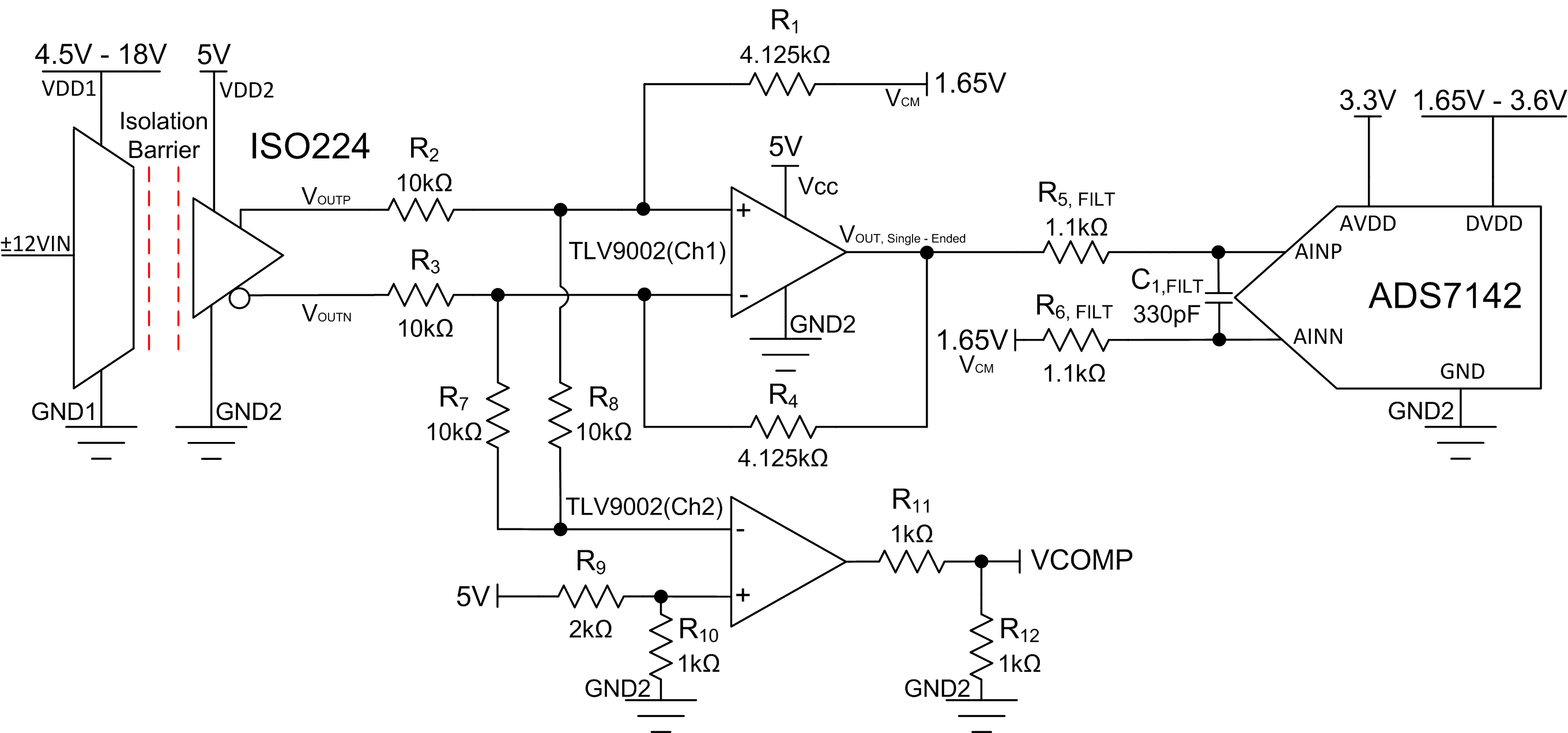

この回路は、ISO224 絶縁アンプ、TLV9002 オペアンプ、ADS7142 SAR ADC を活用して ±12V の絶縁電圧センシング測定を行います。ISO224 は ±12V のシングルエンド信号を ⅓V/V の固定ゲインで測定し、VDD2/2 の出力同相電圧で ±4V 絶縁差動出力電圧を生成できます。TLV9002 のチャネル 1 は、ADS7142 の入力範囲に合わせて ISO224 の出力をコンディショニングし、チャネル 2 は ISO224 のフェイルセーフ出力を監視します。ADS7142 は、フルスケール入力と AVDD 基準電圧の範囲が 1.65V~3.6V である 2 チャネル ADC です。このクックブック回路では ADS7142 の 2 チャネル入力を疑似差動構成で使用し、正と負の両方の信号を ISO224 で測定できます。この回路は、列車制御 / 管理システム、アナログ入力モジュール、インバータとモーター制御など、多くの産業用高電圧アプリケーションに適用できます。本書の「部品選定」の式と説明は、各システムの仕様や要件に応じてカスタマイズできます。

仕様

| 仕様 | 計算結果 | シミュレーション結果 |

|---|---|---|

| 140kSPS での ADC 過渡入力電圧セトリング | 403µV | 88µV |

| コンディショニングされた信号の範囲 | 0V~3.3V | 0V~3.3V |

| 入力でのノイズ | 262µVRMS | 526µVRMS |

| 閉ループ帯域幅 | 175kHz | 145kHz |

デザイン ノート

- 広い入力範囲、柔軟な電源構成、高い精度が理由で、ISO224 を選択しました。

- 超低消費電力、高集積、柔軟な電源構成、小さなサイズが理由で、ADS7142 を選択しました。

- コスト最適化、構成オプション、小さなサイズが理由で、TLV9002 オペアンプを選択しました。

- AVDD、VCM、ADC の同相電圧を設定する AINN への疑似差動入力には、低インピーダンスかつ低ノイズの電源を選択します。

- ADC のフルスケール範囲と同相の仕様を特定します。これについては「部品選定」で述べます。

- 歪みを最小限に抑えるため、CFILT には C0G コンデンサを選択します。

- 最良の性能を得るため、RFILT1,2 には 0.1% 20ppm/℃以下の薄膜抵抗を使用して、歪みを最小限に抑えることを考慮します。

- 『Understanding and Calibrating the Offset and Gain for ADC Systems』で、誤差解析の方法を説明しています。ゲイン、オフセット、ドリフト、およびノイズの誤差を最小限に抑える方法については、リンク先をご覧ください。

- TI プレシジョン ラボ - ADC トレーニング ビデオ シリーズでは、電荷バケツ回路の RFILT と CFILT を選択する方法について解説しています。これらの部品の値はアンプの帯域幅、データ コンバータのサンプリング レート、データ コンバータの設計に依存します。ここに示す値は、この例のアンプとデータ コンバータで適切なセトリングと AC 性能を実現します。設計を変更する場合は、別の RC フィルタを選定する必要があります。最高水準のセトリングと AC 性能を実現する RC フィルタの選定方法については、『Introduction to SAR ADC Front-End Component Selection』を参照してください。

部品選定

- 入力電圧範囲に基づいて絶縁アンプを選択し、出力同相電圧および出力電圧の範囲を決定します。

ISO224 の電源には、ハイサイド電源に 4.5V~18V、ローサイド電源に 4.5V~5.5V が使えます。ISO224 のシングルエンド入力範囲は ±12V、ゲインは ⅓V/V 固定であるため、この例では同相電圧 VDD2 / 2 (2.5V) で ±4V の差動出力が得られます。

- サイズが小さく低消費電力の ADC を選択します。

ADS7142 は、疑似差動構成で使用できる小型低消費電力の 2 チャネル ADC です。最大入力範囲は基準電圧により設定され、この例では AVDD (3.3V) と同じです。

疑似差動測定に必要な ADC 同相電圧を求めます。

- ISO224 の ±4V 差動、2.5V 同相出力を、ADS7142 の 3.3V 疑似差動、1.65V 同相入力に変換できるオペアンプを選択します。また、ISO224 のフェイルセーフ出力機能を監視できる 2 番目のチャネルを備えたオペアンプを選択することを推奨します。

TLV9002 は、コストの制約が厳しい小型アプリケーション用に最適化された 2 チャネル、レール ツー レール入出力アンプです。

チャネル 1 を使用して、ISO224 の ±4V 差動、2.5V 同相出力を、1.65V の同相電圧で 3.3V ピークの疑似差動出力に変換します。R1 = R4 かつ R2 = R3 の場合、伝達関数は次の式で設定されます。

この信号は ±4V から 3.3V に変換する必要があります。すなわち、信号を 3.3V/±4V = 3.3V/8V の割合で減衰させる必要があります。前に計算した値 (1.65V) を VCM に代入し、R2 と R3 を 10kΩ に設定すると、次の式が得られます。

R1 と R4 についてこの式を解くと、4.125kΩ の値が得られます。

このトピックの詳細については、『差動出力 (絶縁) アンプのシングルエンド入力 ADC への接続』アプリケーション ブリーフを参照してください。

TLV9002 のチャネル 2 は、ISO224 のフェイルセーフ出力機能の監視に使用します。ISO224 のフェイルセーフ出力機能は、VIN ピンの入力信号にかかわらず、ハイサイド電源 (VDD1) が失われると常に有効になります。TLV9002 のチャネル 2 の出力 (VCOMP) はシステム コントローラの GPIO ポートに入力され、フェイルセーフ出力機能が有効な場合常に High に移行します。詳細については、『フェイルセーフ出力機能』アプリケーション ノートを参照してください。

- 入力信号のセトリングと 140kSPS のサンプル レートに合わせて R1FILT、R2FILT、CFILT を選択します。

TI Precision Labs のビデオ『Refine the RFILT and CFILT Values』では、RFILT とCFILT の選定方法を説明しています。最終的に、1.1kΩ と 330pF という値で、アクイジション時間内に最下位ビット (LSB) の 1/2 を優に下回るまでセトリングできることが分かりました。

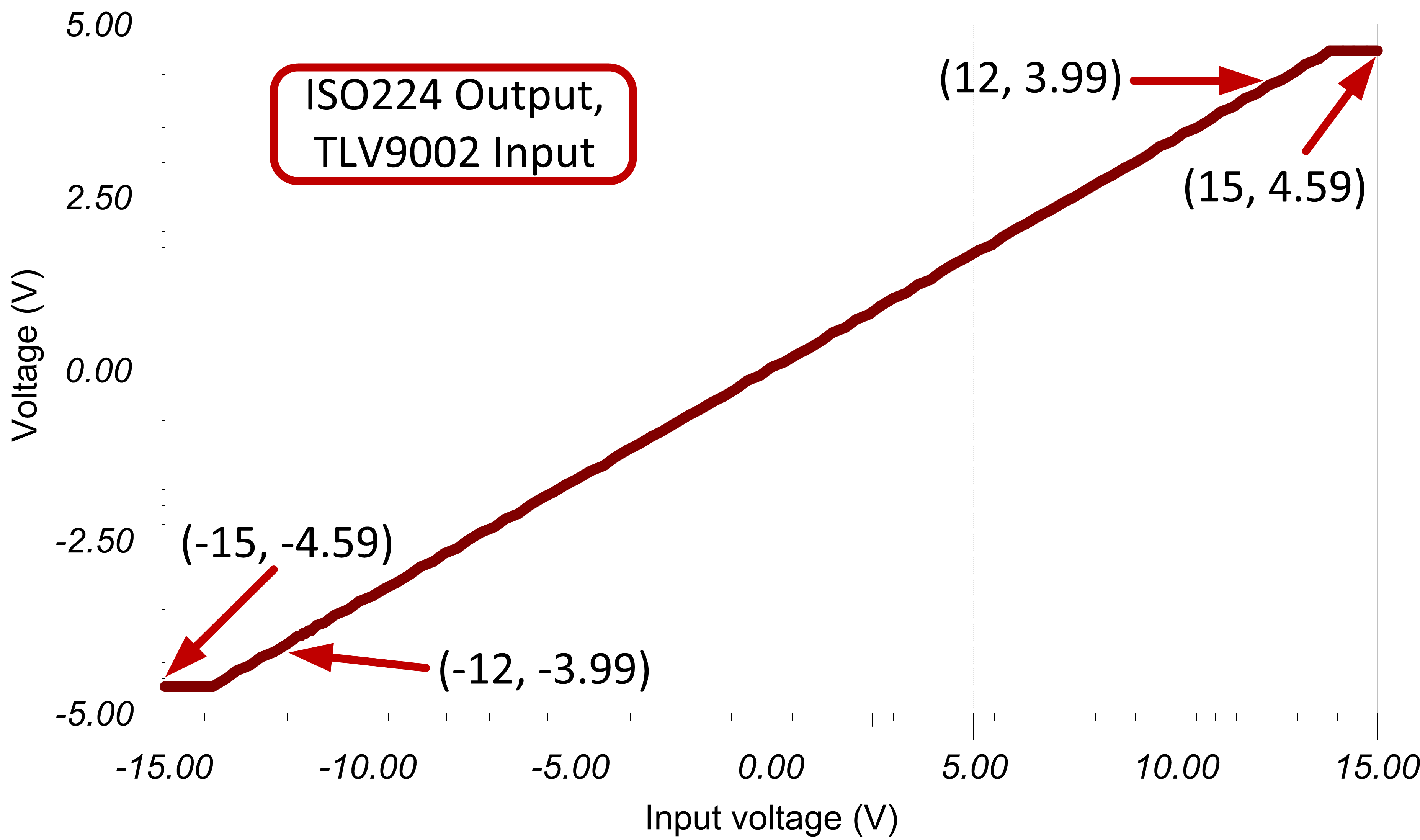

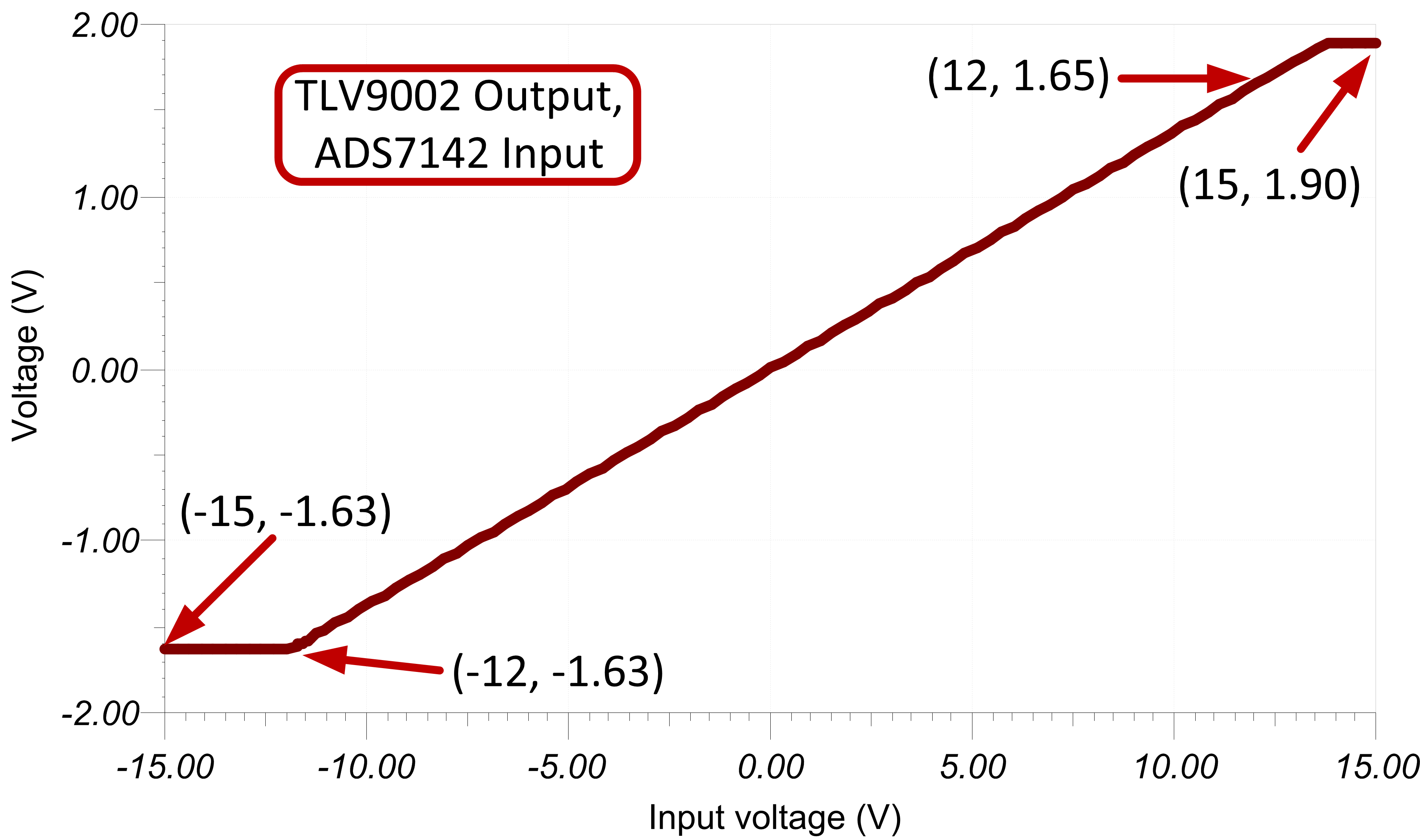

DC 伝達特性

次のグラフに、ISO224 への ±15V 入力信号による TLV9002 および ADS7142 への入力のシミュレーション結果を示します。最初のグラフに、ISO224 の ±VIN/3 のリニア出力と TLV9002 の入力を示します。2 番目のグラフに、TLV9002 がゲインをさらに VIN/2.43 に減少させ、同相電圧が 1.65V にシフトすることを示します。その結果、AVDD = VREF = 3.3V の場合、フルレンジ ±12V の入力信号で ADC の 0V~3.3V のフルスケール範囲 (FSR) を活用できます。

以下の伝達関数は、ISO224 と TLV9002 のゲインが 1/7.28V/V であることを示しています。

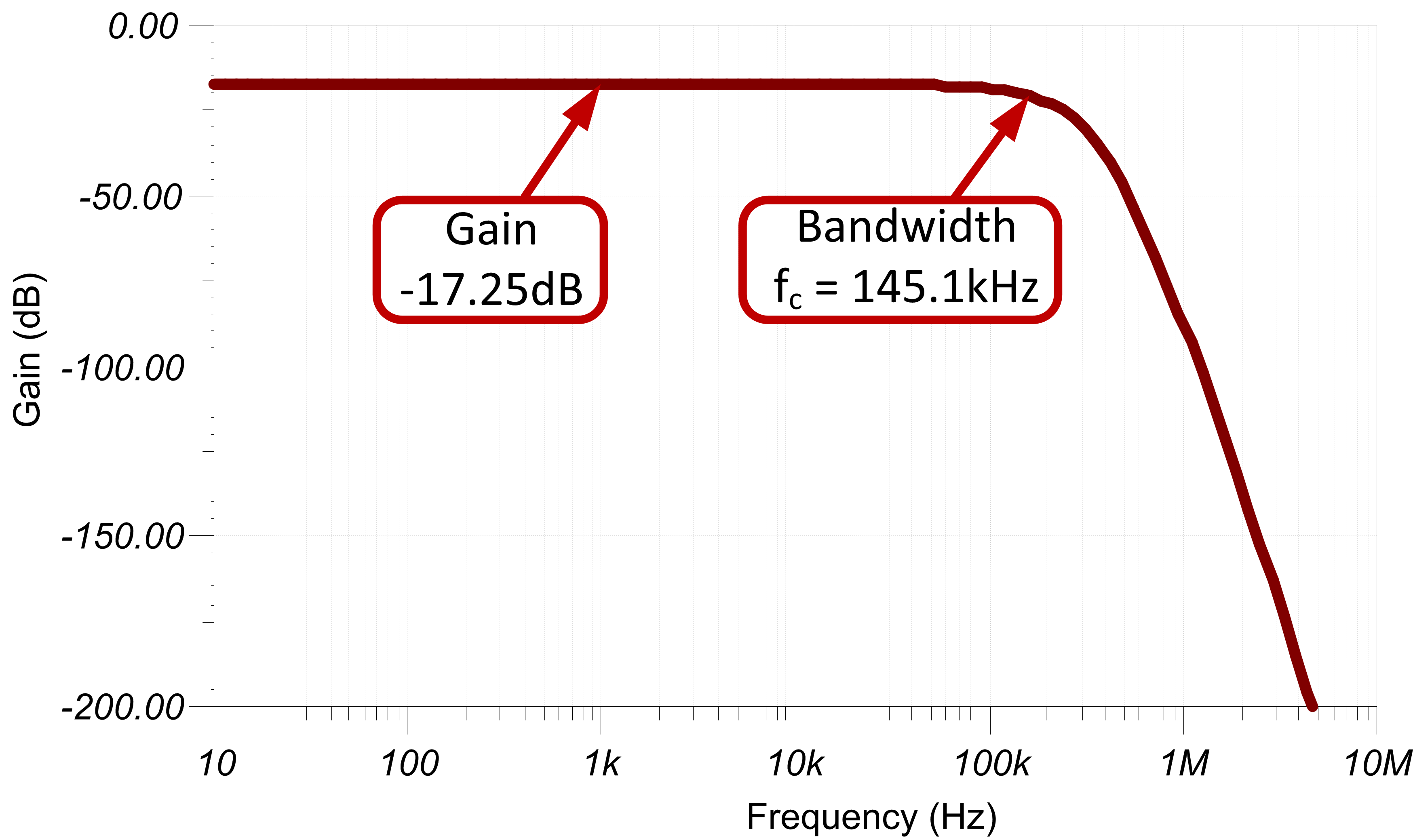

AC 伝達特性

信号チェーンの帯域幅のシミュレーション結果は約 145kHz、ゲインは -17.25dB であり、線形ゲインは約 0.137V/V (減衰率 1/7.28V/V) です。これは、システムのゲインの期待値と一致しています。

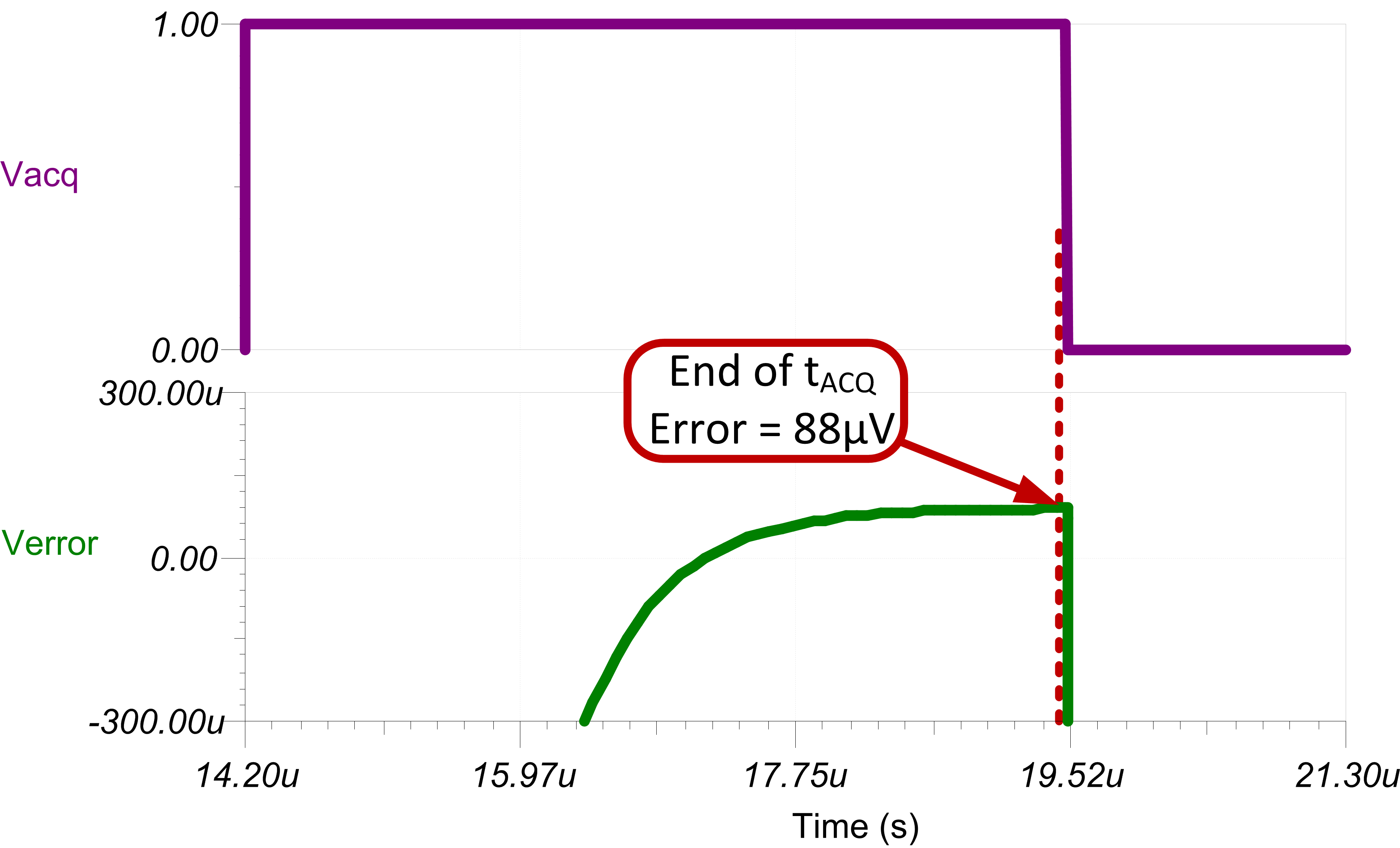

ADC 過渡入力電圧セトリング シミュレーション

以下に、アクイジション時間が 5.3μs のときの過渡セトリングのシミュレーション結果を示します。88μV のノイズは、0.5 × LSB の制限である 403μV 内に十分収まっています。この件の詳しい理論については、『Refine the Rfilt and Cfilt Values』を参照してください。

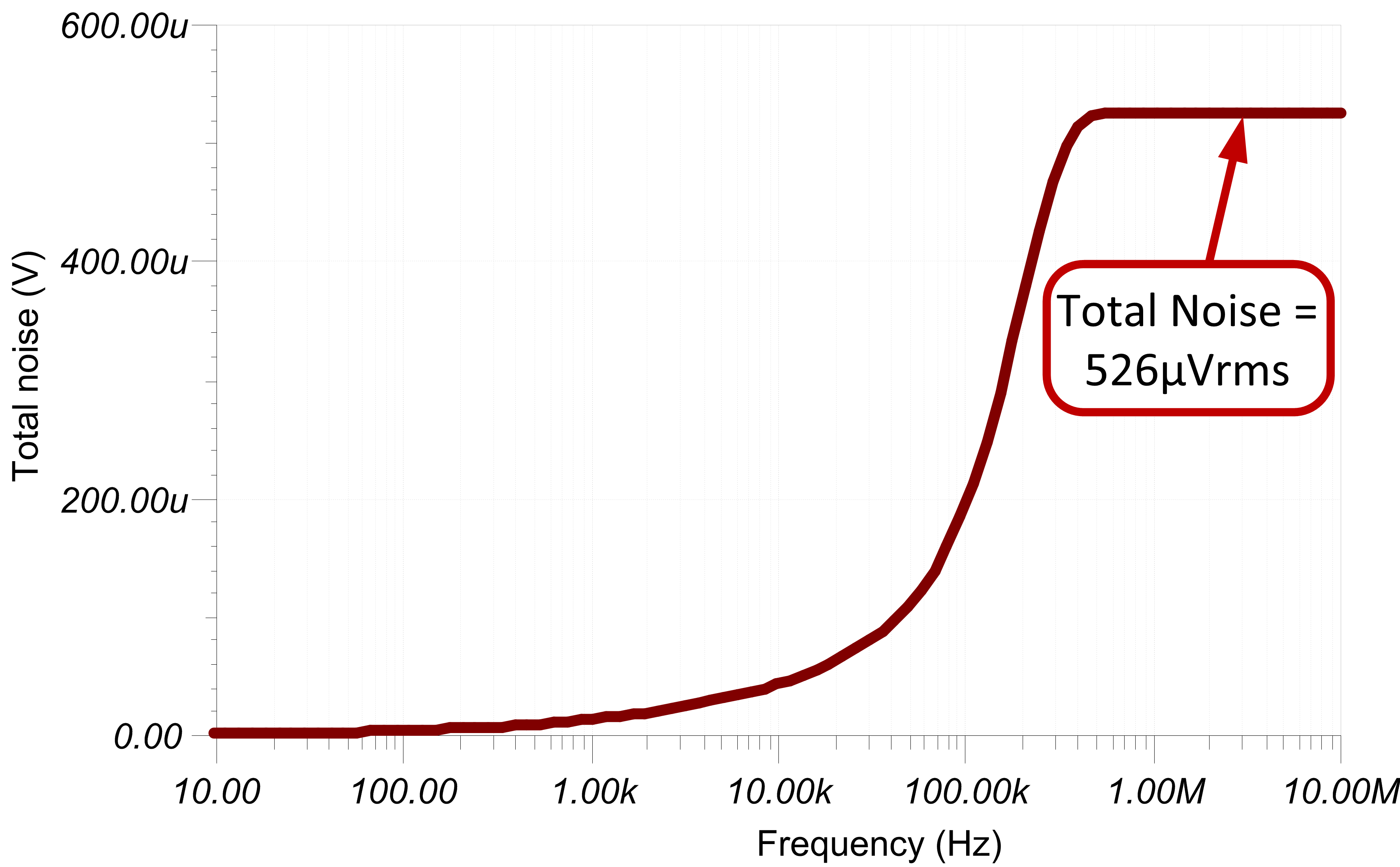

ノイズ シミュレーション

ADC の入力でのノイズのシミュレーション結果は、計算された期待値を上回っています。この差は、シミュレーション モデルでのノイズのピーキングが計算に含まれていないことが原因です。以下の式は、信号チェーンでは ISO224 のノイズが支配的で、TLV9002 からのノイズは無視できることを示しています。この件の詳しい理論については、『Calculating the Total Noise for ADC Systems』を参照してください。

設計の参照資料

テキサス・インスツルメンツの総合的な回路ライブラリについては、『アナログ エンジニア向け回路クックブック』を参照してください。

主要なファイルへのリンク

絶縁設計の TINA ファイル:SBAC226 を参照してください。

使用デバイス

| デバイス | 主な特長 | リンク | 類似デバイス |

|---|---|---|---|

| ISO224 | ±12V のシングルエンド入力範囲、⅓ の固定ゲイン、±4V の差動出力を生成、出力同相電圧 2.5V、ハイサイド電源 4.5V~18V、ローサイド電源 4.5V~5.5V、入力オフセット:25℃で ±5mV、最大値 ±42µV/℃、ゲイン誤差:25℃で ±0.3%、最大値 ±50ppm/℃、非直線性:最大値 ±0.01%、±1ppm/℃、1.25MΩ の高入力インピーダンス。 | ISO224 | www.ti.com/isoamps |

| ADS7142 | デュアル チャネル、フルスケール入力スパンと基準電圧を AVDD により設定、デフォルト 12 ビットの性能、高精度モードで 16 ビットの性能、600SPS において 0.45µA の非常に低い消費電流。 | ADS7142 | https://www.ti.com/PrecisionADCs |

| TLV9002 | デュアル チャネル、レール ツー レール入出力アンプ、2727nV/√Hz の低い広帯域ノイズ、±0.04mV の低い入力オフセット電圧。 | TLV9002 | https://www.ti.com/opamps |