JAJA724A november 2022 – march 2023 MSPM0L1227 , MSPM0L1227-Q1 , MSPM0L1228 , MSPM0L1228-Q1 , MSPM0L2227 , MSPM0L2227-Q1 , MSPM0L2228 , MSPM0L2228-Q1

9.4 基板層の選択方法と推奨されるスタックアップ

高速信号の反射を低減するには、ソース、シンク、伝送ライン間のインピーダンスをマッチングする必要があります。信号トレースのインピーダンスは、その形状と、基準プレーンに対する信号トレースの位置に依存します。

特定のインピーダンス要件に対する差動ペア間のパターン幅と間隔は、選択した PCB スタックアップによって異なります。PCB テクノロジーの種類やコスト要件に応じて、最小のパターン幅と間隔に制限があるため、必要なインピーダンスをすべて実現できるように、PCB スタックアップを選択する必要があります。

使用できる最小構成は 2 つのスタックアップです。複数の高速信号を持つ高密度 PCB には、4 層または 6 層の基板が必要です。

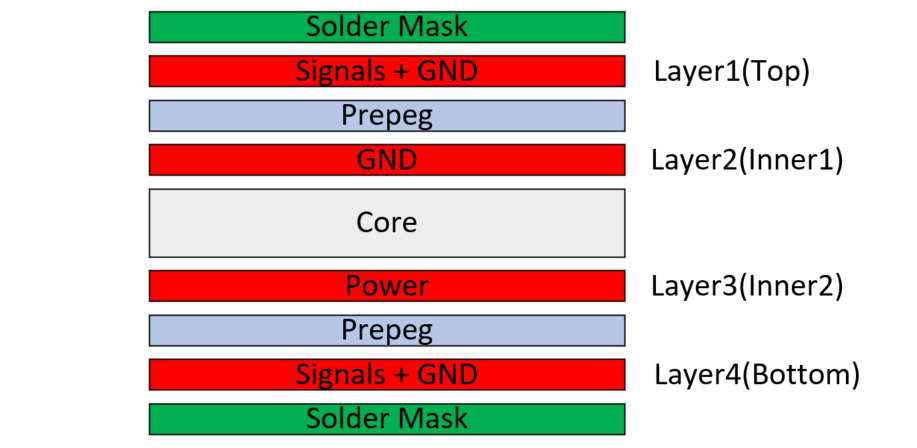

以下のスタックアップ (図 9-5を参照) は、スタックアップの評価と選択を支援するための出発点として使用できる 4 層の例です。これらのスタックアップ構成では、電源プレーンに隣接する GND プレーンを使用して静電容量を増加させ、GND と電源プレーンの間のギャップを小さくします。そのため、最上層の高速信号にはソリッドな GND リファレンス・プレーンがあり、EMC 放射の低減に役立ちます。これは、層数が増加し、各 PCB 信号層に GND リファレンスを配置することで、放射 EMC 性能がさらに向上するためです。

図 9-5 4 層 PCB スタックアップの例

図 9-5 4 層 PCB スタックアップの例システムがそれほど複雑ではない場合、高速信号や敏感なアナログ信号が存在しないため、2 つのスタックアップ構造で十分です。