JAJS204S December 2005 – November 2024 TPS74401

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Detailed Description

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

3 概要

TPS74401 低ドロップアウト (LDO) リニア レギュレータは、広範なアプリケーション向けの使いやすく堅牢な電力管理の選択肢です。ソフトスタートをユーザーがプログラム可能なため、スタートアップ時の容量性突入電流を低減して、入力電源のストレスを最小限に抑えることができます。ソフトスタートは単調性で、多くの種類のプロセッサおよび特定用途向け IC (ASIC) の電源供給向けに設計されています。イネーブル入力とパワー グッド出力により、外部レギュレータとの間でシーケンシングを簡単に行えます。高い柔軟性により、FPGA や DSP、その他特別なスタートアップ条件を持つアプリケーションのシーケンス制御条件を満たすソリューションを作成できます。

高精度の基準電圧およびエラー アンプは、負荷、ライン、温度、プロセスの全体にわたって 1% の精度を維持します。このデバイスは、出力コンデンサなしで (従来チップ)、あるいは任意の種類のコンデンサ ≥ 2.2µF で (新チップ)、安定動作します。このデバイスは、TJ = -40℃~125℃において完全に動作が規定されています。

パッケージ情報

| 部品番号 | パッケージ (1) | パッケージ サイズ(2) |

|---|---|---|

| TPS74401 | KTW (TO-263、7) | 10.1mm × 15.24mm |

| RGR (VQFN、20) | 3.5mm × 3.5mm | |

| RGW (VQFN、20) | 5mm × 5mm |

(1) 詳細については、「メカニカル、パッケージ、および注文情報」を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

代表的なアプリケーション回路

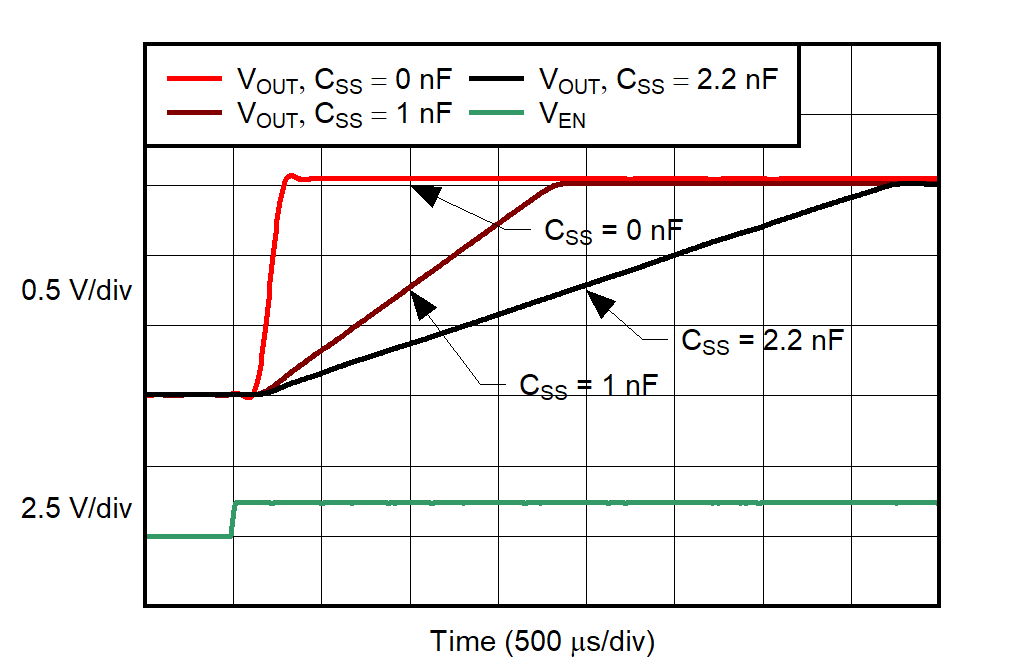

代表的なアプリケーション回路 ターンオン応答

ターンオン応答