JAJS616D May 2000 – July 2016 DS90LV047A

PRODUCTION DATA.

7 Parameter Measurement Information

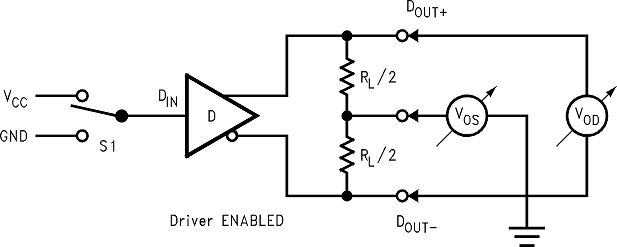

Figure 17. Driver VOD and VOS Test Circuit

Figure 17. Driver VOD and VOS Test Circuit

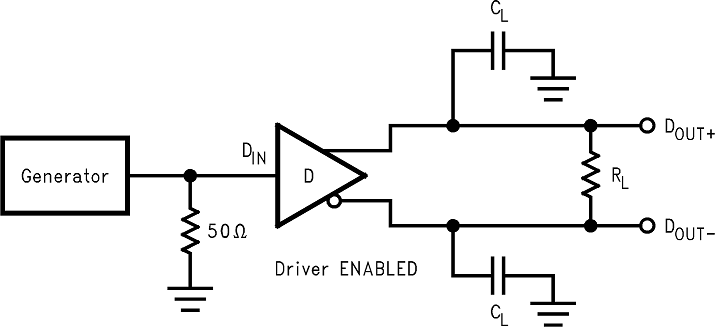

Figure 18. Driver Propagation Delay and Transition Time Test Circuit

Figure 18. Driver Propagation Delay and Transition Time Test Circuit

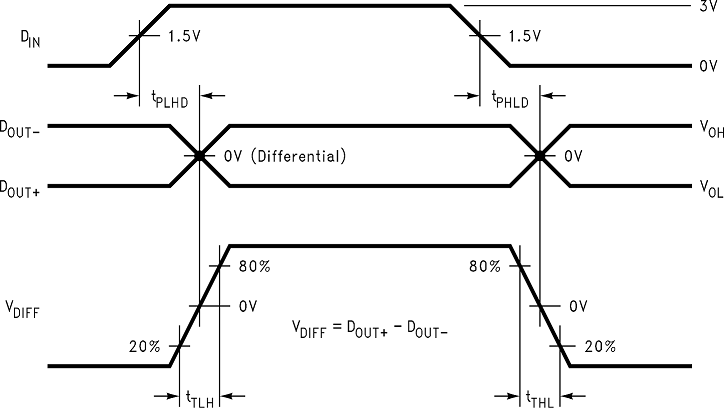

Figure 19. Driver Propagation Delay and Transition Time Waveforms

Figure 19. Driver Propagation Delay and Transition Time Waveforms

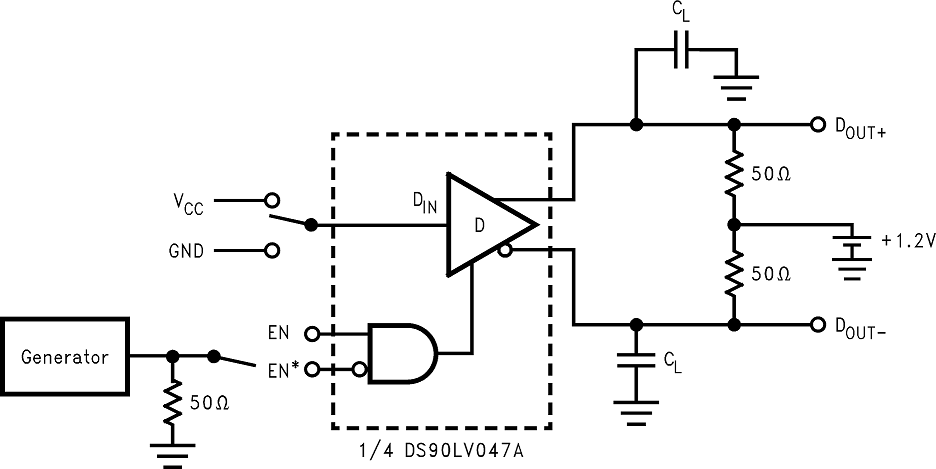

Figure 20. Driver TRI-STATE Delay Test Circuit

Figure 20. Driver TRI-STATE Delay Test Circuit

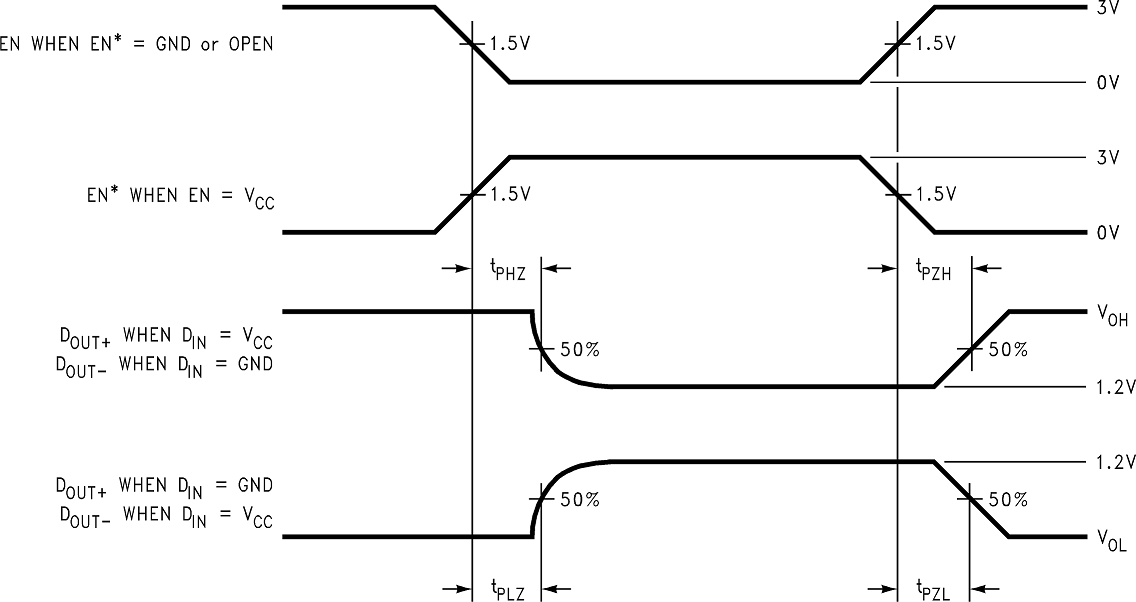

Figure 21. Driver TRI-STATE Delay Waveform

Figure 21. Driver TRI-STATE Delay Waveform