-

SN65DSI83-Q1 車載用、シングル・チャネル、MIPI® DSIからシングルリンクLVDSへのブリッジ

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3 Feature Description

- 8.4 Programming

- 8.5

Register Maps

- 8.5.1

Control and Status Registers Overview

- 8.5.1.1 CSR Bit Field Definitions – ID Registers

- 8.5.1.2 CSR Bit Field Definitions – Reset and Clock Registers

- 8.5.1.3 CSR Bit Field Definitions – DSI Registers

- 8.5.1.4 CSR Bit Field Definitions – LVDS Registers

- 8.5.1.5

CSR Bit Field Definitions – Video Registers

- 8.5.1.5.1 Register 0x20

- 8.5.1.5.2 Register 0x21

- 8.5.1.5.3 Register 0x24

- 8.5.1.5.4 Register 0x25

- 8.5.1.5.5 Register 0x28

- 8.5.1.5.6 Register 0x29

- 8.5.1.5.7 Register 0x2C

- 8.5.1.5.8 Register 0x2D

- 8.5.1.5.9 Register 0x30

- 8.5.1.5.10 Register 0x31

- 8.5.1.5.11 Register 0x34

- 8.5.1.5.12 Register 0x36

- 8.5.1.5.13 Register 0x38

- 8.5.1.5.14 Register 0x3A

- 8.5.1.5.15 Register 0x3C

- 8.5.1.6 CSR Bit Field Definitions – IRQ Registers

- 8.5.1

Control and Status Registers Overview

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

- 重要なお知らせ

DATA SHEET

SN65DSI83-Q1 車載用、シングル・チャネル、MIPI® DSIからシングルリンクLVDSへのブリッジ

このリソースの元の言語は英語です。 翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

1 特長

- 車載アプリケーションに対応

- 下記内容でAEC-Q100認定済み:

- デバイス温度グレード2: 動作時周囲温度–40℃~+105℃

- デバイスHBM ESD分類レベル3A

- デバイスCDM ESD分類レベルC6

- MIPI® D-PHYバージョン1.00.00物理レイヤ・フロントエンドおよびDisplay Serial Interface (DSI)バージョン1.02.00を実装

- シングル・チャネルDSIレシーバは、チャネルごとに1、2、3、4本のD-PHYデータ・レーンとして構成でき、レーンごとに最高1Gbpsで動作

- 18bppおよび24bppのDSIビデオ・パケットをRGB666およびRGB888フォーマットでサポート

- 最大解像度: 60fps WUXGA 1920×1200、18bppおよび24bppカラー(低ブランキング)。60fps、1366×768/1280×800 (18bppおよび24bpp)のディスプレイにも適切

- シングル・リンクLVDS用出力

- シングル・チャネルDSIからシングル・リンクLVDSへの動作モードをサポート

- LVDS出力クロック範囲: 25MHz~154MHz

- LVDSピクセル・クロックはフリーランニングの連続D-PHYクロックまたは外部リファレンス・クロック(REFCLK)により供給

- 1.8VのメインVCC電源

- 低消費電力機能として、SHUTDOWNモード、低減LVDS出力電圧スイング、同相、MIPI超低消費電力状態(ULPS)をサポート

- PCB配線を簡素化するため、LVDSチャネルSWAPおよびLVDS PIN順序の反転機能を搭載

- 64ピンの10mm×10mm HTQFP (PAP) PowerPAD™ ICパッケージで供給

SN65DSI83-Q1回路図

2 アプリケーション

- インフォテイメント用のディスプレイ内蔵ヘッド・ユニット

- インフォテイメント用のリモート・ディスプレイ付きヘッド・ユニット

- インフォテイメント用のリアシート・エンターテイメント

- ハイブリッド車載クラスタ

- 携帯用ナビゲーション・デバイス

- ナビゲーション

- 産業用ヒューマン・マシン・インターフェイス(HMI)およびディスプレイ

3 概要

SN65DSI83-Q1 DSI-to-LVDSブリッジは、シングル・チャネルのMIPI D-PHYレシーバ・フロントエンド構成で、チャネルごとに4つのレーンがあり、それぞれ1Gbpsで動作し、最大入力帯域幅は4Gbpsです。このブリッジはMIPI DSI 18bpp RGB666および24bpp RGB888パケットをデコードし、フォーマットされたビデオ・データストリームを、25MHz~154MHzのピクセル・クロックで動作するLVDS出力に変換して、リンクごとに4つのデータ・レーンを持つシングル・リンクLVDSを提供します。

SN65DSI83-Q1デバイスは、最高でWUXGA 1920×1200、毎秒60フレーム、24bppを、低ブランキングでサポートします。SN65DSI83-Q1デバイスは、毎秒60フレームの1366×768/1280×800、18bppおよび24bppのアプリケーションにも適しています。DSIとLVDSのインターフェイス間のデータ・ストリーム・ミスマッチに適応するため、部分的なライン・バッファが実装されています。

SN65DSI83-Q1デバイスは、小型の外形の10mm×10mm、0.5mmピッチのHTQFPパッケージに搭載され、-40℃~+105℃の温度範囲で動作します。

製品情報(1)

| 型番 | パッケージ | 本体サイズ(公称) |

|---|---|---|

| SN65DSI83-Q1 | HTQFP (64) | 10.00mm×10.00mm |

- 提供されているすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

4 改訂履歴

Changes from * Revision (December 2016) to A Revision

- Deleted figure RESET and Initialization Timing Definition While VCC is HighGo

- Changed the paragraph following Figure 8Go

- Changed Recommended Initialization Sequence To: Initialization SequenceGo

- Changed Table 2Go

- Changed item 3 in Video Stop and Restart Sequence From: Drive all DSI input lanes including DSI CLK lane to LP11. To: Drive all DSI data lanes to LP11, but keep the DSI CLK lanes in HS. Go

5 Pin Configuration and Functions

Pin Functions

| PIN | TYPE | DESCRIPTION | |

|---|---|---|---|

| NAME | NO. | ||

| ADDR | 64 | I/O | Local I2C interface target address select. See Table 3. In normal operation this pin is an input. When the ADDR pin is programmed high, it must be tied to the same 1.8-V power rails where the SN65DSI83-Q1 VCC 1.8-V power rail is connected |

| A_CLKP | 38 | O | LVDS channel A, LVDS clock output |

| A_CLKN | 39 | ||

| A_Y0P | 46 | O | LVDS channel A, LVDS data output 0 |

| A_Y0N | 47 | ||

| A_Y1P | 44 | O | LVDS channel A, LVDS data output 1 |

| A_Y1N | 45 | ||

| A_Y2P | 41 | O | LVDS channel A, LVDS data output 2 |

| A_Y2N | 42 | ||

| A_Y3P | 36 | O | LVDS channel A, LVDS data output 3. A_Y3P and A_Y3N must be left not connected (NC) for 18-bpp panels |

| A_Y3N | 37 | ||

| DA0P | 19 | I | MIPI D-PHY channel A, data lane 0; data rate up to 1 Gbps |

| DA0N | 20 | ||

| DA1P | 21 | I | MIPI D-PHY channel A, data lane 1; data rate up to 1 Gbps |

| DA1N | 22 | ||

| DA2P | 27 | I | MIPI D-PHY channel A, data lane 2; data rate up to 1 Gbps |

| DA2N | 28 | ||

| DA3P | 29 | I | MIPI D-PHY channel A, data lane 3; data rate up to 1 Gbps |

| DA3N | 30 | ||

| DACP | 24 | I | MIPI D-PHY channel A, clock lane; data rate up to 1 Gbps |

| DACN | 25 | ||

| EN | 2 | I | Chip enable and reset. The device is reset (shutdown) when the EN pin is low |

| GND | 23, 26, 52 | G | Reference ground |

| IRQ | 33 | O | Interrupt signal |

| REFCLK | 17 | I | This pin is an optional external reference clock for the LVDS pixel clock. If an external reference clock is not used, this pin must be pulled to ground with an external resistor. The source of the reference clock must be placed as close as possible with a series resistor near the source to reduce EMI |

| RSVD | 4 | RSVD | Reserved and leave them unconnected |

| 5 | |||

| 6 | |||

| 7 | |||

| 8 | |||

| 9 | |||

| 10 | |||

| 11 | |||

| 12 | |||

| 13 | |||

| 50 | |||

| 51 | |||

| 53 | |||

| 54 | |||

| 56 | |||

| 57 | |||

| 59 | |||

| 60 | |||

| 61 | |||

| 62 | |||

| RSVD1 | 34 | I/O | Reserved. This pin must be left unconnected for normal operation |

| RSVD2 | 1 | I | Reserved. This pin must be left unconnected for normal operation |

| SCL | 15 | I | Local I2C interface clock |

| SDA | 16 | I/O | Local I2C interface data |

| VCC | 3 | — | 1.8-V power supply |

| 14 | |||

| 18 | |||

| 32 | |||

| 35 | |||

| 40 | |||

| 43 | |||

| 48 | |||

| 49 | |||

| 55 | |||

| 58 | |||

| 63 | |||

| VCORE | 31 | P | 1.1-V output from the voltage regulator. This pin must have a 1-µF external capacitor to ground |

| PowerPAD | — | — | Reference ground |

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)| MIN | MAX | UNIT | |||

|---|---|---|---|---|---|

| VCC | Supply voltage | –0.3 | 2.175 | V | |

| Input voltage | CMOS input pins | –0.5 | 2.175 | V | |

| DSI input pins (DAxP, DAxN) | –0.4 | 1.4 | V | ||

| TA | Operating free-air temperature | –40 | 105 | °C | |

| TJ | Junction temperature | –40 | 115 | °C | |

| Tstg | Storage temperature | –65 | 150 | °C | |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

6.2 ESD Ratings

| VALUE | UNIT | ||||

|---|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002(1) | ±4000 | V | |

| Charged-device model (CDM), per AEC Q100-011 | ±1000 | ||||

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| VCC | VCC power supply | 1.65 | 1.8 | 1.95 | V |

| VPSN | Supply noise on any VCC pin | ƒ(noise) > 1 MHz | 0.05 | V | |

| V(DSI) | DSI input pin voltage | –50 | 1350 | mV | |

| ƒ(I2C) | Local I2C input frequency | 400 | kHz | ||

| ƒHS(CLK) | DSI high-speed (HS) clock input frequency | 40 | 500 | MHz | |

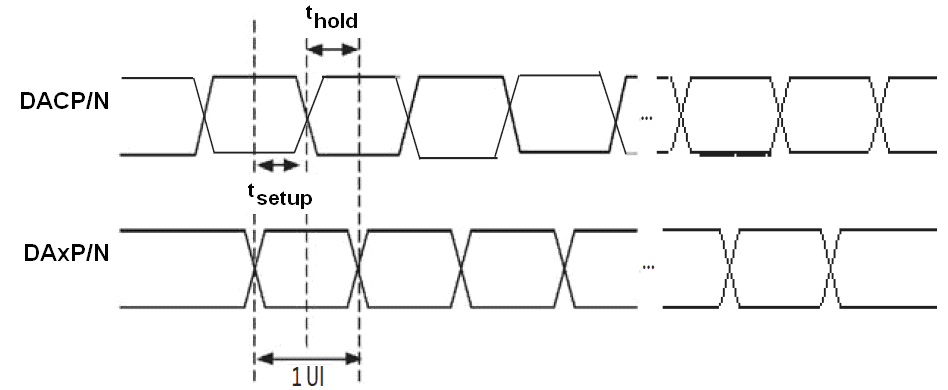

| tsu | DSI HS data to clock setup time; see Figure 1 | 0.15 | UI(1) | ||

| th | DSI HS data to clock hold time; see Figure 1 | 0.15 | UI(1) | ||

| ZOD(LVDS) | LVDS output differential impedance | 90 | 132 | Ω | |

| TC | Case temperature | 92.2 | °C | ||

(1) The unit interval (UI) is one half of the period of the HS clock; at 500 MHz the minimum setup and hold time is 150 ps.

6.4 Thermal Information

| THERMAL METRIC(1) | SN65DSI83-Q1 | UNIT | |

|---|---|---|---|

| PAP (HTQFP) | |||

| 64 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 36.1 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 18.2 | °C/W |

| RθJB | Junction-to-board thermal resistance | 20.6 | °C/W |

| ψJT | Junction-to-top characterization parameter | 0.8 | °C/W |

| ψJB | Junction-to-board characterization parameter | 20.5 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | 2.2 | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

6.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP(1) | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VIL | Low-level control signal input voltage | 0.3 × VCC | V | |||

| VIH | High-level control signal input voltage | 0.7 × VCC | V | |||

| VOH | High-level output voltage | IOH = –4 mA | 1.25 | V | ||

| VOL | Low-level output voltage | IOL = 4 mA | 0.4 | V | ||

| ILKG | Input failsafe leakage current | VCC = 0; VCC(PIN) = 1.8 V | ±30 | μA | ||

| IIH | High level input current | Any input terminal | ±30 | μA | ||

| IIL | Low level input current | Any input terminal | ±30 | μA | ||

| IOZ | High-impedance output current | CMOS output terminals | ±10 | μA | ||

| IOS | Short-circuit output current | Any output driving GND short | ±50 | mA | ||

| ICC | Device active current | See (2) | 77 | 124 | mA | |

| IULPS | Device standby current | All data and clock lanes are in ultra-low power state (ULPS) | 7.7 | 14 | mA | |

| IRST | Shutdown current | EN = 0 | 130 | µA | ||

| REN | EN control input resistor | 200 | kΩ | |||

| MIPI DSI INTERFACE | ||||||

| VIH-LP | LP receiver input high threshold | See Figure 2 | 880 | mV | ||

| VIL-LP | LP receiver input low threshold | See Figure 2 | 550 | mV | ||

| |VID| | HS differential input voltage | 100 | 270 | mV | ||

| |VIDT| | HS differential input voltage threshold | 50 | mV | |||

| VIL-ULPS | LP receiver input low threshold; ultra-low power state (ULPS) | 300 | mV | |||

| VCM-HS | HS common mode voltage; steady-state | 70 | 330 | mV | ||

| ΔVCM-HS | HS common mode peak-to-peak variation including symbol delta and interference | 100 | mV | |||

| VIH-HS | HS single-ended input high voltage | See Figure 2 | 460 | mV | ||

| VIL-HS | HS single-ended input low voltage | See Figure 2 | –40 | mV | ||

| VTERM-EN | HS termination enable; single-ended input voltage (both Dp AND Dn apply to enable) | Termination is switched simultaneous for Dn and Dp | 450 | mV | ||

| RDIFF-HS | HS mode differential input impedance | 80 | 125 | Ω | ||

| LVDS OUTPUT | ||||||

| |VOD| | Steady-state differential output voltage

A_Y x P/N |

CSR 0×19.3:2=00

100 Ω near end termination |

180 | 245 | 330 | mV |

| CSR 0×19.3:2=01

100 Ω near end termination |

215 | 293 | 392 | |||

| CSR 0×19.3:2=10

100 Ω near end termination |

250 | 341 | 455 | |||

| CSR 0×19.3:2=11

100 Ω near end termination |

290 | 389 | 515 | |||

| CSR 0×19.3:2=00

200 Ω near end termination |

150 | 204 | 275 | |||

| CSR 0×19.3:2=01

200 Ω near end termination |

200 | 271 | 365 | |||

| CSR 0×19.3:2=10

200 Ω near end termination |

250 | 337 | 450 | |||

| CSR 0×19.3:2=11

200 Ω near end termination |

300 | 402 | 535 | |||

| |VOD| | Steady-state differential output voltage for

A_CLKP/N |

CSR 0×19.3:2=00

near end termination |

140 | 191 | 262 | mV |

| CSR 0×19.3:2=01

100 Ω near end termination |

168 | 229 | 315 | |||

| CSR 0×19.3:2=10

100 Ω near end termination |

195 | 266 | 365 | |||

| CSR 0×19.3:2=11

100 Ω near end termination |

226 | 303 | 415 | |||

| CSR 0×19.3:2=00

200 Ω near end termination |

117 | 159 | 220 | |||

| CSR 0×19.3:2=01

200 Ω near end termination |

156 | 211 | 295 | |||

| CSR 0×19.3:2=10

200 Ω near end termination |

195 | 263 | 362 | |||

| CSR 0×19.3:2=11

200 Ω near end termination |

234 | 314 | 435 | |||

| Δ|VOD| | Change in steady-state differential output voltage between opposite binary states | RL = 100 Ω | 35 | mV | ||

| VOC(SS) | Steady state common-mode output voltage(3) | CSR 0×19.6 = 1 and CSR 0×1B.6 = 1 Figure 3 | 0.75 | 0.9 | 1.13 | V |

| CSR 0×19.6 = 0 see Figure 3 | 1 | 1.25 | 1.5 | |||

| VOC(PP) | Peak-to-peak common-mode output voltage | see Figure 3 | 35 | mV | ||

| RLVDS_DIS | Pulldown resistance for disabled LVDS outputs | 1 | kΩ | |||

(1) All typical values are at VCC = 1.8 V and TA = 25°C

(2) SN65DSI83-Q1: SINGLE Channel DSI to SINGLE Channel DSI, 1280 × 800

- Number of LVDS lanes = 3 data lanes + 1 CLK lane

- Number of DSI lanes = 4 data lanes + 1 CLK lane

- LVDS CLK OUT = 83 M

- DSI CLK = 500 M

- RGB888, LVDS 18 bpp

(3) Tested at VCC = 1.8V , TA = –40°C for MIN, TA = 25°C for TYP, TA = 105°C for MAX.

6.6 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP(1) | MAX | UNIT | |

|---|---|---|---|---|---|---|

| DSI | ||||||

| tGS | DSI LP glitch suppression pulse width | 300 | ps | |||

| LVDS | ||||||

| tc | Output clock period | 6.49 | 40 | ns | ||

| tw | High-level output clock (CLK) pulse duration | 4/7 tc | ns | |||

| t0 | Delay time, CLK↑ to 1st serial bit position | tc = 6.49 ns;

Input clock jitter < 25 ps (REFCLK) See Figure 4 |

–0.15 | 0.15 | ns | |

| t1 | Delay time, CLK↑ to 2nd serial bit position | 1/7 tc – 0.15 | 1/7 tc + 0.15 | ns | ||

| t2 | Delay time, CLK↑ to 3rd serial bit position | 2/7 tc – 0.15 | 2/7 tc + 0.15 | ns | ||

| t3 | Delay time, CLK↑ to 4th serial bit position | 3/7 tc – 0.15 | 3/7 tc + 0.15 | ns | ||

| t4 | Delay time, CLK↑ to 5th serial bit position | 4/7 tc – 0.15 | 4/7 tc + 0.15 | ns | ||

| t5 | Delay time, CLK↑ to 6th serial bit position | 5/7 tc – 0.15 | 5/7 tc + 0.15 | ns | ||

| t6 | Delay time, CLK↑ to 7th serial bit position | 6/7 tc – 0.15 | 6/7 tc + 0.15 | ns | ||

| tr | Differential output rise time | See Figure 4 | 180 | 500 | ps | |

| tf | Differential output fall time | |||||

| EN, ULPS, RESET | ||||||

| ten | Enable time from EN or ULPS | tc(o) = 12.9 ns | 1 | ms | ||

| tdis | Disable time to standby; see | tc(o) = 12.9 ns | 0.1 | ms | ||

| treset | Reset yime | 10 | ms | |||

| REFCLK | ||||||

| FREFCLK | REFCLK freqeuncy. Supported frequencies:

25 MHz - 154 MHz |

25 | 154 | MHz | ||

| tr, tf | REFCLK rise and fall time | 100 × 10–12 | 1×10–9 | s | ||

| tpj | REFCLK peak-to-peak phase jitter | 50 | ps | |||

| Duty | REFCLK duty cycle | 40% | 50% | 60% | ||

| REFCLK or DSI CLK (DACP/N) | ||||||

| SSC_CLKIN | SSC enabled Input CLK center spread depth(2) | 0.5% | 1% | 2% | ||

| Modulation frequency | 30 | 60 | kHz | |||

(1) All typical values are at VCC = 1.8 V and TA = 25°C

(2) For EMI reduction purpose, the SN65DSI83-Q1 supports the center spreading of the LVDS CLK output through the REFCLK or DSI CLK input. The center spread CLK input to the REFCLK or DSI CLK is passed through to the LVDS CLK output A_CLKP/N.

7 Parameter Measurement Information

Figure 1. DSI HS Mode Receiver Timing Definitions

Figure 1. DSI HS Mode Receiver Timing Definitions  Figure 2. DSI Receiver Voltage Definitions

Figure 2. DSI Receiver Voltage Definitions  Figure 3. Test Load and Voltage Definitions for LVDS Outputs

Figure 3. Test Load and Voltage Definitions for LVDS Outputs  Figure 4. SN65DSI83-Q1 LVDS Timing Definitions

Figure 4. SN65DSI83-Q1 LVDS Timing Definitions

1. See the ULPS section of the data sheet for the ULPS entry and exit sequence.

2. ULPS entry and exit protocol and timing requirements must be met according to the MIPI DPHY specification.

Figure 5. ULPS Timing Definition