-

ADS122C04 24ビット、4チャネル、2kSPS、I2Cインターフェイス搭載のデルタ-シグマADC

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 概要(続き)

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3

Feature Description

- 9.3.1 Multiplexer

- 9.3.2 Low-Noise Programmable Gain Stage

- 9.3.3 Voltage Reference

- 9.3.4 Modulator and Internal Oscillator

- 9.3.5 Digital Filter

- 9.3.6 Conversion Times

- 9.3.7 Excitation Current Sources

- 9.3.8 Sensor Detection

- 9.3.9 System Monitor

- 9.3.10 Temperature Sensor

- 9.3.11 Offset Calibration

- 9.3.12 Conversion Data Counter

- 9.3.13 Data Integrity Features

- 9.4 Device Functional Modes

- 9.5 Programming

- 9.6

Register Map

- 9.6.1 Configuration Registers

- 9.6.2 Register Descriptions

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13デバイスおよびドキュメントのサポート

- 14メカニカル、パッケージ、および注文情報

- 重要なお知らせ

ADS122C04 24ビット、4チャネル、2kSPS、I2Cインターフェイス搭載のデルタ-シグマADC

1 特長

- 315µA (標準値)の低消費電流

- 広い電源電圧範囲:2.3V~5.5V

- プログラマブル・ゲイン:1~128

- プログラマブル・データ・レート:最大2kSPS

- 最大20ビットの有効分解能

- シングル・サイクル安定化デジタル・フィルタによる50Hzおよび60Hzの同時リジェクション(20SPS)

- 2つの差動入力または4つのシングルエンド入力

- デュアル・マッチのプログラム可能電流源:

10µA~1.5mA - 内部リファレンス:2.048V、ドリフト(標準値):5ppm/℃

- 内部オシレータ:精度2%

- 内部温度センサ:精度0.5℃(標準値)

- I2C互換インターフェイス

- サポートされるI2Cバス速度モード:

Standard-Mode、Fast-Mode、Fast-Mode Plus - 16のI2Cアドレスをピンで設定可能

- パッケージ:3.0mm × 3.0mm × 0.75mm WQFN

2 アプリケーション

- フィールド・トランスミッタ:

温度、圧力、張力、フロー - PLCおよびDCSアナログ入力モジュール

- 温度コントローラ

- 熱メータ

- 患者モニタリング・システム:体温、血圧

3 概要

ADS122C04は、高精度の24ビット、アナログ/デジタル・コンバータ(ADC)で、小信号を測定するセンサ・アプリケーションのシステム・コストと部品点数を削減する多数の機能を統合しています。このデバイスは、柔軟な入力マルチプレクサ(MUX)を介した2つの差動入力または4つのシングルエンド入力、低ノイズのプログラマブル・ゲイン・アンプ(PGA)、2つのプログラマブル励起電流源、基準電圧、オシレータ、高精度温度センサを備えています。

このデバイスはシングル・サイクル安定化により、最大2000サンプル/秒(SPS)のデータ・レートで変換を実行します。デジタル・フィルタはノイズの大きい工業用アプリケーションに対して、20SPSで50Hzおよび60Hzの同時リジェクションを提供します。内部PGAは最大128のゲインを提供します。このPGAを備えたADS122C04は、測温抵抗体(RTD)、熱電対、サーミスタ、抵抗性ブリッジ・センサなどの小信号を測定するセンサ・アプリケーションに最適です。

製品情報(1)

| 型番 | パッケージ | 本体サイズ(公称) |

|---|---|---|

| ADS122C04 | WQFN (16) | 3.00mm×3.00mm |

| TSSOP (16) | 5.00mm×4.40mm |

- 提供されているすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

Device Images

Kタイプ熱電対温度の測定

4 改訂履歴

Changes from A Revision (March 2018) to B Revision

- Changed Internal Voltage Reference, Accuracy parameter: added TSSOP package to test conditions of first row and added second row for the WQFN package Go

- Added TSSOP package to conditions of Internal Reference Voltage Histogram figureGo

- Changed Digital Supply Current vs Temperature figureGo

- Deleted last sentence from first paragraph of Pseudo Code Example sectionGo

- Changed (MUX[3:1] = 1110) to (MUX[3:0] = 1110) in Pseudo Code Example section Go

Changes from * Revision (October 2017) to A Revision

- 量産用にリリースGo

5 概要(続き)

ADS122C04には2線式のI2C互換インターフェイスが搭載され、最高1MbpsのI2Cバス速度に対応します。2本のアドレス・ピンにより、16の異なるデバイスI2Cアドレスを選択できます。

ADS122C04は、16ピンのリードレスWQFNパッケージ、または16ピンTSSOPパッケージで提供されており、温度範囲-40℃~+125℃で動作が規定されています。

6 Pin Configuration and Functions

Pin Functions

| PIN | ANALOG OR DIGITAL

INPUT/OUTPUT |

DESCRIPTION(1) | ||

|---|---|---|---|---|

| NAME | NO. | |||

| RTE | PW | |||

| A0 | 15 | 1 | Digital input | I2C slave address select pin 0. See the I2C Address section for details. |

| A1 | 16 | 2 | Digital input | I2C slave address select pin 1. See the I2C Address section for details. |

| AIN0 | 9 | 11 | Analog input | Analog input 0 |

| AIN1 | 8 | 10 | Analog input | Analog input 1 |

| AIN2 | 5 | 7 | Analog input | Analog input 2 |

| AIN3 | 4 | 6 | Analog input | Analog input 3 |

| AVDD | 10 | 12 | Analog supply | Positive analog power supply. Connect a 100-nF (or larger) capacitor to AVSS. |

| AVSS | 3 | 5 | Analog supply | Negative analog power supply |

| DGND | 2 | 4 | Digital supply | Digital ground |

| DRDY | 12 | 14 | Digital output | Data ready, active low. Connect to DVDD using a pullup resistor. |

| DVDD | 11 | 13 | Digital supply | Positive digital power supply. Connect a 100-nF (or larger) capacitor to DGND. |

| REFN | 6 | 8 | Analog input | Negative reference input |

| REFP | 7 | 9 | Analog input | Positive reference input |

| RESET | 1 | 3 | Digital input | Reset, active low |

| SCL | 14 | 16 | Digital input | Serial clock input. Connect to DVDD using a pullup resistor. |

| SDA | 13 | 15 | Digital input/output | Serial data input and output. Connect to DVDD using a pullup resistor. |

| Thermal pad | Pad | — | — | Thermal power pad. Connect to AVSS. |

7 Specifications

7.1 Absolute Maximum Ratings(1)

| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| Power-supply voltage | AVDD to AVSS | –0.3 | 7 | V |

| DVDD to DGND | –0.3 | 7 | ||

| AVSS to DGND | –2.8 | 0.3 | ||

| Analog input voltage | AIN0, AIN1, AIN2, AIN3, REFP, REFN | AVSS – 0.3 | AVDD + 0.3 | V |

| Digital input voltage | SCL, SDA, A0, A1, DRDY, RESET | DGND – 0.3 | 7 | V |

| Input current | Continuous, any pin except power-supply pins | –10 | 10 | mA |

| Temperature | Junction, TJ | 150 | °C | |

| Storage, Tstg | –60 | 150 | ||

7.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±2000 | V |

| Charged-device model (CDM), per JEDEC specification JESD22-C101(2) | ±750 | |||

7.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)| MIN | NOM | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| POWER SUPPLY | ||||||

| Unipolar analog power supply | AVDD to AVSS | 2.3 | 5.5 | V | ||

| AVSS to DGND | –0.1 | 0 | 0.1 | |||

| Bipolar analog power supply | AVDD to DGND | 2.3 | 2.5 | 2.75 | V | |

| AVSS to DGND | –2.75 | –2.5 | –2.3 | |||

| Digital power supply | DVDD to DGND | 2.3 | 5.5 | V | ||

| ANALOG INPUTS(1) | ||||||

| V(AINx) | Absolute input voltage(2) | PGA disabled, gain = 1 to 4 | AVSS – 0.1 | AVDD + 0.1 | V | |

| PGA enabled, gain = 1 to 4 | AVSS + 0.2 | AVDD – 0.2 | ||||

| PGA enabled, gain = 8 to 128 | AVSS + 0.2 +

|VINMAX|·(Gain – 4) / 8 |

AVDD – 0.2 –

|VINMAX|·(Gain – 4) / 8 |

||||

| VIN | Differential input voltage | VIN = VAINP – VAINN(3) | –VREF / Gain | VREF / Gain | V | |

| VOLTAGE REFERENCE INPUTS | ||||||

| VREF | Differential reference input voltage | VREF = V(REFP) – V(REFN) | 0.75 | 2.5 | AVDD – AVSS | V |

| V(REFN) | Absolute negative reference voltage | AVSS – 0.1 | V(REFP) – 0.75 | V | ||

| V(REFP) | Absolute positive reference voltage | V(REFN) + 0.75 | AVDD + 0.1 | V | ||

| DIGITAL INPUTS | ||||||

| Input voltage | SCL, SDA, A0, A1, DRDY,

2.3 V ≤ DVDD < 3.0 V |

DGND | DVDD + 0.5 | V | ||

| SCL, SDA, A0, A1, DRDY,

3.0 V ≤ DVDD ≤ 5.5 V |

DGND | 5.5 | ||||

| RESET | DGND | DVDD | ||||

| TEMPERATURE RANGE | ||||||

| TA | Operating ambient temperature | –40 | 125 | °C | ||

PGA disabled means the low-noise PGA is powered down and bypassed. Gains of 1, 2, and 4 are still possible in this case.

See the Low-Noise Programmable Gain Stage section for more information.

7.4 Thermal Information

| THERMAL METRIC(1) | ADS122C04 | UNIT | ||

|---|---|---|---|---|

| WQFN (RTE) | TSSOP (PW) | |||

| 16 PINS | 16 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 57.7 | 90.3 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 29.0 | 31.7 | °C/W |

| RθJB | Junction-to-board thermal resistance | 19.9 | 41.8 | °C/W |

| ψJT | Junction-to-top characterization parameter | 0.3 | 1.8 | °C/W |

| ψJB | Junction-to-board characterization parameter | 19.8 | 41.2 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | 11.8 | N/A | °C/W |

7.5 Electrical Characteristics

minimum and maximum specifications apply from TA = –40°C to +125°C; typical specifications are at TA = 25°C; all specifications are at AVDD = 2.3 V to 5.5 V, AVSS = 0 V, DVDD = 3.3 V, PGA enabled, all data rates, and internal reference enabled (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| ANALOG INPUTS | ||||||

| Absolute input current | PGA disabled, gain = 1 to 4, normal mode, VIN = 0 V | ±5 | nA | |||

| PGA disabled, gain = 1 to 4, turbo mode, VIN = 0 V | ±10 | |||||

| Gain = 1 to 128, VIN = 0 V | ±1 | |||||

| Absolute input current drift | PGA disabled, gain = 1 to 4, VIN = 0 V | 10 | pA/°C | |||

| Gain = 1 to 128, VIN = 0 V | 5 | |||||

| Differential input current | PGA disabled, gain = 1 to 4, normal mode,

VCM = AVDD / 2, –VREF / Gain ≤ VIN ≤ VREF / Gain |

±5 | nA | |||

| PGA disabled, gain = 1 to 4, turbo mode,

VCM = AVDD / 2, –VREF / Gain ≤ VIN ≤ VREF / Gain |

±10 | |||||

| Gain = 1 to 128,

VCM = AVDD / 2, –VREF / Gain ≤ VIN ≤ VREF / Gain |

±1 | |||||

| Differential input current drift | PGA disabled, gain = 1 to 4,

VCM = AVDD / 2, –VREF / Gain ≤ VIN ≤ VREF / Gain |

10 | pA/°C | |||

| Gain = 1 to 128,

VCM = AVDD / 2, –VREF / Gain ≤ VIN ≤ VREF / Gain |

2 | |||||

| SYSTEM PERFORMANCE | ||||||

| Resolution (no missing codes) | 24 | Bits | ||||

| DR | Data rate | Normal mode | 20, 45, 90, 175, 330, 600, 1000 | SPS | ||

| Turbo mode | 40, 90, 180, 350, 660, 1200, 2000 | |||||

| Noise (input-referred)(1) | Normal mode, gain = 128, DR = 20 SPS | 110 | nVRMS | |||

| INL | Integral nonlinearity | AVDD = 3.3 V, gain = 1 to 128, VCM = AVDD / 2, external VREF, normal mode, best fit | –15 | ±6 | 15 | ppmFSR |

| VIO | Input offset voltage | PGA disabled, gain = 1 to 4, differential inputs | ±4 | µV | ||

| Gain = 1, differential inputs, TA = 25°C | –150 | ±5 | 150 | |||

| Gain = 2 to 128, differential inputs | ±4 | |||||

| Offset drift vs temperature | PGA disabled, gain = 1 to 4 | 0.02 | µV/°C | |||

| Gain = 1 to 128 | 0.1 | 0.6 | ||||

| Gain error(2) | PGA disabled, gain = 1 to 4 | ±0.01% | ||||

| Gain = 1 to 32, TA = 25°C | –0.05% | ±0.01% | 0.05% | |||

| Gain = 64 to 128, TA = 25°C | –0.1% | ±0.015% | 0.1% | |||

| Gain drift vs temperature(2) | PGA disabled, gain = 1 to 4 | 0.5 | ppm/°C | |||

| Gain = 1 to 32 | 0.5 | 2 | ||||

| Gain = 64 to 128 | 1 | 4 | ||||

| SYSTEM PERFORMANCE (continued) | ||||||

| NMRR | Normal-mode rejection ratio | 50 Hz ±1 Hz, DR = 20 SPS | 78 | 88 | dB | |

| 60 Hz ±1 Hz, DR = 20 SPS | 80 | 88 | ||||

| CMRR | Common-mode rejection ratio | At dc, gain = 1, AVDD = 3.3 V | 90 | 105 | dB | |

| fCM = 50 Hz or 60 Hz, DR = 20 SPS, AVDD = 3.3 V | 105 | 115 | ||||

| fCM = 50 Hz or 60 Hz, DR = 2 kSPS, AVDD = 3.3 V | 95 | 110 | ||||

| PSRR | Power-supply rejection ratio | AVDD at dc, VCM = AVDD / 2 | 85 | 105 | dB | |

| DVDD at dc, VCM = AVDD / 2 | 95 | 115 | ||||

| INTERNAL VOLTAGE REFERENCE | ||||||

| VREF | Reference voltage | 2.048 | V | |||

| Accuracy | TA = 25°C, TSSOP package | –0.15% | ±0.01% | 0.15% | ||

| TA = 25°C, WQFN package | –0.25% | ±0.04% | 0.25% | |||

| Temperature drift | 5 | 30 | ppm/°C | |||

| Long-term drift | 1000 hours | 110 | ppm | |||

| VOLTAGE REFERENCE INPUTS | ||||||

| Reference input current | REFP = VREF, REFN = AVSS, AVDD = 3.3 V | ±10 | nA | |||

| INTERNAL OSCILLATOR | ||||||

| fCLK | Frequency | Normal mode | 1.024 | MHz | ||

| Turbo mode | 2.048 | |||||

| Accuracy | Normal mode | –2% | ±1% | 2% | ||

| Turbo mode | –4% | ±2% | 4% | |||

| EXCITATION CURRENT SOURCES (IDACs) (AVDD = 3.3 V to 5.5 V) | ||||||

| Current settings | 10, 50, 100, 250, 500, 1000, 1500 | µA | ||||

| Compliance voltage | All IDAC settings | AVDD – 0.9 | V | |||

| Accuracy (each IDAC) | IDAC = 50 µA to 1.5 mA | –6% | ±1% | 6% | ||

| Current matching between IDACs | IDAC = 50 µA to 1.5 mA, TA = 25°C | 0.3% | 2% | |||

| Temperature drift (each IDAC) | IDAC = 50 µA to 1.5 mA | 50 | ppm/°C | |||

| Temperature drift matching between IDACs | IDAC = 50 µA to 1.5 mA | 8 | 40 | ppm/°C | ||

| BURN-OUT CURRENT SOURCES (BOCS) | ||||||

| Magnitude | Sink and source | 10 | µA | |||

| Accuracy | ±5% | |||||

| TEMPERATURE SENSOR | ||||||

| Conversion resolution | 14 | Bits | ||||

| Temperature resolution | 0.03125 | °C | ||||

| Accuracy | TA = 0°C to +85°C | –1 | ±0.25 | 1 | °C | |

| TA = –40°C to +125°C | –1.5 | ±0.5 | 1.5 | |||

| Accuracy vs analog supply voltage | 0.0625 | 0.25 | °C/V | |||

| DIGITAL INPUTS/OUTPUTS | ||||||

| VIL | Logic input level, low | DGND | 0.3 DVDD | V | ||

| VIH | Logic input level, high | 2.3 V ≤ DVDD < 3.0 V,

SCL, SDA, A0, A1, DRDY |

0.7 DVDD | DVDD + 0.5 | V | |

| 3.0 V ≤ DVDD ≤ 5.5 V,

SCL, SDA, A0, A1, DRDY |

0.7 DVDD | 5.5 | ||||

| RESET | 0.7 DVDD | DVDD | ||||

| Vhys | Hysteresis of Schmitt-trigger inputs | Fast-mode, fast-mode plus | 0.05 DVDD | V | ||

| VOL | Logic output level, low | IOL = 3 mA | DGND | 0.15 | 0.4 | V |

| IOL | Low-level output current | VOL = 0.4 V, standard-mode, fast-mode | 3 | mA | ||

| VOL = 0.4 V, fast-mode plus | 20 | |||||

| VOL = 0.6 V, fast-mode | 6 | |||||

| Ii | Input current | DGND + 0.1 V < VDigital Input < DVDD – 0.1 V | –10 | 10 | µA | |

| Ci | Capacitance | Each pin | 10 | pF | ||

| ANALOG SUPPLY CURRENT (AVDD = 3.3 V, VIN = 0 V, IDACs Turned Off) | ||||||

| IAVDD | Analog supply current | Power-down mode | 0.1 | 3 | µA | |

| Normal mode, PGA disabled, gain = 1 to 4 | 250 | |||||

| Normal mode, gain = 1 to 16 | 360 | 510 | ||||

| Normal mode, gain = 32 | 455 | |||||

| Normal mode, gain = 64, 128 | 550 | |||||

| Turbo mode, PGA disabled, gain = 1 to 4 | 370 | |||||

| Turbo mode, gain = 1 to 16 | 580 | |||||

| Turbo mode, gain = 32 | 765 | |||||

| Turbo mode, gain = 64, 128 | 955 | |||||

| ADDITIONAL ANALOG SUPPLY CURRENTS PER FUNCTION (AVDD = 3.3 V) | ||||||

| IAVDD | Analog supply current | External reference selected | 60 | µA | ||

| IDAC overhead (excludes the actual IDAC current) | 195 | |||||

| DIGITAL SUPPLY CURRENT (DVDD = 3.3 V, All Data Rates, I2C Not Active) | ||||||

| IDVDD | Digital supply current | Power-down mode | 0.3 | 5 | µA | |

| Normal mode | 65 | 100 | ||||

| Turbo mode | 100 | |||||

| POWER DISSIPATION (AVDD = DVDD = 3.3 V, All Data Rates, VIN = 0 V, I2C Not Active) | ||||||

| PD | Power dissipation | Normal mode, gain = 1 to 16 | 1.4 | mW | ||

| Turbo mode, gain = 1 to 16 | 2.2 | |||||

7.6 I2C Timing Requirements

over operating ambient temperature range and DVDD = 2.3 V to 5.5 V, bus capacitance = 10 pF to 400 pF, and pullup resistor = 1 kΩ (unless otherwise noted)| MIN | MAX | UNIT | |||

|---|---|---|---|---|---|

| STANDARD-MODE | |||||

| fSCL | SCL clock frequency | 0 | 100 | kHz | |

| tHD;STA | Hold time, (repeated) START condition.

After this period, the first clock pulse is generated. |

4 | µs | ||

| tLOW | Pulse duration, SCL low | 4.7 | µs | ||

| tHIGH | Pulse duration, SCL high | 4.0 | µs | ||

| tSU;STA | Setup time, repeated START condition | 4.7 | µs | ||

| tHD;DAT | Hold time, data | 0 | µs | ||

| tSU;DAT | Setup time, data | 250 | ns | ||

| tr | Rise time, SCL, SDA | 1000 | ns | ||

| tf | Fall time, SCL, SDA | 250 | ns | ||

| tSU;STO | Setup time, STOP condition | 4.0 | µs | ||

| tBUF | Bus free time, between STOP and START condition | 4.7 | µs | ||

| tVD;DAT | Valid time, data | 3.45 | µs | ||

| tVD;ACK | Valid time, acknowledge | 3.45 | µs | ||

| FAST-MODE | |||||

| fSCL | SCL clock frequency | 0 | 400 | kHz | |

| tHD;STA | Hold time, (repeated) START condition.

After this period, the first clock pulse is generated. |

0.6 | µs | ||

| tLOW | Pulse duration, SCL low | 1.3 | µs | ||

| tHIGH | Pulse duration, SCL high | 0.6 | µs | ||

| tSU;STA | Setup time, repeated START condition | 0.6 | µs | ||

| tHD;DAT | Hold time, data | 0 | µs | ||

| tSU;DAT | Setup time, data | 100 | ns | ||

| tr | Rise time, SCL, SDA | 20 | 300 | ns | |

| tf | Fall time, SCL, SDA | 20 · (DVDD / 5.5 V) | 250 | ns | |

| tSU;STO | Setup time, STOP condition | 0.6 | µs | ||

| tBUF | Bus free time, between STOP and START condition | 1.3 | µs | ||

| tVD;DAT | Valid time, data | 0.9 | µs | ||

| tVD;ACK | Valid time, acknowledge | 0.9 | µs | ||

| tSP | Pulse width of spikes that must be suppressed by the input filter | 0 | 50 | ns | |

| FAST-MODE PLUS | |||||

| fSCL | SCL clock frequency | 0 | 1000 | kHz | |

| tHD;STA | Hold time, (repeated) START condition.

After this period, the first clock pulse is generated. |

0.26 | µs | ||

| tLOW | Pulse duration, SCL low | 0.5 | µs | ||

| tHIGH | Pulse duration, SCL high | 0.26 | µs | ||

| tSU;STA | Setup time, repeated START condition | 0.26 | µs | ||

| tHD;DAT | Hold time, data | 0 | µs | ||

| tSU;DAT | Setup time, data | 50 | ns | ||

| tr | Rise time, SCL, SDA | 120 | ns | ||

| tf | Fall time, SCL, SDA | Pullup resistor = 350 Ω | 20 · (DVDD / 5.5 V) | 120 | ns |

| tSU;STO | Setup time, STOP condition | 0.26 | µs | ||

| tBUF | Bus free time, between STOP and START condition | 0.5 | µs | ||

| tVD;DAT | Valid time, data | 0.45 | µs | ||

| tVD;ACK | Valid time, acknowledge | 0.45 | µs | ||

| tSP | Pulse duration of spikes that must be suppressed by the input filter | 0 | 50 | ns | |

| RESET PIN | |||||

| tw(RSL) | Pulse duration, RESET low | 250 | ns | ||

| td(RSSTA) | Delay time, START condition after RESET rising edge(2) | 100 | ns | ||

| DRDY PIN | |||||

| td(DRSTA) | Delay time, START condition after DRDY falling edge | 0 | ns | ||

| TIMEOUT | |||||

| Timeout(1) | Normal mode | 14000 | tMOD | ||

| Turbo mode | 28000 | ||||

tMOD = 1 / fMOD. Modulator frequency fMOD = 256 kHz (normal mode) and 512 kHz (turbo mode).

7.7 I2C Switching Characteristics

over operating ambient temperature range, DVDD = 2.3 V to 5.5 V, bus capacitance = 10 pF to 400 pF, and pullup resistor = 1 kΩ (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| tw(DRH) | Pulse duration, DRDY high(1) | 2 | tMOD | |||

| tp(RDDR) | Propagation delay time, RDATA command latched to DRDY rising edge | 2 | tMOD | |||

Figure 1. I2C Timing Requirements

Figure 1. I2C Timing Requirements  Figure 2. RESET Pin Timing Requirements

Figure 2. RESET Pin Timing Requirements  Figure 3. DRDY Pin Timing Requirements and Switching Characteristics

Figure 3. DRDY Pin Timing Requirements and Switching Characteristics 7.8 Typical Characteristics

at TA = 25°C, AVDD = 3.3 V, and AVSS = 0 V using internal VREF = 2.048 V (unless otherwise noted)

| Normal mode, PGA disabled, VIN = 0 V |

| Turbo mode, PGA disabled, VIN = 0 V |

| Normal mode, PGA disabled, VCM = 1.65 V |

Differential Input Voltage

| Turbo mode, PGA disabled, VCM = 1.65 V |

Differential Input Voltage

| PGA enabled, external reference, best fit |

| PGA enabled, gain = 1, 620 samples |

| PGA enabled | ||

| PGA enabled, gain = 1, 620 samples |

| PGA disabled |

| PGA disabled |

| Normal mode |

| Normal mode |

| Power-down mode |

| Normal mode |

| Normal mode, PGA enabled, VIN = 0 V |

| Turbo mode, PGA enabled, VIN = 0 V |

| Normal mode, PGA enabled, VCM = 1.65 V |

Differential Input Voltage

| Turbo mode, PGA enabled, VCM = 1.65 V |

Differential Input Voltage

| PGA enabled, internal reference, best fit |

| PGA disabled |

| PGA disabled, gain = 1, 620 samples |

| PGA enabled, gain = 128, 620 samples |

| PGA enabled |

| PGA enabled |

| Normal mode | ||

| DVDD = 3.3 V |

| Normal mode |

| Power-down mode |

| Normal mode |

8 Parameter Measurement Information

8.1 Noise Performance

Delta-sigma (ΔΣ) analog-to-digital converters (ADCs) are based on the principle of oversampling. The input signal of a ΔΣ ADC is sampled at a high frequency (modulator frequency) and subsequently filtered and decimated in the digital domain to yield a conversion result at the respective output data rate. The ratio between modulator frequency and output data rate is called oversampling ratio (OSR). By increasing the OSR, and thus reducing the output data rate, the noise performance of the ADC can be optimized. In other words, the input-referred noise drops when reducing the output data rate because more samples of the internal modulator are averaged to yield one conversion result. Increasing the gain also reduces the input-referred noise, which is particularly useful when measuring low-level signals.

Table 1 to Table 8 summarize the device noise performance. Data are representative of typical noise performance at TA = 25°C using the internal 2.048-V reference. Data shown are the result of averaging readings from a single device over a time period of approximately 0.75 seconds and are measured with the inputs internally shorted together. Table 1, Table 3, Table 5, and Table 7 list the input-referred noise in units of μVRMS for the conditions shown. Values in µVPP are shown in parenthesis. Table 2, Table 4, Table 6, and Table 8 list the corresponding data in effective resolution calculated from μVRMS values using Equation 1. Noise-free resolution calculated from peak-to-peak noise values using Equation 2 are shown in parenthesis.

The input-referred noise (Table 1, Table 3, Table 5, and Table 7) only changes marginally when using an external low-noise reference, such as the REF5020. Use Equation 1 and Equation 2 to calculate effective resolution numbers and noise-free resolution when using a reference voltage other than 2.048 V:

Table 1. Noise in μVRMS (μVPP)

at AVDD = 3.3 V, AVSS = 0 V, Normal Mode, PGA Enabled, and Internal VREF = 2.048 V

| DATA RATE

(SPS) |

GAIN (PGA Enabled) | |||||||

|---|---|---|---|---|---|---|---|---|

| 1 | 2 | 4 | 8 | 16 | 32 | 64 | 128 | |

| 20 | 5.10 (21.69) | 2.49 (10.71) | 1.25 (5.74) | 0.64 (2.92) | 0.41 (1.52) | 0.24 (0.98) | 0.14 (0.54) | 0.11 (0.46) |

| 45 | 6.53 (29.99) | 3.02 (14.47) | 1.67 (6.80) | 0.93 (4.00) | 0.52 (2.43) | 0.28 (1.39) | 0.17 (0.71) | 0.13 (0.57) |

| 90 | 9.01 (41.61) | 4.67 (24.36) | 2.41 (10.95) | 1.24 (6.54) | 0.73 (3.46) | 0.41 (2.06) | 0.25 (1.20) | 0.19 (0.91) |

| 175 | 12.78 (63.79) | 6.75 (37.30) | 3.26 (17.00) | 1.92 (9.81) | 1.02 (5.27) | 0.60 (3.32) | 0.35 (1.93) | 0.25 (1.49) |

| 330 | 17.75 (107.88) | 8.75 (48.95) | 4.72 (28.25) | 2.62 (14.47) | 1.42 (8.06) | 0.85 (4.64) | 0.50 (2.93) | 0.37 (1.91) |

| 600 | 24.73 (153.77) | 12.89 (76.01) | 6.81 (38.94) | 3.84 (22.30) | 2.02 (12.07) | 1.18 (6.69) | 0.70 (4.49) | 0.51 (3.14) |

| 1000 | 36.90 (228.90) | 18.07 (108.90) | 9.48 (58.24) | 5.49 (31.55) | 2.86 (17.41) | 1.65 (10.23) | 1.04 (6.21) | 0.73 (4.69) |

Table 2. Effective Resolution From RMS Noise (Noise-Free Resolution From Peak-to-Peak Noise)

at AVDD = 3.3 V, AVSS = 0 V, Normal Mode, PGA Enabled, and Internal VREF = 2.048 V

| DATA RATE

(SPS) |

GAIN (PGA Enabled) | |||||||

|---|---|---|---|---|---|---|---|---|

| 1 | 2 | 4 | 8 | 16 | 32 | 64 | 128 | |

| 20 | 19.62 (17.53) | 19.65 (17.54) | 19.64 (17.44) | 19.61 (17.22) | 19.25 (17.36) | 19.02 (16.99) | 18.80 (16.85) | 18.15 (16.09) |

| 45 | 19.26 (17.06) | 19.37 (17.11) | 19.23 (17.20) | 19.07 (16.94) | 18.91 (16.68) | 18.80 (16.49) | 18.52 (16.46) | 17.91 (15.78) |

| 90 | 18.79 (16.59) | 18.74 (16.36) | 18.70 (16.51) | 18.66 (16.23) | 18.42 (16.18) | 18.25 (15.92) | 17.97 (15.70) | 17.36 (15.10) |

| 175 | 18.29 (15.97) | 18.21 (15.74) | 18.26 (15.88) | 18.02 (15.48) | 17.94 (15.57) | 17.70 (15.23) | 17.48 (15.02) | 16.97 (14.39) |

| 330 | 17.82 (15.21) | 17.84 (15.35) | 17.73 (15.12) | 17.58 (15.15) | 17.46 (14.96) | 17.20 (14.75) | 16.97 (14.41) | 16.40 (14.03) |

| 600 | 17.34 (14.70) | 17.28 (14.72) | 17.20 (14.68) | 17.02 (14.70) | 16.95 (14.37) | 16.73 (14.22) | 16.46 (13.80) | 15.94 (13.32) |

| 1000 | 16.76 (14.13) | 16.79 (14.20) | 16.72 (14.10) | 16.51 (13.99) | 16.45 (13.99) | 16.24 (13.61) | 15.91 (13.33) | 15.42 (12.74) |

Table 3. Noise in μVRMS (μVPP)

at AVDD = 3.3 V, AVSS = 0 V, Normal Mode, PGA Disabled, and Internal VREF = 2.048 V

| DATA RATE

(SPS) |

GAIN (PGA Disabled) | ||

|---|---|---|---|

| 1 | 2 | 4 | |

| 20 | 5.04 (19.71) | 2.53 (10.06) | 1.57 (5.68) |

| 45 | 6.57 (33.34) | 3.43 (14.00) | 1.60 (6.98) |

| 90 | 8.75 (42.59) | 4.35 (22.83) | 2.13 (10.52) |

| 175 | 12.64 (65.71) | 6.27 (35.00) | 3.40 (16.83) |

| 330 | 18.58 (106.06) | 9.33 (52.59) | 4.54 (26.30) |

| 600 | 25.74 (150.81) | 12.57 (79.15) | 6.47 (36.87) |

| 1000 | 36.98 (221.61) | 18.67 (111.61) | 9.27 (55.07) |

Table 4. Effective Resolution From RMS Noise (Noise-Free Resolution From Peak-to-Peak Noise)

at AVDD = 3.3 V, AVSS = 0 V, Normal Mode, PGA Disabled, and Internal VREF = 2.048 V

| DATA RATE

(SPS) |

GAIN (PGA Disabled) | ||

|---|---|---|---|

| 1 | 2 | 4 | |

| 20 | 19.63 (17.66) | 19.63 (17.64) | 19.32 (17.46) |

| 45 | 19.25 (16.91) | 19.19 (17.16) | 19.29 (17.16) |

| 90 | 18.84 (16.55) | 18.84 (16.45) | 18.87 (16.57) |

| 175 | 18.31 (15.93) | 18.32 (15.84) | 18.20 (15.89) |

| 330 | 17.75 (15.24) | 17.74 (15.25) | 17.78 (15.25) |

| 600 | 17.28 (14.73) | 17.31 (14.66) | 17.27 (14.76) |

| 1000 | 16.76 (14.17) | 16.74 (14.16) | 16.75 (14.18) |

Table 5. Noise in μVRMS (μVPP)

at AVDD = 3.3 V, AVSS = 0 V, Turbo Mode, PGA Enabled, and Internal VREF = 2.048 V

| DATA RATE

(SPS) |

GAIN (PGA Enabled) | |||||||

|---|---|---|---|---|---|---|---|---|

| 1 | 2 | 4 | 8 | 16 | 32 | 64 | 128 | |

| 40 | 4.41 (19.43) | 2.25 (10.62) | 1.12 (5.32) | 0.63 (2.74) | 0.36 (1.64) | 0.22 (1.10) | 0.13 (0.63) | 0.10 (0.51) |

| 90 | 5.76 (30.73) | 2.98 (14.16) | 1.62 (7.84) | 0.92 (4.43) | 0.52 (2.59) | 0.31 (1.59) | 0.18 (0.97) | 0.15 (0.76) |

| 180 | 8.49 (44.61) | 4.48 (22.25) | 2.29 (13.23) | 1.34 (6.83) | 0.71 (4.11) | 0.43 (2.49) | 0.28 (1.51) | 0.22 (1.05) |

| 350 | 12.77 (71.04) | 6.33 (37.00) | 3.33 (19.17) | 1.89 (10.76) | 1.04 (5.91) | 0.61 (3.54) | 0.41 (2.13) | 0.29 (1.64) |

| 660 | 17.10 (105.64) | 9.04 (54.97) | 4.51 (27.74) | 2.84 (16.98) | 1.42 (8.45) | 0.86 (5.07) | 0.57 (3.32) | 0.41 (2.38) |

| 1200 | 25.26 (153.74) | 12.51 (78.75) | 6.58 (39.68) | 3.90 (23.84) | 2.11 (13.19) | 1.23 (7.46) | 0.81 (5.17) | 0.58 (3.50) |

| 2000 | 35.35 (226.39) | 17.82 (112.98) | 9.40 (59.37) | 5.37 (32.97) | 3.02 (18.73) | 1.76 (11.12) | 1.12 (7.06) | 0.83 (5.41) |

Table 6. Effective Resolution From RMS Noise (Noise-Free Resolution From Peak-to-Peak Noise)

at AVDD = 3.3 V, AVSS = 0 V, Turbo Mode, PGA Enabled, and Internal VREF = 2.048 V

| DATA RATE

(SPS) |

GAIN (PGA Enabled) | |||||||

|---|---|---|---|---|---|---|---|---|

| 1 | 2 | 4 | 8 | 16 | 32 | 64 | 128 | |

| 40 | 19.83 (17.69) | 19.80 (17.56) | 19.80 (17.55) | 19.63 (17.51) | 19.44 (17.25) | 19.15 (16.83) | 18.91 (16.63) | 18.29 (15.94) |

| 90 | 19.44 (17.02) | 19.39 (17.14) | 19.27 (16.99) | 19.09 (16.82) | 18.91 (16.59) | 18.66 (16.30) | 18.44 (16.01) | 17.70 (15.36) |

| 180 | 18.88 (16.49) | 18.80 (16.49) | 18.77 (16.24) | 18.54 (16.19) | 18.46 (15.93) | 18.18 (15.65) | 17.80 (15.37) | 17.15 (14.90) |

| 350 | 18.29 (15.82) | 18.30 (15.76) | 18.23 (15.71) | 18.05 (15.55) | 17.91 (15.40) | 17.68 (15.14) | 17.25 (14.87) | 16.75 (14.25) |

| 660 | 17.87 (15.24) | 17.79 (15.19) | 17.79 (15.17) | 17.46 (14.88) | 17.46 (14.89) | 17.18 (14.62) | 16.78 (14.23) | 16.25 (13.71) |

| 1200 | 17.31 (14.70) | 17.32 (14.67) | 17.25 (14.66) | 17.00 (14.39) | 16.89 (14.24) | 16.67 (14.07) | 16.27 (13.60) | 15.75 (13.16) |

| 2000 | 16.82 (14.14) | 16.81 (14.15) | 16.73 (14.07) | 16.54 (13.92) | 16.37 (13.74) | 16.15 (13.49) | 15.80 (13.15) | 15.23 (12.53) |

Table 7. Noise in μVRMS (μVPP)

at AVDD = 3.3 V, AVSS = 0 V, Turbo Mode, PGA Disabled, and Internal VREF = 2.048 V

| DATA RATE

(SPS) |

GAIN (PGA Disabled) | ||

|---|---|---|---|

| 1 | 2 | 4 | |

| 40 | 4.30 (18.73) | 2.18 (9.84) | 1.10 (5.38) |

| 90 | 6.19 (32.78) | 3.14 (13.53) | 1.42 (7.19) |

| 180 | 9.08 (47.57) | 4.49 (25.48) | 2.18 (10.96) |

| 350 | 12.40 (72.79) | 5.89 (33.34) | 3.07 (18.31) |

| 660 | 17.59 (103.97) | 9.05 (51.15) | 4.39 (24.69) |

| 1200 | 24.67 (149.07) | 12.56 (76.35) | 6.31 (37.48) |

| 2000 | 34.54 (224.19) | 17.76 (113.98) | 8.85 (56.87) |

Table 8. Effective Resolution From RMS Noise (Noise-Free Resolution From Peak-to-Peak Noise)

at AVDD = 3.3 V, AVSS = 0 V, Turbo Mode, PGA Disabled, and Internal VREF = 2.048 V

| DATA RATE

(SPS) |

GAIN (PGA Disabled) | ||

|---|---|---|---|

| 1 | 2 | 4 | |

| 40 | 19.86 (17.74) | 19.84 (17.67) | 19.83 (17.54) |

| 90 | 19.34 (16.93) | 19.32 (17.21) | 19.46 (17.12) |

| 180 | 18.78 (16.39) | 18.80 (16.29) | 18.84 (16.51) |

| 350 | 18.33 (15.78) | 18.41 (15.91) | 18.34 (15.77) |

| 660 | 17.83 (15.27) | 17.79 (15.29) | 17.83 (15.34) |

| 1200 | 17.34 (14.75) | 17.32 (14.71) | 17.31 (14.74) |

| 2000 | 16.86 (14.16) | 16.82 (14.13) | 16.82 (14.14) |

9 Detailed Description

9.1 Overview

The ADS122C04 is a small, low-power, 24-bit, ΔΣ ADC that offers many integrated features to reduce system cost and component count in applications measuring small sensor signals.

In addition to the ΔΣ ADC core and single-cycle settling digital filter, the device offers a low-noise, high input impedance, programmable gain amplifier (PGA), an internal 2.048-V voltage reference, and a clock oscillator. The device also integrates a highly linear and accurate temperature sensor as well as two matched programmable current sources (IDACs) for sensor excitation. All of these features are intended to reduce the required external circuitry in typical sensor applications and improve overall system performance. The device is fully configured through four registers and controlled by six commands through an I2C-compatible interface. The Functional Block Diagram section shows the device functional block diagram.

The ADS122C04 ADC measures a differential signal, VIN, which is the difference in voltage between nodes AINP and AINN. The converter core consists of a differential, switched-capacitor, ΔΣ modulator followed by a digital filter. The digital filter receives a high-speed bitstream from the modulator and outputs a code proportional to the input voltage. This architecture results in a very strong attenuation of any common-mode signal.

The device has two available conversion modes: single-shot conversion and continuous conversion mode. In single-shot conversion mode, the ADC performs one conversion of the input signal upon request and stores the value in an internal data buffer. The device then enters a low-power state to save power. Single-shot conversion mode is intended to provide significant power savings in systems that require only periodic conversions, or when there are long idle periods between conversions. In continuous conversion mode, the ADC automatically begins a conversion of the input signal as soon as the previous conversion is completed. New data are available at the programmed data rate. Data can be read at any time without concern of data corruption and always reflect the most recently completed conversion.

9.2 Functional Block Diagram

9.3 Feature Description

9.3.1 Multiplexer

Figure 42 shows the flexible input multiplexer of the device. Either four single-ended signals, two differential signals, or a combination of two single-ended signals and one differential signal can be measured. The multiplexer is configured by four bits (MUX[3:0]) in the configuration register. When single-ended signals are measured, the negative ADC input (AINN) is internally connected to AVSS by a switch within the multiplexer. For system-monitoring purposes, the analog supply [(AVDD – AVSS) / 4] or the currently selected external reference voltage [(VREFP – VREFN) / 4] can be selected as inputs to the ADC. The multiplexer also offers the possibility to route any of the two programmable current sources to any analog input (AINx) or to the dedicated reference pins (REFP, REFN).

Figure 42. Analog Input Multiplexer

Figure 42. Analog Input Multiplexer Electrostatic discharge (ESD) diodes to AVDD and AVSS protect the inputs. The absolute voltage on any input must stay within the range provided by Equation 3 to prevent the ESD diodes from turning on:

If the voltages on the input pins have any potential to violate these conditions, external Schottky clamp diodes or series resistors may be required to limit the input current to safe values (see the Absolute Maximum Ratings table). Overdriving an unused input on the device can affect conversions taking place on other input pins.

9.3.2 Low-Noise Programmable Gain Stage

The device features programmable gains of 1, 2, 4, 8, 16, 32, 64, and 128. Three bits (GAIN[2:0]) in the configuration register are used to configure the gain. Gains are achieved in two stages. The first stage is a low-noise, low-drift, high input impedance, programmable gain amplifier (PGA). The second gain stage is implemented by a switched-capacitor circuit at the input to the ΔΣ modulator. Table 9 shows how each gain is implemented.

Table 9. Gain Implementation

| GAIN SETTING | PGA GAIN | SWITCHED-CAPACITOR GAIN |

|---|---|---|

| 1 | 1 | 1 |

| 2 | 1 | 2 |

| 4 | 1 | 4 |

| 8 | 2 | 4 |

| 16 | 4 | 4 |

| 32 | 8 | 4 |

| 64 | 16 | 4 |

| 128 | 32 | 4 |

The PGA consists of two chopper-stabilized amplifiers (A1 and A2) and a resistor feedback network that sets the PGA gain. The input is equipped with an electromagnetic interference (EMI) filter. Figure 43 shows a simplified diagram of the PGA.

Figure 43. Simplified PGA Diagram

Figure 43. Simplified PGA Diagram VIN denotes the differential input voltage VIN = VAINP – VAINN. Use Equation 4 to calculate the gain of the PGA. Gain is changed inside the device using a variable resistor, RG.

The switched-capacitor gain is changed using variable capacitors at the input to the ΔΣ modulator. Gains 1, 2, and 4 are implemented by using only the switched-capacitor circuit, which allows these gains to be used even when the PGA is bypassed; see the Bypassing the PGA section for more information about bypassing the PGA.

Equation 5 shows that the differential full-scale input voltage range (FSR) of the device is defined by the gain setting and the reference voltage used:

Table 10 shows the corresponding full-scale ranges when using the internal 2.048-V reference.

Table 10. Full-Scale Range

| GAIN SETTING | FSR |

|---|---|

| 1 | ±2.048 V |

| 2 | ±1.024 V |

| 4 | ±0.512 V |

| 8 | ±0.256 V |

| 16 | ±0.128 V |

| 32 | ±0.064 V |

| 64 | ±0.032 V |

| 128 | ±0.016 V |

9.3.2.1 PGA Input Voltage Requirements

As with many amplifiers, the PGA has an absolute input voltage range requirement that cannot be exceeded. The maximum and minimum absolute input voltages are limited by the voltage swing capability of the PGA output. The specified minimum and maximum absolute input voltages (VAINP and VAINN) depend on the PGA gain, the maximum differential input voltage (VINMAX), and the tolerance of the analog power-supply voltages (AVDD and AVSS). Because gain on the ADS122C04 is implemented by both the PGA and a switched-capacitor gain circuit, there are two formulas that define the absolute input voltages. Use Equation 6 when the device gain is configured to less than or equal to 4. Use Equation 7 when the device gain is greater than 4. Use the maximum differential input voltage expected in the application for VINMAX.

Figure 44 graphically shows the relationship between the PGA input voltages to the PGA output voltages for gains larger than 4. The PGA output voltages (VOUTP, VOUTN) depend on the PGA gain and the differential input voltage magnitudes. For linear operation, the PGA output voltages must not exceed AVDD – 0.2 V or AVSS + 0.2 V. Figure 44 depicts an example of a positive differential input voltage that results in a positive differential output voltage.

Figure 44. PGA Input/Output Voltage Relationship

Figure 44. PGA Input/Output Voltage Relationship 9.3.2.2 Bypassing the PGA

At gains of 1, 2, and 4, the device can be configured to disable and bypass the low-noise PGA by setting the PGA_BYPASS bit in the configuration register. Disabling the PGA lowers the overall power consumption and also removes the restrictions of Equation 6 and Equation 7 for the absolute input voltage range. The usable absolute input voltage range is (AVSS – 0.1 V ≤ VAINP, VAINN ≤ AVDD + 0.1 V) when the PGA is disabled.

In order to measure single-ended signals that are referenced to AVSS (AINP = VIN, AINN = AVSS), the PGA must be bypassed. Configure the device for single-ended measurements by either connecting one of the analog inputs to AVSS externally or by using the internal AVSS connection of the multiplexer (MUX[3:0] settings 1000 through 1011). When configuring the internal multiplexer for settings where AINN = AVSS (MUX[3:0] = 1000 through 1011), the PGA is automatically bypassed and disabled irrespective of the PGA_BYPASS setting and gain is limited to 1, 2, and 4. In case gain is set to greater than 4, the device limits gain to 4.

When the PGA is disabled, the device uses a buffered switched-capacitor stage to obtain gains 1, 2, and 4. An internal buffer in front of the switched-capacitor stage ensures that the effect on the input loading resulting from the capacitor charging and discharging is minimal. See the Electrical Characteristics section for the typical values of absolute input currents (current flowing into or out of each input) and differential input currents (difference in absolute current between the positive and negative input) when the PGA is disabled.

For signal sources with high output impedance, external buffering may still be necessary. Active buffers can introduce noise as well as offset and gain errors. Consider all of these factors in high-accuracy applications.

9.3.3 Voltage Reference

The device offers an integrated, low-drift, 2.048-V reference. For applications that require a different reference voltage value or a ratiometric measurement approach, the device offers a differential reference input pair (REFP and REFN). In addition, the analog supply (AVDD – AVSS) can be used as a reference.

The reference source is selected by two bits (VREF[1:0]) in the configuration register. By default, the internal reference is selected. The internal voltage reference requires less than 25 µs to fully settle after power-up, when coming out of power-down mode, or when switching from an external reference source to the internal reference.

The differential reference input allows freedom in the reference common-mode voltage. The reference inputs are internally buffered to increase input impedance. Therefore, additional reference buffers are usually not required when using an external reference. When used in ratiometric applications, the reference inputs do not load the external circuitry; however, the analog supply current increases when using an external reference because the reference buffers are enabled.

In most cases the conversion result is directly proportional to the stability of the reference source. Any noise and drift of the voltage reference is reflected in the conversion result.

9.3.4 Modulator and Internal Oscillator

A ΔΣ modulator is used in the ADS122C04 to convert the analog input voltage into a pulse code modulated (PCM) data stream. The modulator runs at a modulator clock frequency of fMOD = fCLK / 4, where fCLK is provided by the internal oscillator. The oscillator frequency, and therefore also the modulator frequency, depend on the selected operating mode. Table 11 shows the oscillator and modulator frequencies for the different operating modes.

Table 11. Oscillator and Modulator Clock Frequencies for Different Operating Modes

| OPERATING MODE | fCLK | fMOD |

|---|---|---|

| Normal mode | 1.024 MHz | 256 kHz |

| Turbo mode | 2.048 MHz | 512 kHz |

9.3.5 Digital Filter

The device uses a linear-phase finite impulse response (FIR) digital filter that performs both filtering and decimation of the digital data stream coming from the modulator. The digital filter is automatically adjusted for the different data rates and always settles within a single cycle. The frequency responses of the digital filter are illustrated in Figure 45 to Figure 53 for different output data rates. The filter notches and output data rate scale proportionally with the clock frequency. The internal oscillator can vary over temperature as specified in the Electrical Characteristics table. The data rate or conversion time, respectively, and consequently also the filter notches vary proportionally.

Figure 45. Filter Response

Figure 45. Filter Response

(Normal Mode, DR = 20 SPS)

Figure 47. Filter Response

Figure 47. Filter Response

(Normal Mode, DR = 45 SPS)

Figure 46. Detailed View of the Filter Response

Figure 46. Detailed View of the Filter Response

(Normal Mode, DR = 20 SPS)

Figure 48. Filter Response

Figure 48. Filter Response

(Normal Mode, DR = 90 SPS)

Figure 49. Filter Response

Figure 49. Filter Response

(Normal Mode, DR = 175 SPS)

Figure 51. Filter Response

Figure 51. Filter Response

(Normal Mode, DR = 600 SPS)

Figure 53. Filter Response

Figure 53. Filter Response

(Turbo Mode, DR = 2 kSPS)

Figure 50. Filter Response

Figure 50. Filter Response

(Normal Mode, DR = 330 SPS)

Figure 52. Filter Response

Figure 52. Filter Response

(Normal Mode, DR = 1 kSPS)

9.3.6 Conversion Times

Table 12 shows the actual conversion times for each data rate setting. The values provided are in terms of tCLK cycles and in milliseconds.

Continuous conversion mode data rates are timed from one DRDY falling edge to the next DRDY falling edge. The first conversion starts 28.5 · tCLK (normal mode) or 105 · tCLK (turbo mode) after the START/SYNC command is latched.

Single-shot conversion mode data rates are timed from when the START/SYNC command is latched to the DRDY falling edge and rounded to the next tCLK.

Commands are latched on the eighth falling edge of SCL in the command byte.

Table 12. Conversion Times

| NOMINAL DATA RATE

(SPS) |

–3-dB BANDWIDTH

(Hz) |

CONTINUOUS CONVERSION MODE(2) | SINGLE-SHOT CONVERSION MODE | ||

|---|---|---|---|---|---|

| ACTUAL CONVERSION TIME (tCLK)(1) | ACTUAL CONVERSION TIME (ms) | ACTUAL CONVERSION TIME (tCLK)(1) | ACTUAL CONVERSION TIME (ms) | ||

| NORMAL MODE | |||||

| 20 | 13.1 | 51192 | 49.99 | 51213 | 50.01 |

| 45 | 20.0 | 22780 | 22.5 | 22805 | 22.27 |

| 90 | 39.6 | 11532 | 11.26 | 11557 | 11.29 |

| 175 | 77.8 | 5916 | 5.78 | 5941 | 5.80 |

| 330 | 150.1 | 3116 | 3.04 | 3141 | 3.07 |

| 600 | 279.0 | 1724 | 1.68 | 1749 | 1.71 |

| 1000 | 483.8 | 1036 | 1.01 | 1061 | 1.04 |

| TURBO MODE | |||||

| 40 | 17.1 | 51192 | 25.00 | 51217 | 25.01 |

| 90 | 39.9 | 22780 | 11.12 | 22809 | 11.14 |

| 180 | 79.2 | 11532 | 5.63 | 11561 | 5.65 |

| 350 | 155.6 | 5916 | 2.89 | 5945 | 2.90 |

| 660 | 300.3 | 3116 | 1.52 | 3145 | 1.54 |

| 1200 | 558.1 | 1724 | 0.84 | 1753 | 0.86 |

| 2000 | 967.6 | 1036 | 0.51 | 1065 | 0.52 |

Although the conversion time at the 20-SPS setting is not exactly 1 / 20 Hz = 50 ms, this discrepancy does not affect the 50-Hz or 60-Hz rejection. The conversion time and filter notches vary by the amount specified in the Electrical Characteristics table for oscillator accuracy.

9.3.7 Excitation Current Sources

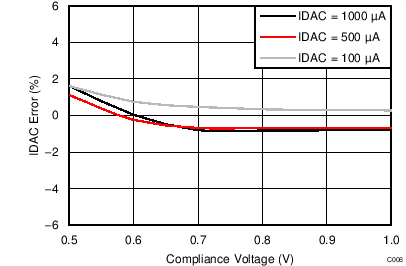

The device provides two matched programmable excitation current sources (IDACs) for resistance temperature detector (RTD) applications. The output current of the current sources can be programmed to 10 µA, 50 µA, 100 µA, 250 µA, 500 µA, 1000 µA, or 1500 µA using the respective bits (IDAC[2:0]) in the configuration register. Each current source can be connected to any of the analog inputs (AINx) as well as to the dedicated reference inputs (REFP and REFN). Both current sources can also be connected to the same pin. Routing of the IDACs is configured by bits (I1MUX[2:0], I2MUX[2:0]) in the configuration register. Care must be taken not to exceed the compliance voltage of the IDACs. In other words, limit the voltage on the pin where the IDAC is routed to ≤ (AVDD – 0.9 V), otherwise the specified accuracy of the IDAC current is not met. For three-wire RTD applications, the matched current sources can be used to cancel errors caused by sensor lead resistance (see the 3-Wire RTD Measurement section for more details).

The IDACs require up to 200 µs to start up after the IDAC current is programmed to the respective value using the IDAC[2:0] bits. Set the IDAC current to the respective value using the IDAC[2:0] bits and then select the routing for each IDAC (I1MUX[2:0], I2MUX[2:0]) thereafter.

In single-shot conversion mode, the IDACs remain active between any two conversions if the IDAC[2:0] bits are set to a value other than 000. However, the IDACs are powered down whenever the POWERDOWN command is issued.

Keep in mind that the analog supply current increases when enabling the IDACs (that is, when the IDAC[2:0] bits are set to a value other than 000). The IDAC circuit needs this bias current to operate even when the IDACs are not routed to any pin (I1MUX[2:0] = I2MUX[2:0] = 000). In addition, the selected output current is drawn from the analog supply when I1MUX[2:0] or I2MUX[2:0] are set to a value other than 000.

9.3.8 Sensor Detection

To help detect a possible sensor malfunction, the device provides internal 10-µA, burn-out current sources. When enabled by setting the respective bit (BCS) in the configuration register, one current source provides current to the positive analog input (AINP) currently selected and the other current source sinks current from the selected negative analog input (AINN).

In case of an open circuit in the sensor, these burn-out current sources pull the positive input towards AVDD and the negative input towards AVSS, resulting in a full-scale reading. A full-scale reading can also indicate that the sensor is overloaded or that the reference voltage is absent. A near-zero reading can indicate a shorted sensor. The absolute value of the burn-out current sources typically varies by ±5% and the internal multiplexer adds a small series resistance. Therefore, distinguishing a shorted sensor condition from a normal reading can be difficult, especially if an RC filter is used at the inputs. In other words, even if the sensor is shorted, the voltage drop across the external filter resistance and the residual resistance of the multiplexer causes the output to read a value higher than zero.

Keep in mind that ADC readings of a functional sensor may be corrupted when the burn-out current sources are enabled. Disable the burn-out current sources when preforming the precision measurement, and only enable these sources to test for sensor fault conditions.

9.3.9 System Monitor

The device provides some means for monitoring the analog power supply and the external voltage reference. To select a monitoring voltage, the internal multiplexer (MUX[3:0]) must be configured accordingly in the configuration register. The device automatically bypasses the PGA and sets the gain to 1, irrespective of the configuration register settings when the monitoring feature is used. The system monitor function only provides a coarse result and is not meant to be a precision measurement.

When measuring the analog power supply (MUX[3:0] = 1101), the resulting conversion is approximately (AVDD – AVSS) / 4. The device uses the internal 2.048-V reference for the measurement regardless of what reference source is selected in the configuration register (VREF[1:0]).

When monitoring the external reference voltage source (MUX[3:0] = 1100), the result is approximately (V(REFP) – V(REFN)) / 4. The device automatically uses the internal reference for the measurement.

9.3.10 Temperature Sensor

The ADS122C04 offers an integrated precision temperature sensor. The temperature sensor mode is enabled by setting the TS bit = 1 in the configuration register. When in temperature sensor mode, the settings of configuration register 0 have no effect and the device uses the internal reference for measurement, regardless of the selected voltage reference source. Temperature readings follow the same process as the analog inputs for starting and reading conversion results. Temperature data are represented as a 14-bit effective result that is left-justified within the 24-bit conversion result. When reading the three data bytes, the first 14 bits (MSBs) are used to indicate the temperature measurement result. The LSBs of the data output do not indicate temperature. Only the 14 MSBs are relevant. One 14-bit LSB equals 0.03125°C. Negative numbers are represented in binary two's complement format. Table 13 shows the mapping between temperature and digital codes.

Table 13. 14-Bit Temperature Data Format

| TEMPERATURE (°C) | DIGITAL OUTPUT | |

|---|---|---|

| BINARY | HEX | |

| 128 | 01 0000 0000 0000 | 1000 |

| 127.96875 | 00 1111 1111 1111 | 0FFF |

| 100 | 00 1100 1000 0000 | 0C80 |

| 75 | 00 1001 0110 0000 | 0960 |

| 50 | 00 0110 0100 0000 | 0640 |

| 25 | 00 0011 0010 0000 | 0320 |

| 0.25 | 00 0000 0000 1000 | 0008 |

| 0.03125 | 00 0000 0000 0001 | 0001 |

| 0 | 00 0000 0000 0000 | 0000 |

| –0.25 | 11 1111 1111 1000 | 3FF8 |

| –25 | 11 1100 1110 0000 | 3CE0 |

| –40 | 11 1011 0000 0000 | 3B00 |

9.3.10.1 Converting From Temperature to Digital Codes

9.3.10.1.1 For Positive Temperatures (For Example, 50°C):

Two's complement is not performed on positive numbers. Therefore, simply convert the number to binary code in a 14-bit, left-justified format with the MSB = 0 to denote the positive sign.

Example: 50°C / (0.03125°C per count) = 1600 = 0640h = 00 0110 0100 0000

9.3.10.1.2 For Negative Temperatures (For Example, –25°C):

Generate the two's complement of a negative number by complementing the absolute binary number and adding 1. Then, denote the negative sign with the MSB = 1.

Example: |–25°C| / (0.03125°C per count) = 800 = 0320h = 00 0011 0010 0000

Two's complement format: 11 1100 1101 1111 + 1 = 11 1100 1110 0000

9.3.10.2 Converting From Digital Codes to Temperature

To convert from digital codes to temperature, first check whether the MSB is a 0 or a 1. If the MSB is a 0, simply multiply the decimal code by 0.03125°C to obtain the result. If the MSB is a 1, subtract 1 from the result and complement all bits. Then, multiply the result by –0.03125°C.

Example: The device reads back 0960h: 0960h has an MSB = 0.

0960h · 0.03125°C = 2400 · 0.03125°C = 75°C

Example: The device reads back 3CE0h: 3CE0h has an MSB = 1.

Subtract 1 and complement the result: 3CE0h → 0320h

0320h · (–0.03125°C) = 800 · (–0.03125°C) = –25°C

9.3.11 Offset Calibration

The internal multiplexer offers the option to short both PGA inputs (AINP and AINN) to mid-supply (AVDD + AVSS) / 2. This option can be used to measure and calibrate the device offset voltage by storing the result of the shorted input voltage reading in a microcontroller and consequently subtracting the result from each following reading. Take multiple readings with the inputs shorted and average the result to reduce the effect of noise.

9.3.12 Conversion Data Counter

The ADS122C04 offers an optional data counter word to help the host determine if the conversion data are new. The DCNT bit in the configuration register enables the conversion data counter. The data counter appears as an 8-bit word that precedes the conversion data each time a conversion result is read. The reset value of the counter is 00h. The word increments each time the ADC completes a conversion. The counter rolls over to 00h after reaching FFh.

When the host reads a conversion result, the host can determine if the data being read are new by comparing the counter value with the counter value obtained with the last data read. If the counter values are the same, then this result indicates that no new conversion data are available from the ADC. The counter can also help the host determine if a conversion result was missed.

Reset the conversion data counter by clearing the DCNT bit to 0 and then setting DCNT back to 1. A device reset also resets the conversion data counter.

9.3.13 Data Integrity Features

There are two methods for ensuring data integrity for data output on the ADS122C04. Output data can be register contents or conversion results. The optional data counter word that precedes conversion data is covered by both data integrity options. The data integrity modes are configured using the CRC[1:0] bits in the configuration register. When CRC[1:0] = 01, a bitwise-inverted version of the data is output immediately following the most significant byte (MSB) of the data.

When CRC[1:0] = 10, a 16-bit CRC word is output immediately following the MSB of the data. In CRC mode, the checksum bytes are the 16-bit remainder of the bitwise exclusive-OR (XOR) of the data bytes with a CRC polynomial. The CRC is based on the CRC-16-CCITT polynomial: x16 + x12 + x5 + 1 with an initial value of FFFFh.

The 17 binary coefficients of the polynomial are: 1 0001 0000 0010 0001. To calculate the CRC, divide (XOR operation) the data bytes (excluding the CRC) with the polynomial and compare the calculated CRC values to the ADC CRC value. If the values do not match, a data transmission error has occurred. In the event of a data transmission error, read the data again.

The following list shows a general procedure to compute the CRC value:

- Left-shift the initial data value by 16 bits, with zeros padded to the right.

- Align the MSB of the CRC polynomial to the left-most, logic-one value of the data.

- Perform an XOR operation on the data value with the aligned CRC polynomial. The XOR operation creates a new, shorter-length value. The bits of the data values that are not in alignment with the CRC polynomial drop down and append to the right of the new XOR result.

- When the XOR result is less than 1 0000 0000 0000 0000, the procedure ends, yielding the 16-bit CRC value. Otherwise, continue with the XOR operation shown in step 2 using the current data value. The number of loop iterations depends on the value of the initial data.

9.4 Device Functional Modes

Figure 54 shows a flow chart of the different operating modes and how the device transitions from one mode to another.

9.4.1 Power-Up and Reset

The ADS122C04 is reset in one of three ways: either by a power-on reset, by the RESET pin, or by a RESET command.

When a reset occurs, the configuration registers reset to the default values and the device enters a low-power state. The device then waits for the START/SYNC command to enter conversion mode; see the I2C Timing Requirements table for reset timing information.

9.4.1.1 Power-On Reset

During power up, the device is held in reset. The power-on reset releases approximately 500 µs after both supplies have exceeded their respective power-up reset thresholds. After this time all internal circuitry (including the voltage reference) are stable and communication with the device is possible. As part of the power-on reset process, the device sets all bits in the configuration registers to the respective default settings. After power-up, the device enters a low-power state. This power-up behavior is intended to prevent systems with tight power-supply requirements from encountering a current surge during power-up.