JAJSGJ4D August 2018 – April 2021 UCC21530-Q1

PRODUCTION DATA

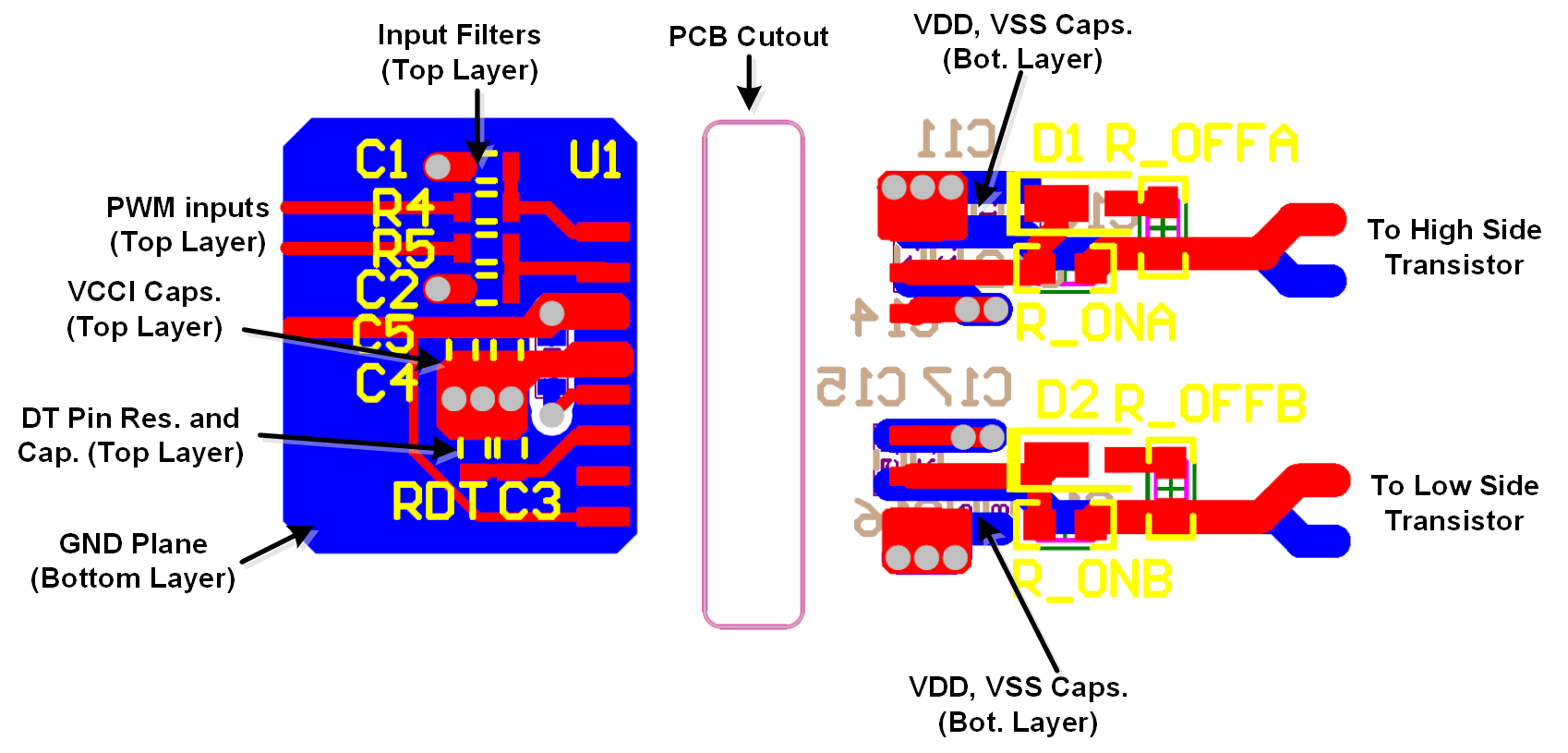

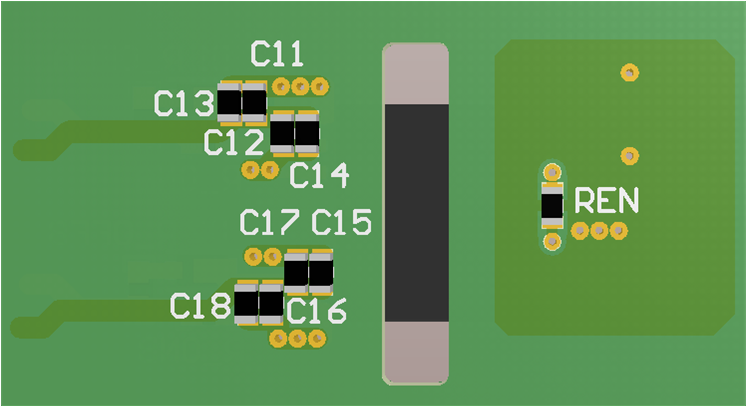

9.2 レイアウト例

2 層 PCB レイアウトの例を、図 9-1 に示します。この図では、信号と主要なコンポーネントにラベル付けされています。

図 9-1 レイアウト例

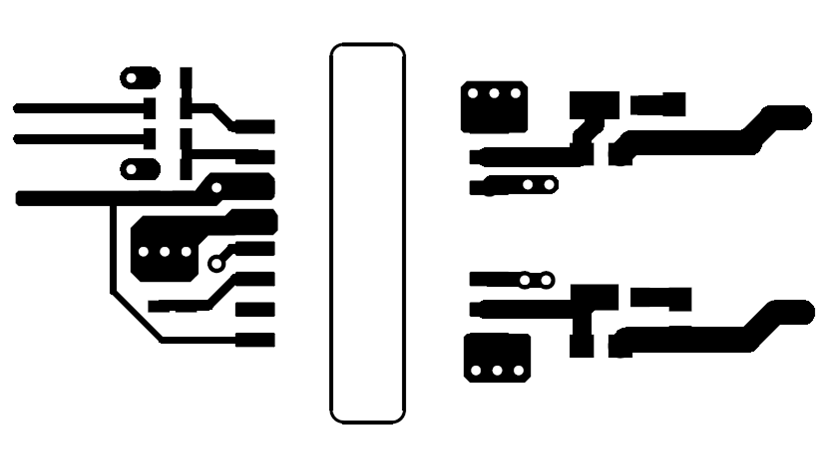

図 9-1 レイアウト例上層と下層のパターンと銅箔を、図 9-2 と図 9-3 に示します。

注:

1 次側と 2 次側の間に PCB パターンも銅箔も存在しないため、絶縁性能を確保できます。

高電圧動作に備えて沿面距離を最大化するため、出力段のハイサイド・ゲート・ドライバとローサイド・ゲート・ドライバの間の PCB パターンは拡大されています。これにより、高 dv/dt が発生する可能性があるスイッチング・ノード VSSA (SW) とローサイド・ゲート駆動の間の寄生容量結合によるクロストークも最小化されます。

図 9-2 上層のパターンと銅箔

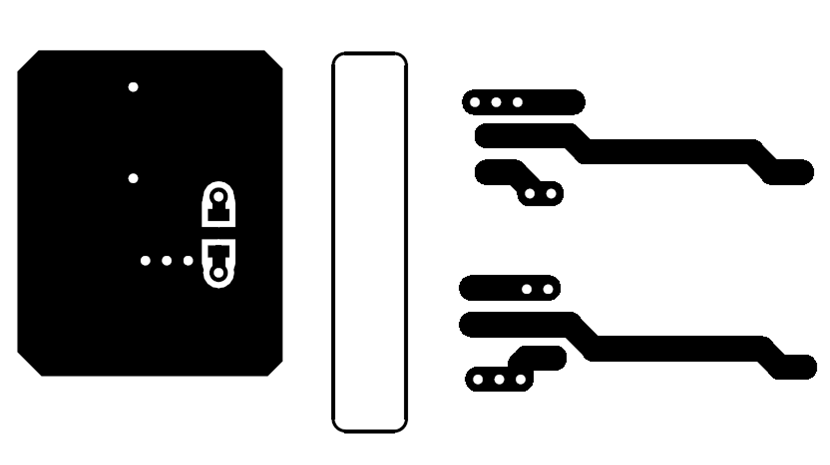

図 9-2 上層のパターンと銅箔 図 9-3 下層のパターンと銅箔

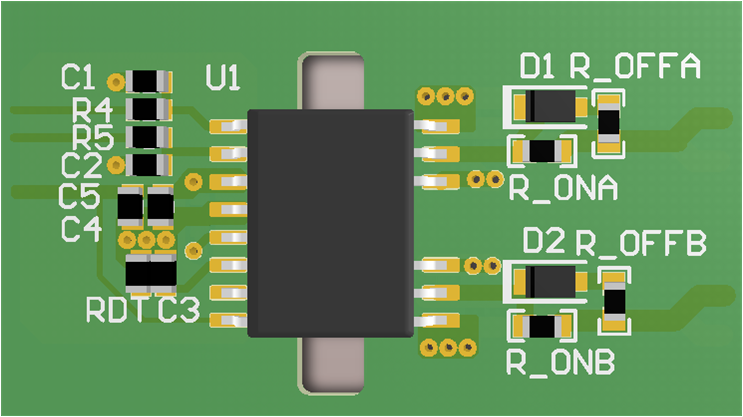

図 9-3 下層のパターンと銅箔3D レイアウト画像 (上面図と底面図) を、図 9-4 と図 9-5 に示します。

注:

1 次側と 2 次側の間の PCB カットアウトの場所に注意します。これにより、絶縁性能を確保しています。

図 9-4 PCB の 3D 上面図

図 9-4 PCB の 3D 上面図 図 9-5 PCB の 3D 底面図

図 9-5 PCB の 3D 底面図