-

UCC20225-Q1、UCC20225A-Q1 LGA、シングル入力、 絶縁型デュアルチャネル・ゲート・ドライバ、車載 48V システム用 JAJSGJ8C November 2018 – September 2019 UCC20225-Q1 , UCC20225A-Q1

PRODUCTION DATA.

-

UCC20225-Q1、UCC20225A-Q1 LGA、シングル入力、 絶縁型デュアルチャネル・ゲート・ドライバ、車載 48V システム用

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 概要(続き)

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Power Ratings

- 7.6 Insulation Specifications

- 7.7 Safety-Related Certifications

- 7.8 Safety Limiting Values

- 7.9 Electrical Characteristics

- 7.10 Switching Characteristics

- 7.11 Thermal Derating Curves

- 7.12 Typical Characteristics

- 8 Parameter Measurement Information

- 9 Detailed Description

-

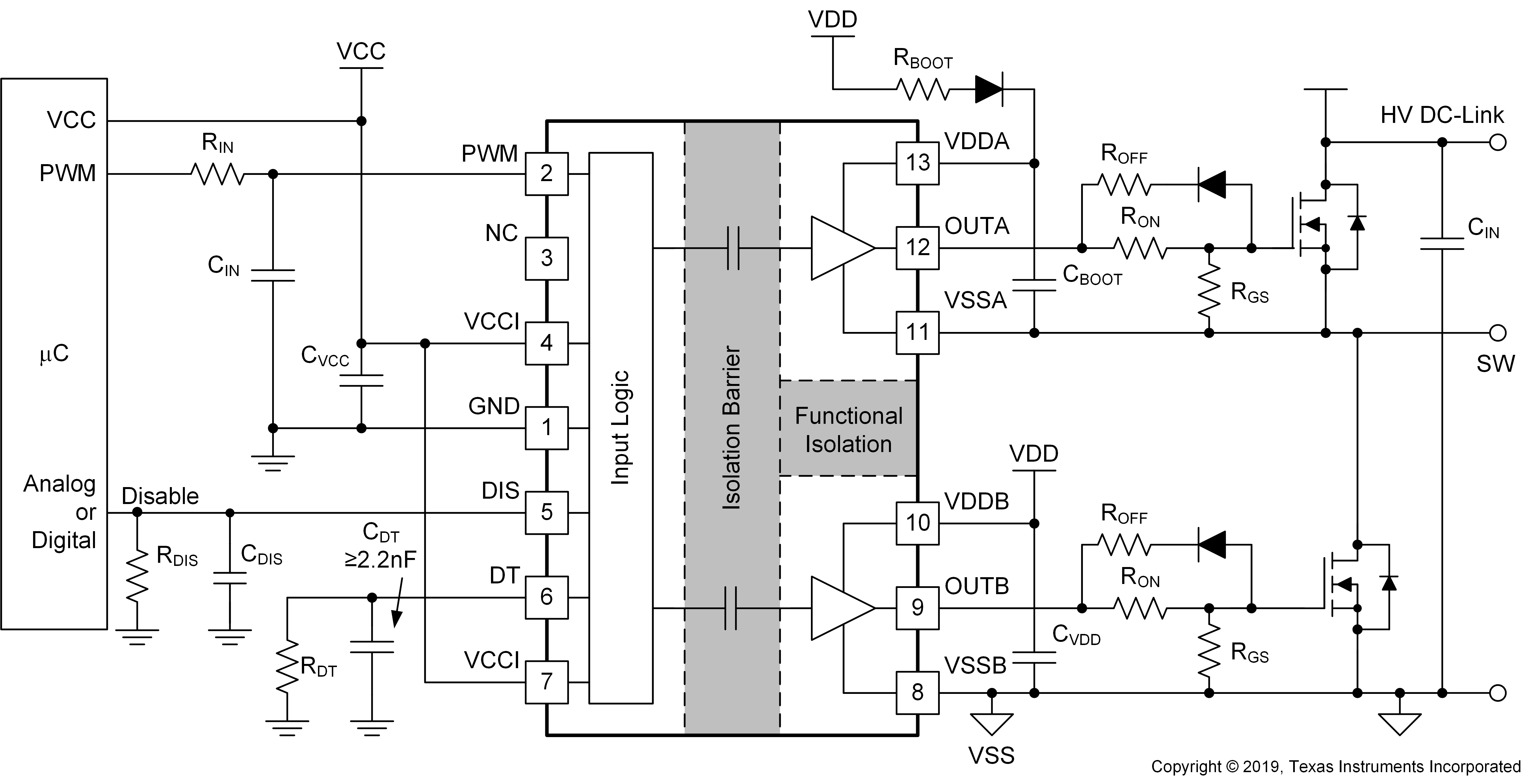

10Application and Implementation

- 10.1 Application Information

- 10.2

Typical Application

- 10.2.1 Design Requirements

- 10.2.2

Detailed Design Procedure

- 10.2.2.1 Designing PWM Input Filter

- 10.2.2.2 Select External Bootstrap Diode and its Series Resistor

- 10.2.2.3 Gate Driver Output Resistor

- 10.2.2.4 Estimate Gate Driver Power Loss

- 10.2.2.5 Estimating Junction Temperature

- 10.2.2.6 Selecting VCCI, VDDA/B Capacitor

- 10.2.2.7 Dead Time Setting Guidelines

- 10.2.2.8 Application Circuits with Output Stage Negative Bias

- 10.2.3 Application Curves

- 11Power Supply Recommendations

- 12Layout

- 13デバイスおよびドキュメントのサポート

- 14メカニカル、パッケージ、および注文情報

- 重要なお知らせ

DATA SHEET

UCC20225-Q1、UCC20225A-Q1 LGA、シングル入力、 絶縁型デュアルチャネル・ゲート・ドライバ、車載 48V システム用

このリソースの元の言語は英語です。 翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

1 特長

- 次の結果で AEC Q100 認定済み

- デバイス温度グレード 1

- デバイス HBM ESD 分類レベル H2

- デバイス CDM ESD 分類レベル C6

- シングル PWM 入力、デュアル出力

- デッド・タイムをレジスタでプログラム可能

- ピーク・ソース 4A、ピーク・シンク 6A の出力

- 100V/ns を超える CMTI

- スイッチング・パラメータ

- 19ns (標準値) の伝搬遅延

- 最大遅延マッチング: 5ns

- 最大パルス幅歪み: 6ns

- 3V~18V の入力 VCCI 範囲

- 最大 25V の VDD、5V および 8V の UVLO オプション

- 5ns より短い入力過渡を除去

- TTL および CMOS 互換の入力

- 5mm×5mm の省スペース LGA-13 パッケージ

- 安全関連の認定

- VDE V 0884-11:2017 に準拠した 3535VPK絶縁

- UL 1577 に準拠した絶縁耐圧:2500VRMS (1 分間)

- GB4943.1-2011準拠のCQC認定

2 アプリケーション

- 車載用外部オーディオ・アンプ

- 車載用 48V システム

3 概要

UCC20225-Q1 ファミリは シングル入力、デュアル出力で、ピーク電流がソース 4A、シンク 6A の絶縁型ゲート・ドライバであり、5mm x 5mm の LGA-13 パッケージに搭載されています。パワー・トランジスタを最大5MHzで駆動するよう設計され、クラス最高の伝搬遅延とパルス幅歪みを実現しています。

入力側は、2.5kVRMSの絶縁バリアによって2つの出力ドライバと分離され、同相過渡耐性(CMTI)は最小で100V/nsです。2つの出力側ドライバ間が内部で機能的に絶縁されているため、最大700VDCの動作電圧が可能です。

UCC20225-Q1 ファミリは、DT ピンの抵抗によりデッドタイムをプログラムできます。DIS ピンが HIGH に設定されると、両方の出力が同時にシャットダウンし、接地したときには通常動作します。

製品情報(1)

| 型番 | パッケージ | UVLO |

|---|---|---|

| UCC20225A-Q1 | LGA (13) 5 × 5mm | 5V |

| UCC20225-Q1 | LGA (13) 5 × 5mm | 8V |

- 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

Device Images

機能ブロック図