JAJSJ53B may 2020 – april 2023 TPD3S713-Q1 , TPD3S713A-Q1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

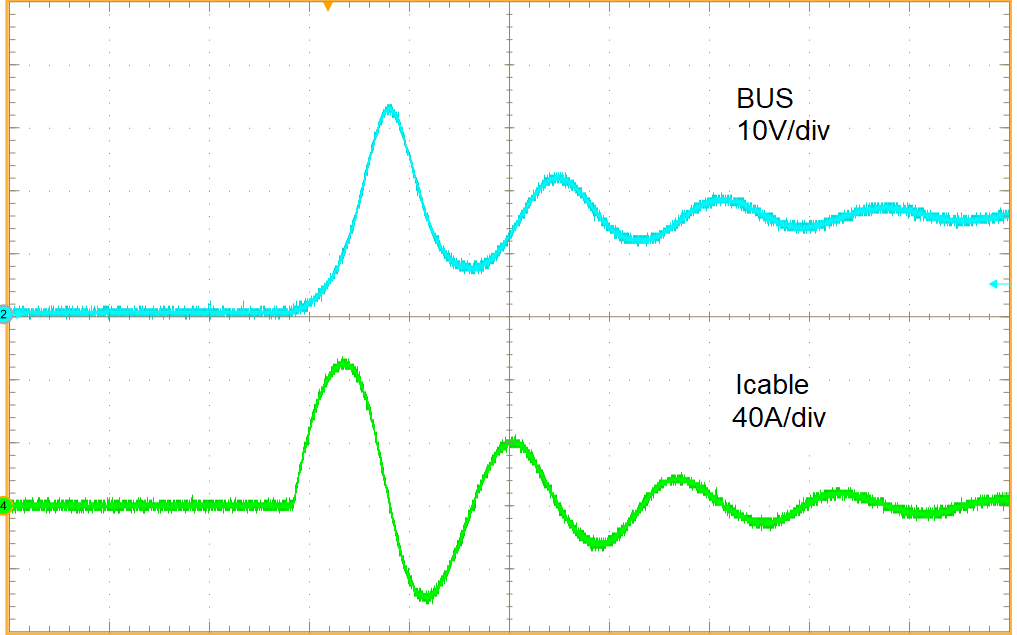

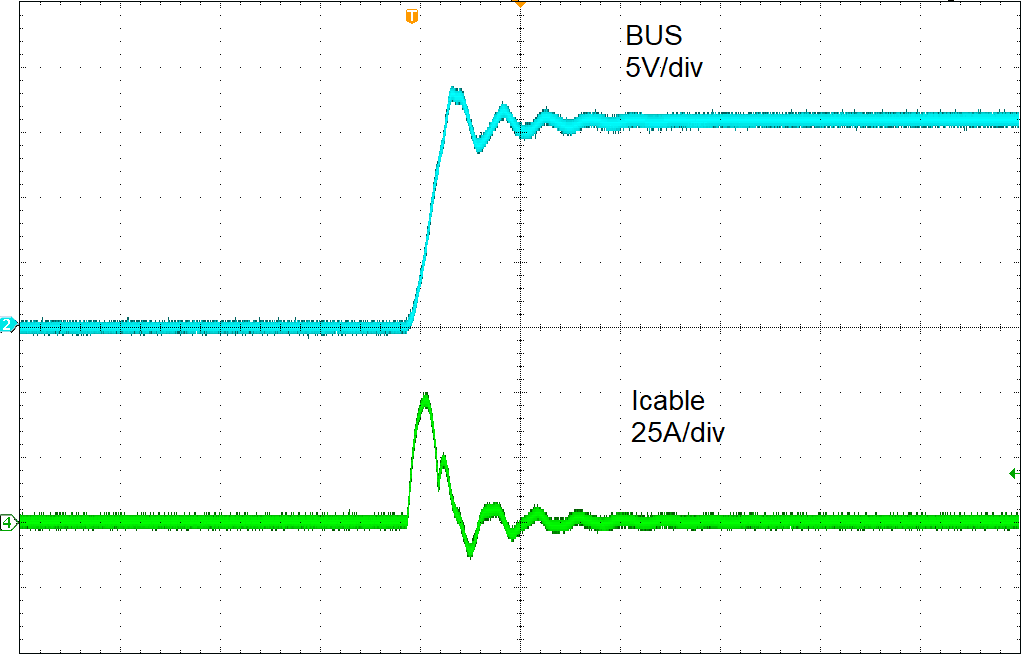

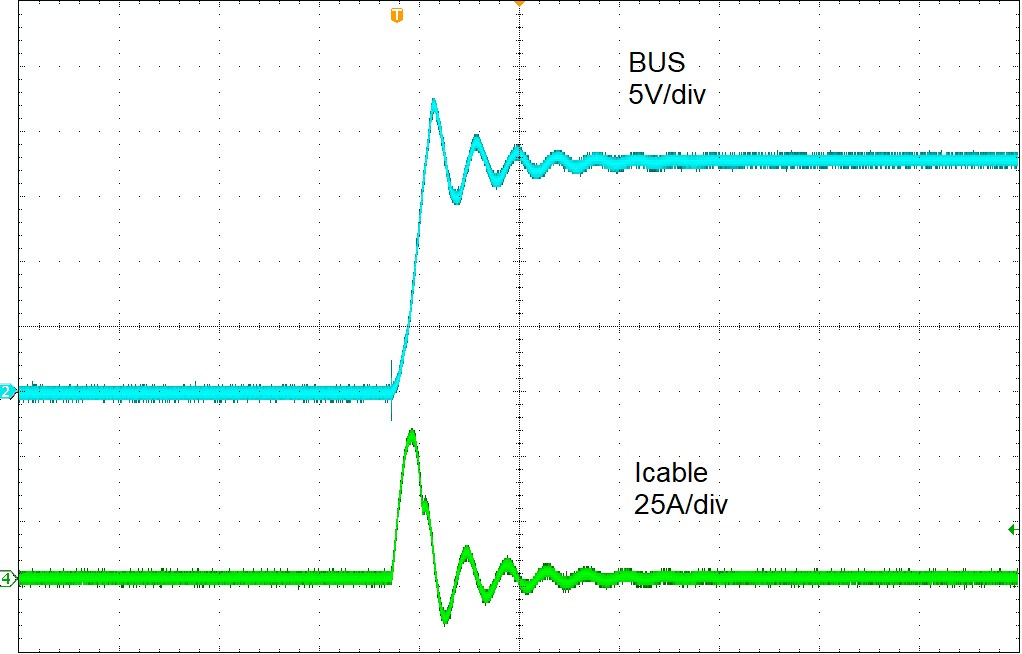

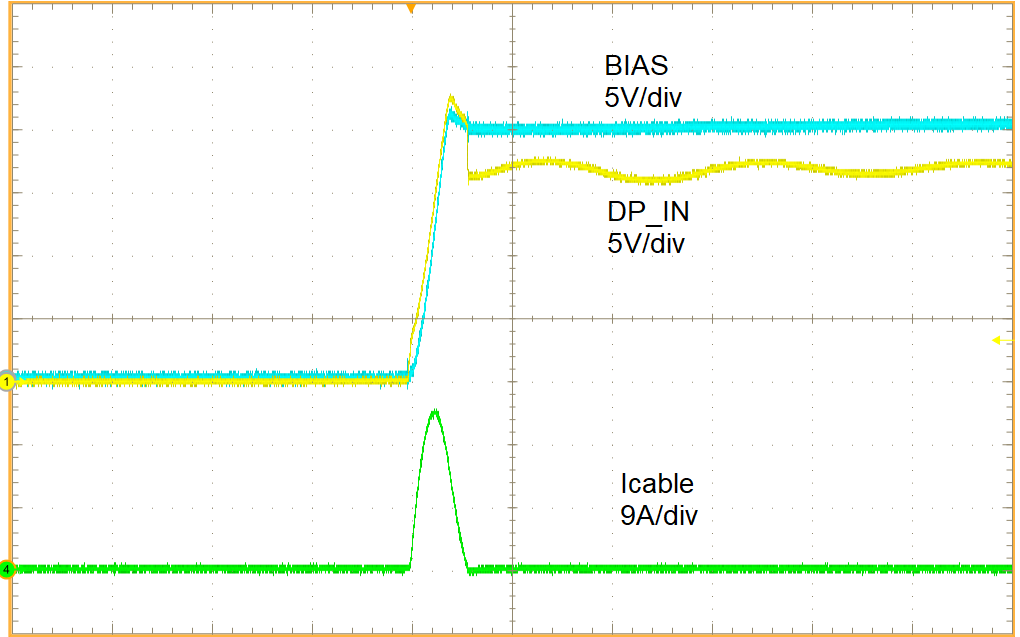

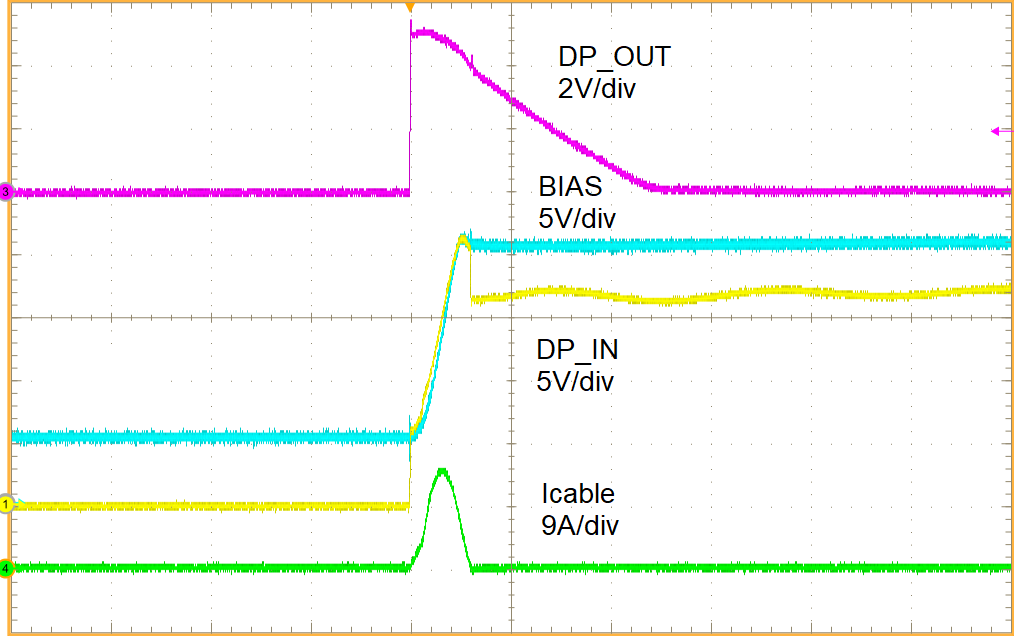

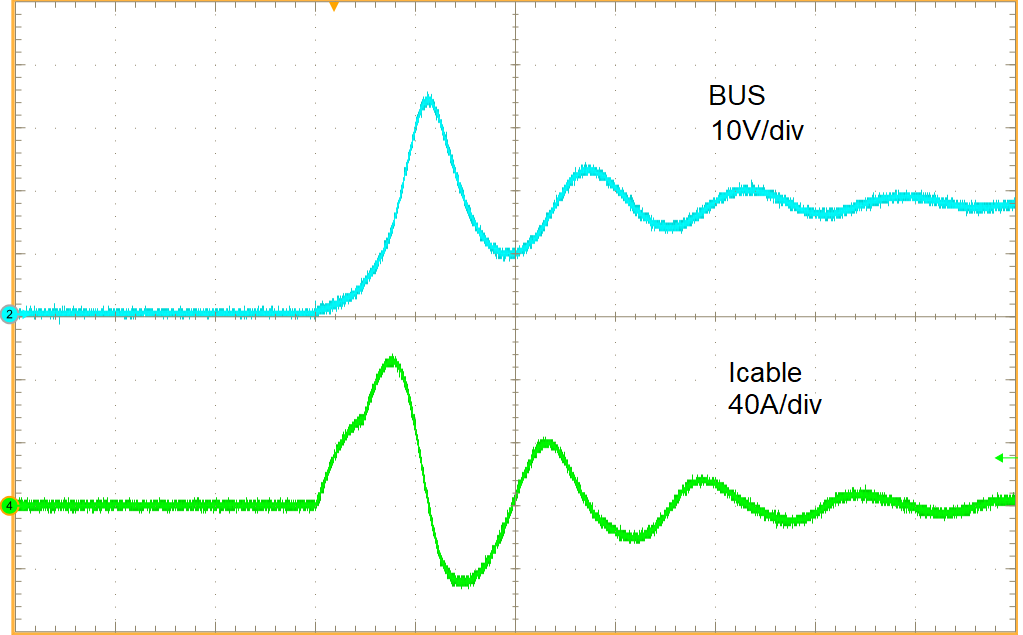

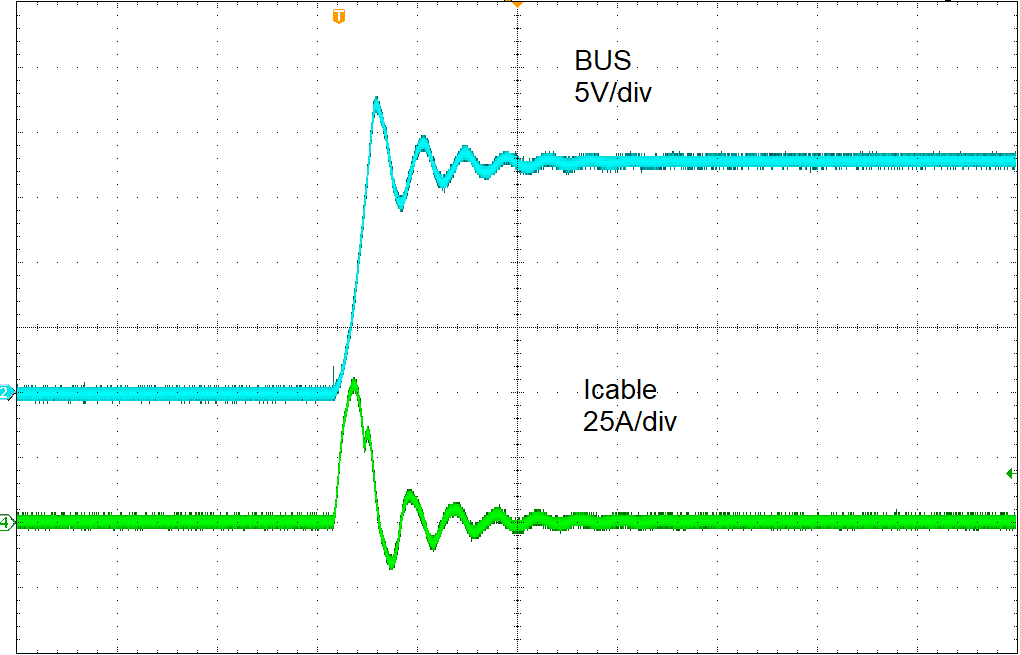

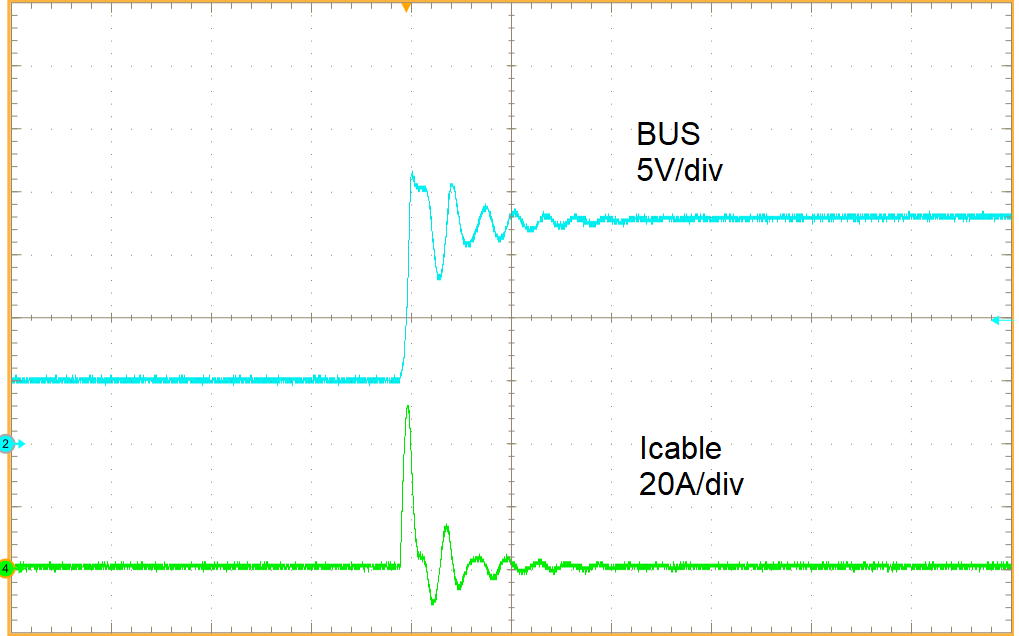

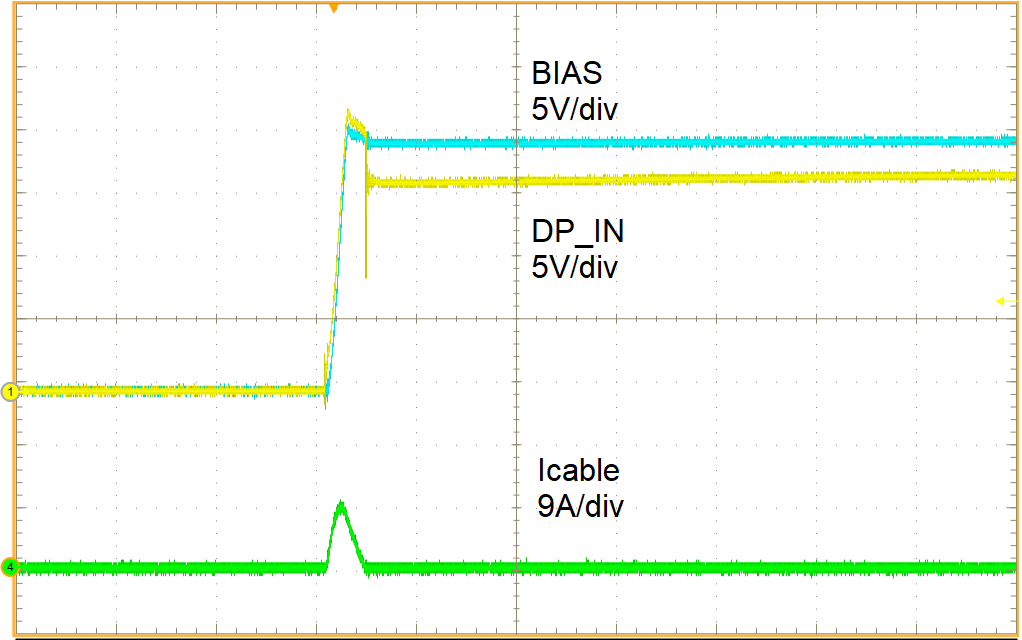

9.2.3 Application Curves

| VBAT = 16 V | t = 5 µs/div |

| t = 20 µs/div |

| t = 20 µs/div |

| RBIAS = 5.1 kΩ | t = 2 µs/div |

| R(BIAS) = 5.1 kΩ | t = 2 µs/div | R(DP_OUT) = 15 kΩ |

| VBAT = 18 V | t = 5 µs/div |

| t = 20 µs/div |

| t = 20 µs/div |

| RBIAS = 5.1 kΩ | t = 2 µs/div |