JAJSJT6A August 2020 – July 2021 TPS65994AD

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Recommended Capacitance

- 6.5 Thermal Information

- 6.6 Power Supply Characteristics

- 6.7 Power Consumption

- 6.8 PP_5V Power Switch Characteristics

- 6.9 PP_EXT Power Switch Characteristics

- 6.10 Power Path Supervisory

- 6.11 CC Cable Detection Parameters

- 6.12 CC VCONN Parameters

- 6.13 CC PHY Parameters

- 6.14 Thermal Shutdown Characteristics

- 6.15 ADC Characteristics

- 6.16 Input/Output (I/O) Characteristics

- 6.17 I2C Requirements and Characteristics

- 6.18 Typical Characteristics

- 7 Parameter Measurement Information

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 USB-PD Physical Layer

- 8.3.2 Power Management

- 8.3.3

Power Paths

- 8.3.3.1

Internal Sourcing Power Paths

- 8.3.3.1.1 PP_5Vx Current Clamping

- 8.3.3.1.2 PP_5Vx Local Overtemperature Shut Down (OTSD)

- 8.3.3.1.3 PP_5Vx Current Sense

- 8.3.3.1.4 PP_5Vx OVP

- 8.3.3.1.5 PP_5Vx UVLO

- 8.3.3.1.6 PP_5Vx Reverse Current Protection

- 8.3.3.1.7 Fast Role Swap

- 8.3.3.1.8 PP_CABLE Current Clamp

- 8.3.3.1.9 PP_CABLE Local Overtemperature Shut Down (OTSD)

- 8.3.3.1.10 PP_CABLE UVLO

- 8.3.3.2 Sink Path Control

- 8.3.3.1

Internal Sourcing Power Paths

- 8.3.4 Cable Plug and Orientation Detection

- 8.3.5 Default Behavior Configuration (ADCIN1, ADCIN2)

- 8.3.6 ADC

- 8.3.7 DisplayPort Hot-Plug Detect (HPD)

- 8.3.8 Digital Interfaces

- 8.3.9 Digital Core

- 8.3.10 I2C Interface

- 8.4 Device Functional Modes

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

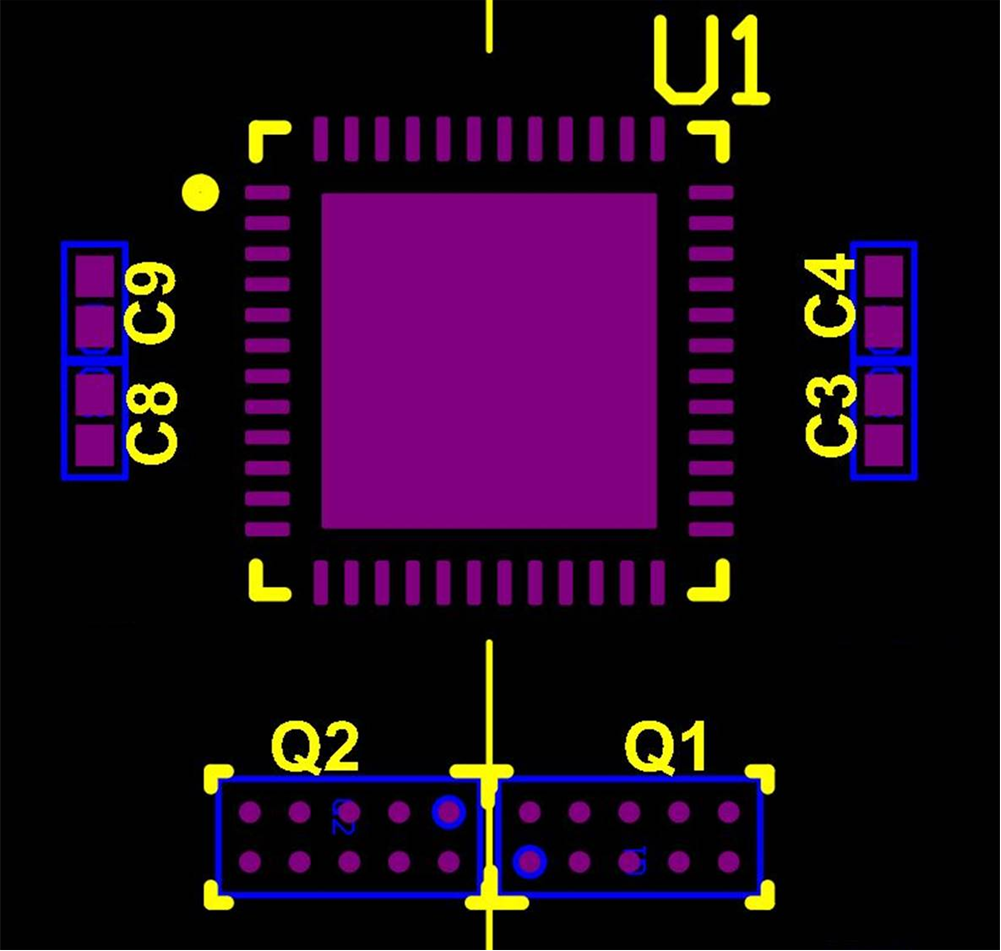

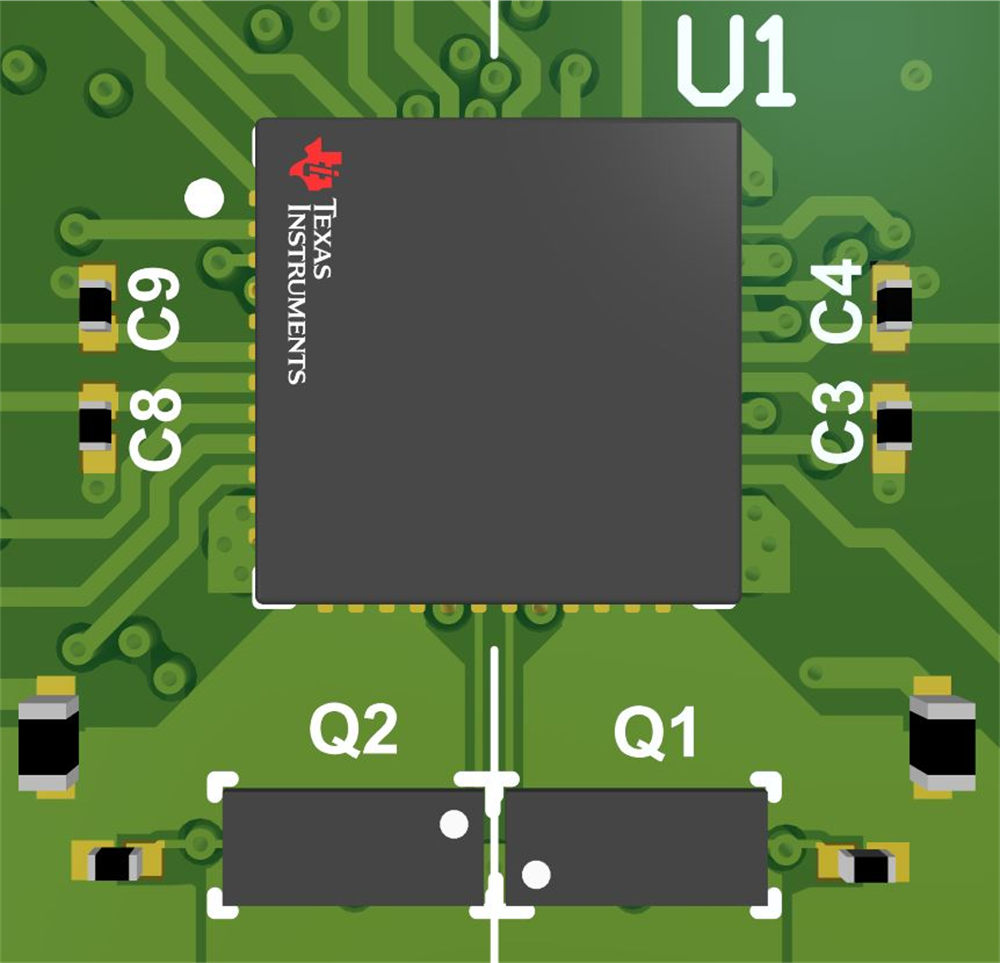

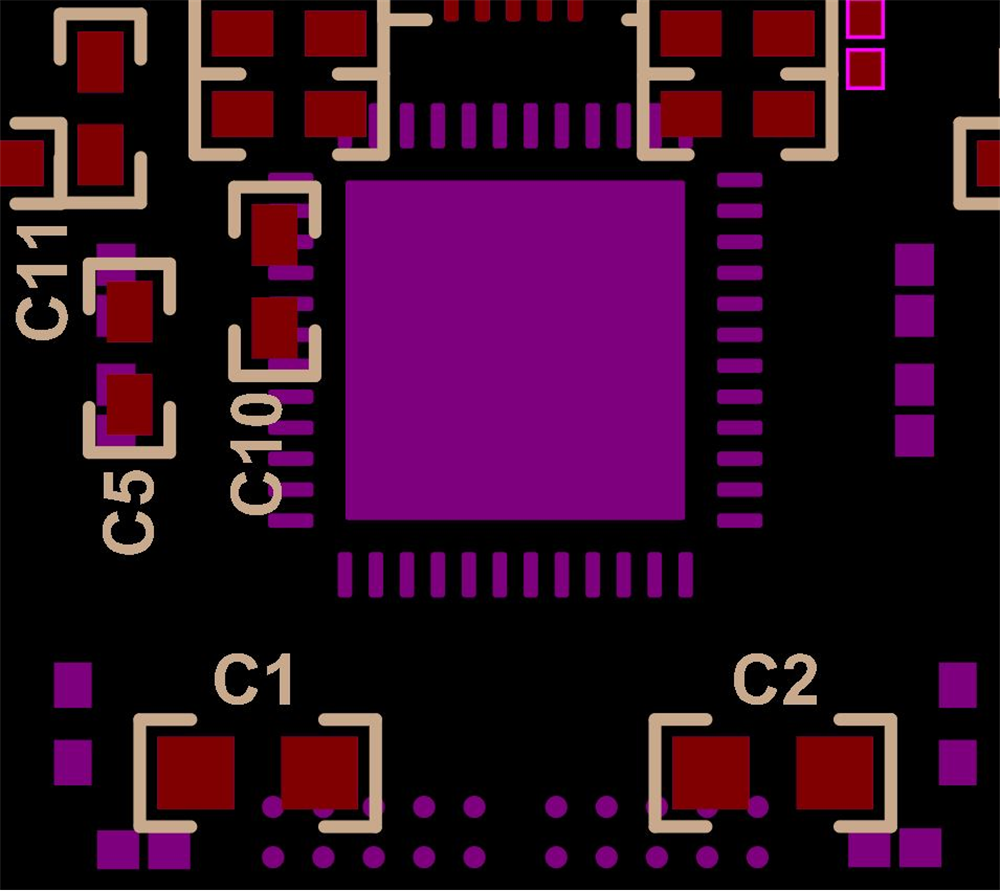

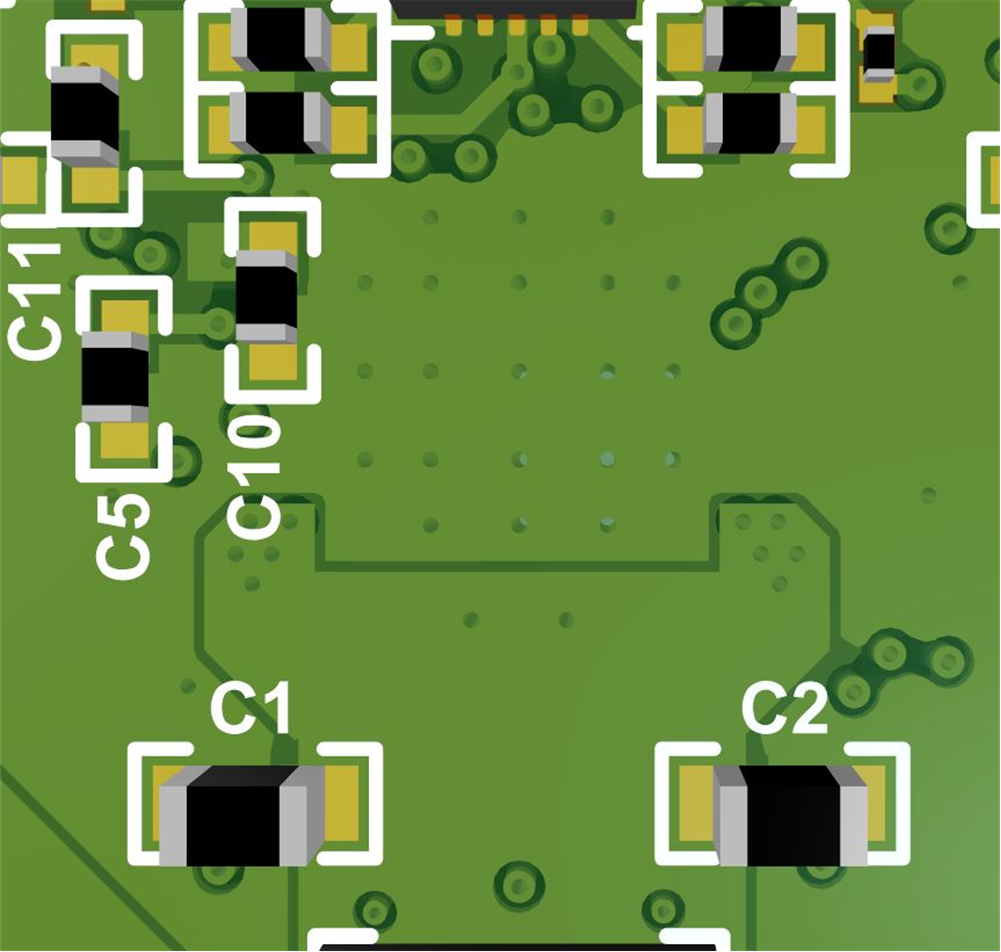

11.3 Component Placement

Top and bottom placement is used for this example to minimize solution size. The TPS65994AD is placed on the top side of the board and the majority of its components are placed on the bottom side. When placing the components on the bottom side, it is recommended that they are placed directly under the TPS65994AD. When placing the VBUS and PPHV capacitors it is easiest to place them with the GND terminal of the capacitors to face outward from the TPS65994AD or to the side since the drain connection pads on the bottom layer should not be connected to anything and left floating. All other components that are for pins on the GND pad side of the TPS65994AD should be placed where the GND terminal is underneath the GND pad.

The CC capacitors should be placed on the same side as the TPS65994AD close to the respective CC1 and CC2 pins. Do NOT via to another layer in between the CC pins to the CC capacitor, placing a via after the CC capacitor is recommended.

The ADCIN1/2 voltage divider resistors can be placed where convenient. In this layout example they are placed on the opposite layer of the TPS65994AD close to the LDO_3V3 pin to simplify routing.

The figures below show the placement in 2-D and 3-D.

Figure 11-2 Top View Layout

Figure 11-2 Top View Layout Figure 11-4 Top View 3-D

Figure 11-4 Top View 3-D Figure 11-3 Bottom View Layout

(Flipped)

Figure 11-3 Bottom View Layout

(Flipped) Figure 11-5 Bottom View 3-D

Figure 11-5 Bottom View 3-D