JAJSM66A June 2021 – December 2021 LM74701-Q1

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

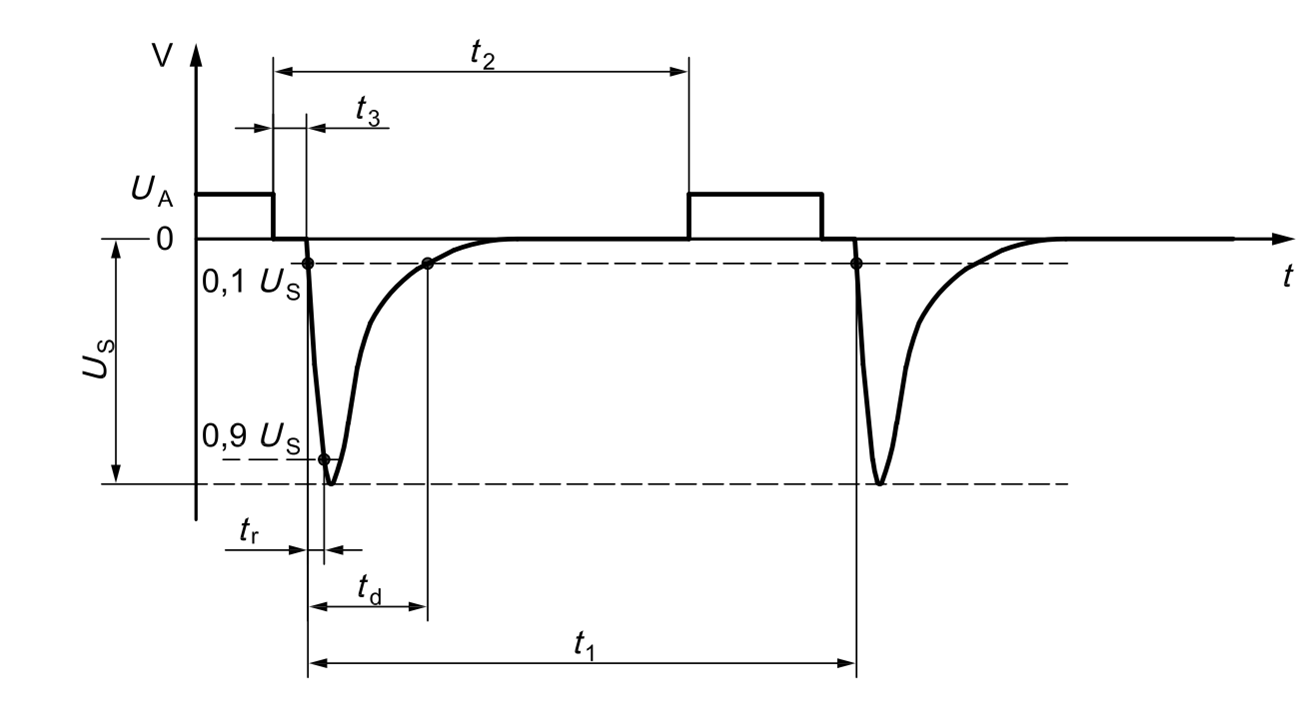

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

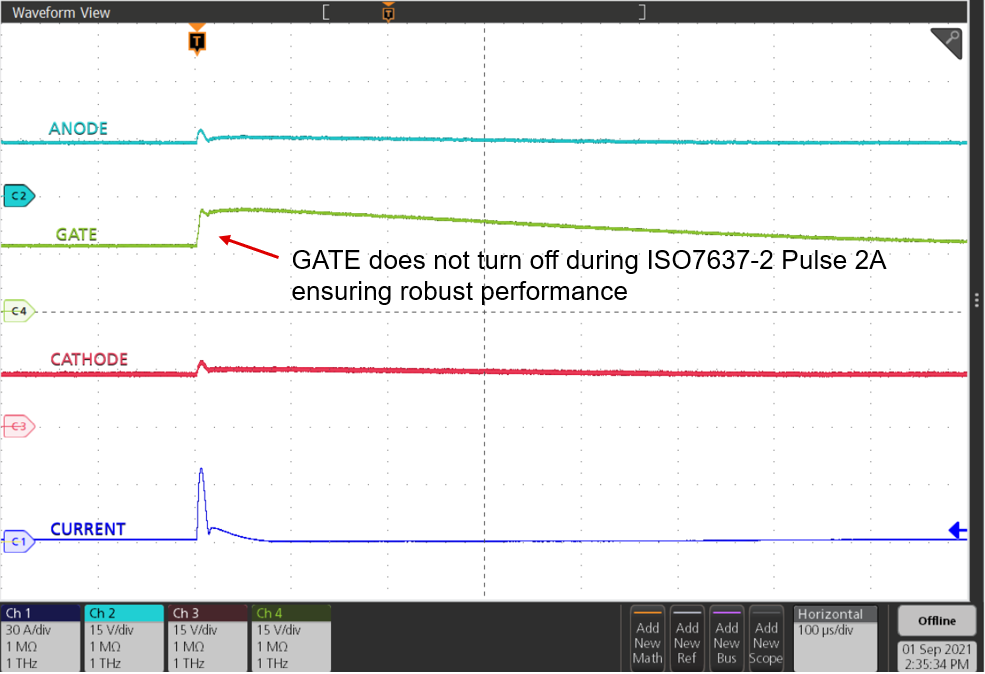

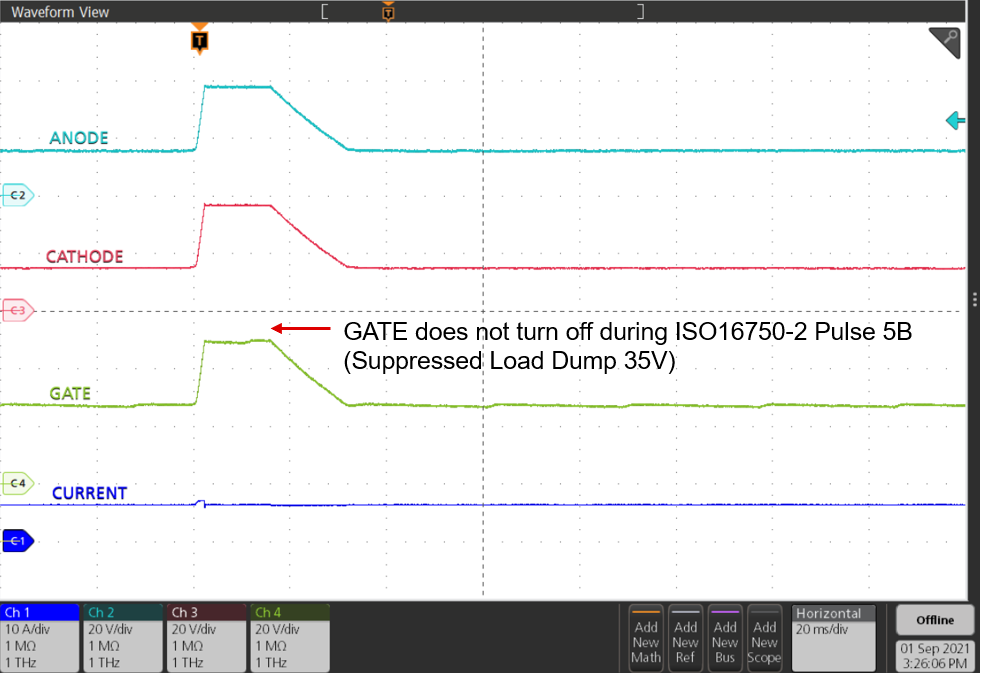

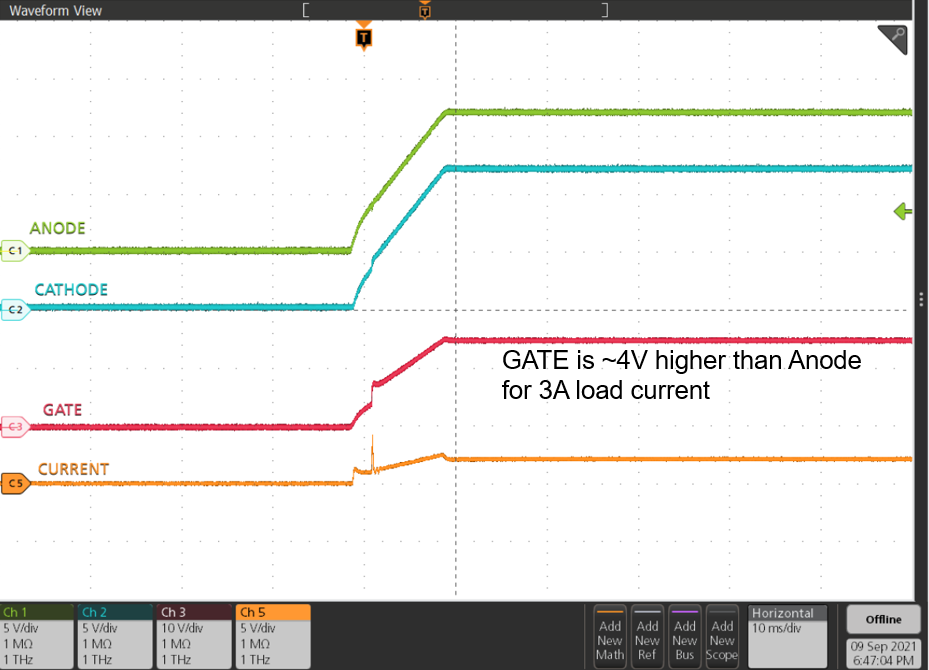

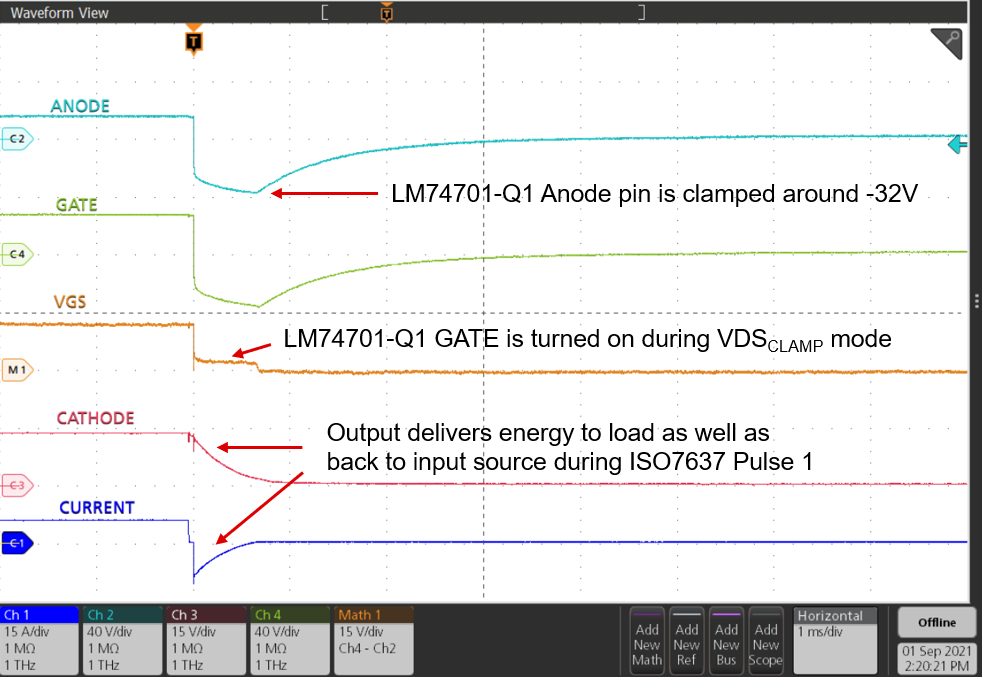

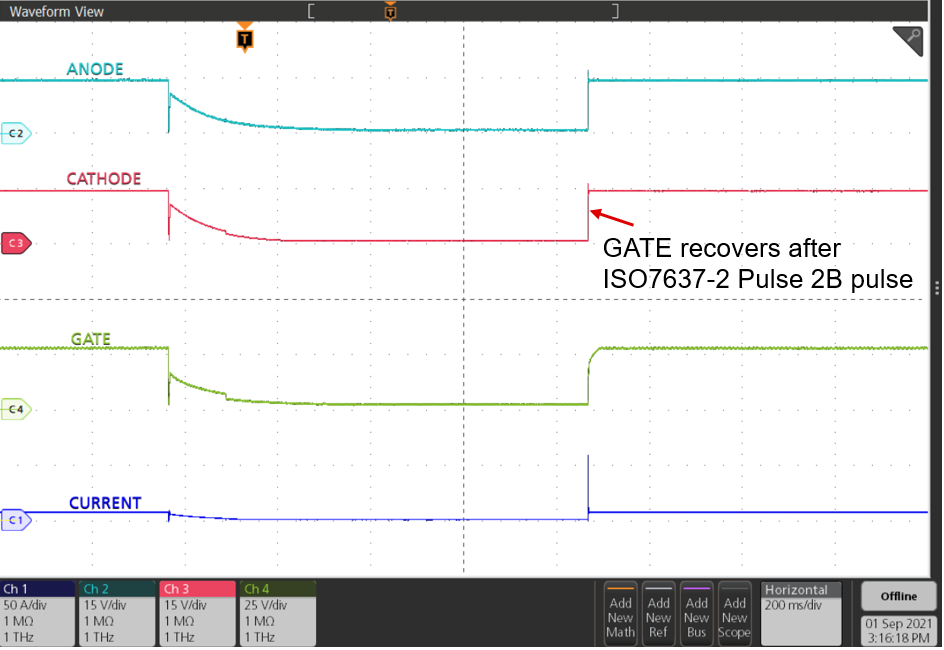

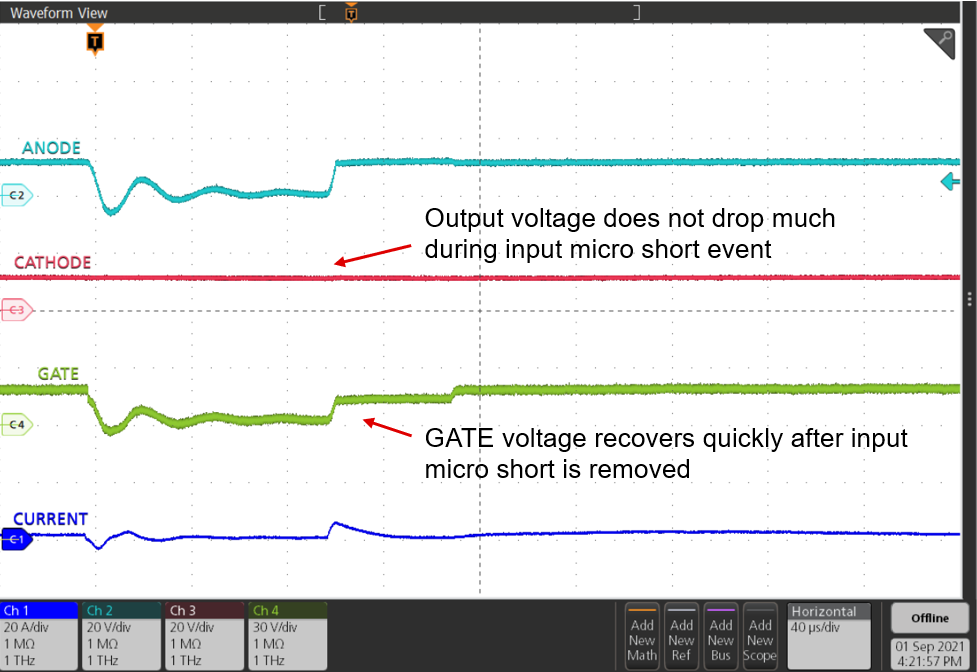

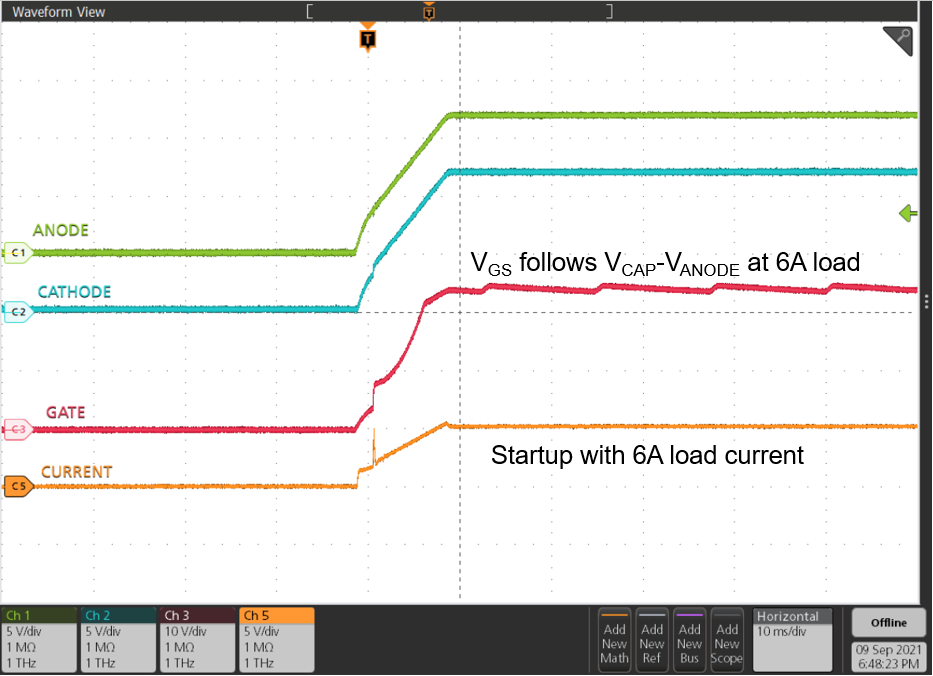

9.2.3 Application Curves

Figure 9-4 ISO 7637-2 Pulse 1

Figure 9-4 ISO 7637-2 Pulse 1

| Time (100 µs/DIV) |

| Time (20 ms/DIV) |

| Time (10 ms/DIV) |

| Time (1 ms/DIV) |

| Time (200 ms/DIV) |

| Time (40 µs/DIV) |

| Time (10 ms/DIV) |