JAJSMM0C September 2022 – June 2024 DRV8411

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 デバイスの比較

- 5 ピン構成および機能

- 6 仕様

- 7 代表的特性

- 8 詳細説明

- 9 アプリケーションと実装

- 10デバイスおよびドキュメントのサポート

- 11改訂履歴

- 12メカニカル、パッケージ、および注文情報

9.1.1.3.3 熱性能

データシートに規定する接合部から周囲への熱抵抗 RθJA は、おもに各種ドライバの比較または熱性能の概算に役立ちます。しかし、実際のシステム性能は、PCB 層構成 (スタックアップ)、配線、ビア数、サーマル・パッド周りの銅面積に応じて、この値よりも良くなったり、悪くなったりします。ドライバが特定の電流を駆動する時間の長さもまた、消費電力や熱性能に影響を与えます。ここでは、定常状態および過渡熱条件での設計方法について考察します。

このセクションのデータは、次の基準を使用してシミュレーションしたものです。

HTSSOP (PWP パッケージ)

- 2 層 PCB (サイズ 114.3 x 76.2 x 1.6mm)、標準 FR4、1oz (35µm 銅箔厚) または 2oz 銅箔厚。サーマル・ビアはサーマル・パッドの下にのみ配置 (4 x 3 アレイに 12 個のビア、1mm 間隔、0.2mm 直径、0.025mm 銅メッキ)。

- 上層:HTSSOP パッケージ・フットプリントと銅プレーン・ヒートシンク。シミュレーションでは、上層の銅領域が変化しています。

- 下層:ドライバのサーマル・パッド下のビアで熱的に接続されたグランド・プレーン。下層の銅箔面積は上層の銅箔面積によって変化します。

- 4 層 PCB (サイズ 114.3 x 76.2 x 1.6mm)、標準 FR4。外側のプレーンは 1oz (35µm 銅箔厚) または 2oz 銅箔厚。内側のプレーンは 1oz で一定。サーマル・ビアはサーマル・パッドの下にのみ配置 (4 x 3 アレイに 12 個のビア、1mm 間隔、0.2mm 直径、0.025mm 銅メッキ)。

- 上層:HTSSOP パッケージ・フットプリントと銅プレーン・ヒートシンク。シミュレーションでは、上層の銅領域が変化しています。

- 中間層 1:サーマル・パッドとビアで熱的に接続された GND プレーン。グランド・プレーンの領域は 74.2mm x 74.2mm です。

- 中間層 2:電源プレーン、熱的接続なし。電源プレーンの領域は 74.2mm x 74.2mm です。

- 下層:ドライバの下に小さな銅パッドを設け、上層および内部 GND プレーンから打ったビアで熱的に接続した信号層。下層のサーマル・パッドはパッケージと同じサイズ (5mm x 4.4mm)。上層の銅プレーンが変化しても、下層のパッドのサイズは一定。

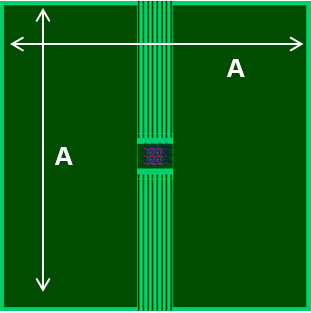

HTSSOP パッケージについてシミュレーションした基板の例を 図 9-11 に示します。表 9-3 に、各シミュレーションで変化させた基板の寸法を示します。

図 9-11 HTSSOP の PCB モデルの上層

図 9-11 HTSSOP の PCB モデルの上層表 9-3 16 ピン PWP パッケージの寸法 A

| 銅 (Cu) 面積 (cm2) | 寸法 A (mm) |

|---|---|

| 2 | 16.43 |

| 4 | 22.23 |

| 8 | 30.59 |

| 16 | 42.37 |

WQFN (RTE パッケージ)

- 2 層 PCB (サイズ 114.3 x 76.2 x 1.6mm)、標準 FR4、1oz (35µm 銅箔厚) または 2oz 銅箔厚。サーマル・ビアはパッケージのフットプリントの下にのみ配置 (5 個のビア、1mm 間隔、0.2mm 直径、0.025mm 銅メッキ)。

- 上層:WQFN パッケージのフットプリントとトレース。

- 下層:パッケージのフットプリントの下で、ビアを介して熱的に接続されるグランド・プレーン。シミュレーションでは、下層の銅箔面積を変化させています。

- 4 層 PCB (サイズ 114.3 x 76.2 x 1.6mm)、標準 FR4。外側のプレーンは 1oz (35µm 銅箔厚) または 2oz 銅箔厚。内側のプレーンは 1oz で一定。サーマル・ビアはパッケージのフットプリントの下にのみ配置 (5 個のビア、1mm 間隔、0.2mm 直径、0.025mm 銅メッキ)。

- 上層:WQFN パッケージのフットプリントとトレース。

- 中間層 1:パッケージのフットプリントの下で、ビアを介して熱的に接続される GND プレーン。グランド・プレーンの領域は 74.2mm x 74.2mm です。

- 中間層 2:電源プレーン、熱的接続なし。電源プレーンの領域は 74.2mm x 74.2mm です。

- 下層:ドライバの下に小さな銅パッドを設け、上層および内部 GND プレーンから打ったビアで熱的に接続した信号層。下層のサーマル・パッドは 1.55mm x 1.55mm。下層のサーマル・パッドは、パッケージと同じサイズ (3mm x 3mm)。下層のパッドのサイズは一定。

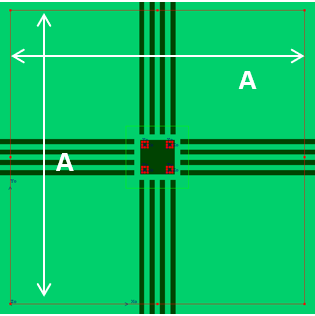

HTSSOP パッケージについてシミュレーションした基板の例を 図 9-12 に示します。表 9-4 に、各シミュレーションで変化させた基板の寸法を示します。

図 9-12 WQFN の PCB モデルの上層

図 9-12 WQFN の PCB モデルの上層表 9-4 16 ピン RTE パッケージの寸法 A

| 銅 (Cu) 面積 (cm2) | 寸法 A (mm) |

|---|---|

| 2 | 14.14 |

| 4 | 20.00 |

| 8 | 28.28 |

| 16 | 40.00 |