-

TPS74801-Q1 プログラマブル ソフトスタート機能付き、車載用 1.5A 低ドロップアウト リニア レギュレータ

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Detailed Description

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

- 重要なお知らせ

TPS74801-Q1 プログラマブル ソフトスタート機能付き、車載用 1.5A 低ドロップアウト リニア レギュレータ

このリソースの元の言語は英語です。 翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

1 特長

- 車載アプリケーション用に AEC-Q100 認定済み:

- 温度グレード 1:-40℃~+125℃、TA

- VOUT 範囲:0.8V~3.6V

- 非常に低い VIN 範囲:0.8V~5.5V

- VBIAS 範囲:2.7V~5.5V

- 低いドロップアウト:60mV (標準値)、1.5A、VBIAS = 5V

- パワー グッド (PG) 出力により、電源電圧の監視や、他の電源のためのシーケンシング信号の供給が可能

- ライン、負荷、温度の全範囲にわたって 2% の精度

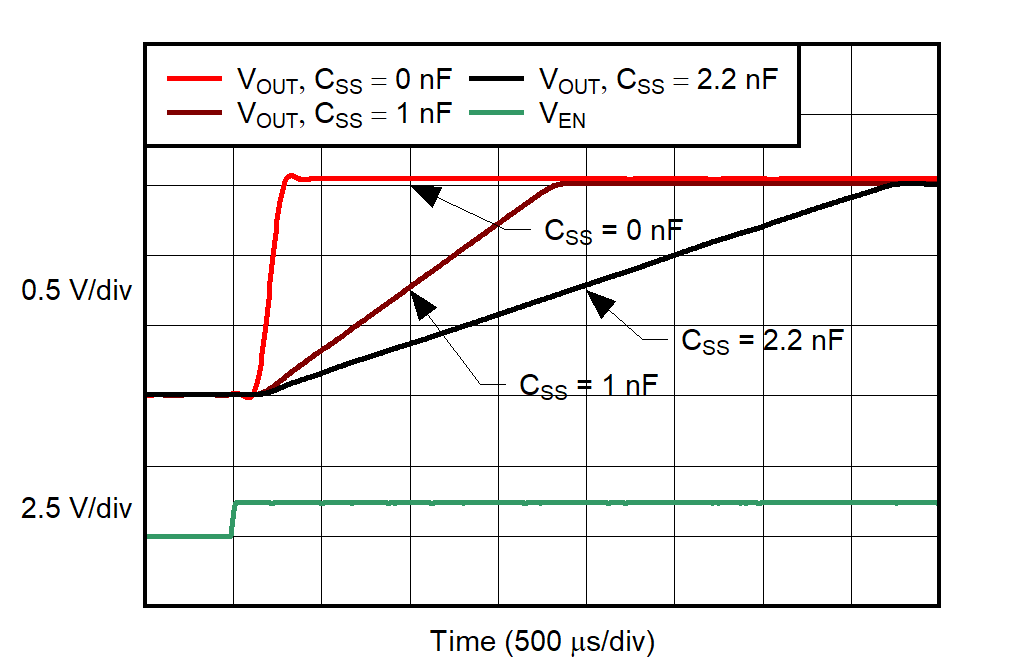

- プログラム可能なソフトスタートにより、直線的に電圧が立ち上がるようにスタートアップさせることが可能

- VBIAS により、過渡応答性に優れた低 VIN 動作を実現

- 2.2μF 以上の出力コンデンサで安定動作

- 小型の 3mm × 3mm × 1mm VSON-10 および 5mm × 5mm VQFN-20 パッケージで供給

3 概要

TPS74801-Q1 低ドロップアウト (LDO) リニア レギュレータは、広範なアプリケーション向けの使いやすく堅牢な電力管理ソリューションです。ソフトスタートをユーザーがプログラムできるので、スタートアップ時の容量性突入電流を低減して、入力電源のストレスを最小限に抑えることができます。ソフトスタートは単調性で、多くの種類のプロセッサや ASIC の電源供給向けに設計されています。イネーブル入力とパワー グッド出力により、外部レギュレータとの間でシーケンシングを簡単に行えます。この優れた柔軟性により、FPGA、DSP、および特殊なスタートアップ要件を持つ他のアプリケーションのシーケンス要件を満たすソリューションを構成できます。

高精度の基準電圧およびエラー アンプは、負荷、ライン、温度、プロセスの全体にわたって 2% の精度を維持します。このデバイスは 2.2μF 以上の任意のタイプの出力コンデンサで安定して動作し、新しいチップでは TJ = -40℃~+150℃、DRC パッケージでは TJ = -40℃~+105℃、RGW パッケージでは TJ = -40℃~+125℃で完全に動作が規定されています。TPS74801-Q1 は 3mm × 3mm の小型 VSON-10 パッケージで供給され、ソリューションの総合的な小型化に役立ちます。このデバイスは、5mm × 5mm の VQFN-20 パッケージでも供給されます。

代表的なアプリケーション回路 (可変)

代表的なアプリケーション回路 (可変) ターンオン応答

ターンオン応答4 Pin Configuration and Functions

Figure 4-1 DRC Package,10-Pin VSON With Exposed Thermal Pad(Top View)

Figure 4-1 DRC Package,10-Pin VSON With Exposed Thermal Pad(Top View) Figure 4-2 RGW Package,20-Pin VQFN With Exposed Thermal Pad(Top View)

Figure 4-2 RGW Package,20-Pin VQFN With Exposed Thermal Pad(Top View)| PIN | TYPE | DESCRIPTION | ||

|---|---|---|---|---|

| NAME | NO. | |||

| DRC (VSON) | RGW (VQFN) | |||

| BIAS | 4 | 10 | I | Bias input voltage for error amplifier, reference, and internal control circuits. |

| EN | 5 | 11 | I | Enable pin. Driving this pin high enables the regulator. Driving this pin low puts the regulator into shutdown mode. This pin must not be left unconnected. |

| FB | 8 | 16 | I | Feedback pin. The feedback connection to the center tap of an external resistor divider network that sets the output voltage. This pin must not be left floating. |

| GND | 6 | 12 | — | Ground |

| IN | 1, 2 | 5-8 | I | Input to the device. |

| NC | N/A | 2-4, 13, 14, 17 | — | No connection. This pin can be left floating or connected to GND to allow better thermal contact to the top-side plane. |

| OUT | 9, 10 | 1, 18-20 | O | Regulated output voltage. A small capacitor (total typical capacitance ≥ 2.2 μF, ceramic) is needed from this pin to ground to provide stability. |

| PG | 3 | 9 | O | Power-good pin. An open-drain, active-high output that indicates the status of VOUT. When VOUT exceeds the PG trip threshold, the PG pin goes into a high-impedance state. When VOUT is below this threshold the pin is driven to a low-impedance state. Connect a pullup resistor from 10 kΩ to 1 MΩ from this pin to a supply of up to 5.5 V. The supply can be higher than the input voltage. Alternatively, the PG pin can be left unconnected if output monitoring is not necessary. |

| SS | 7 | 15 | — | Soft-start pin. A capacitor connected on this pin to ground sets the start-up time. If this pin is left unconnected, the regulator output soft-start ramp time is typically 200 μs. |

| Thermal Pad | — | Solder the thermal pad to the ground plane for increased thermal performance. | ||